A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

*

This signal has a weak internal pull up

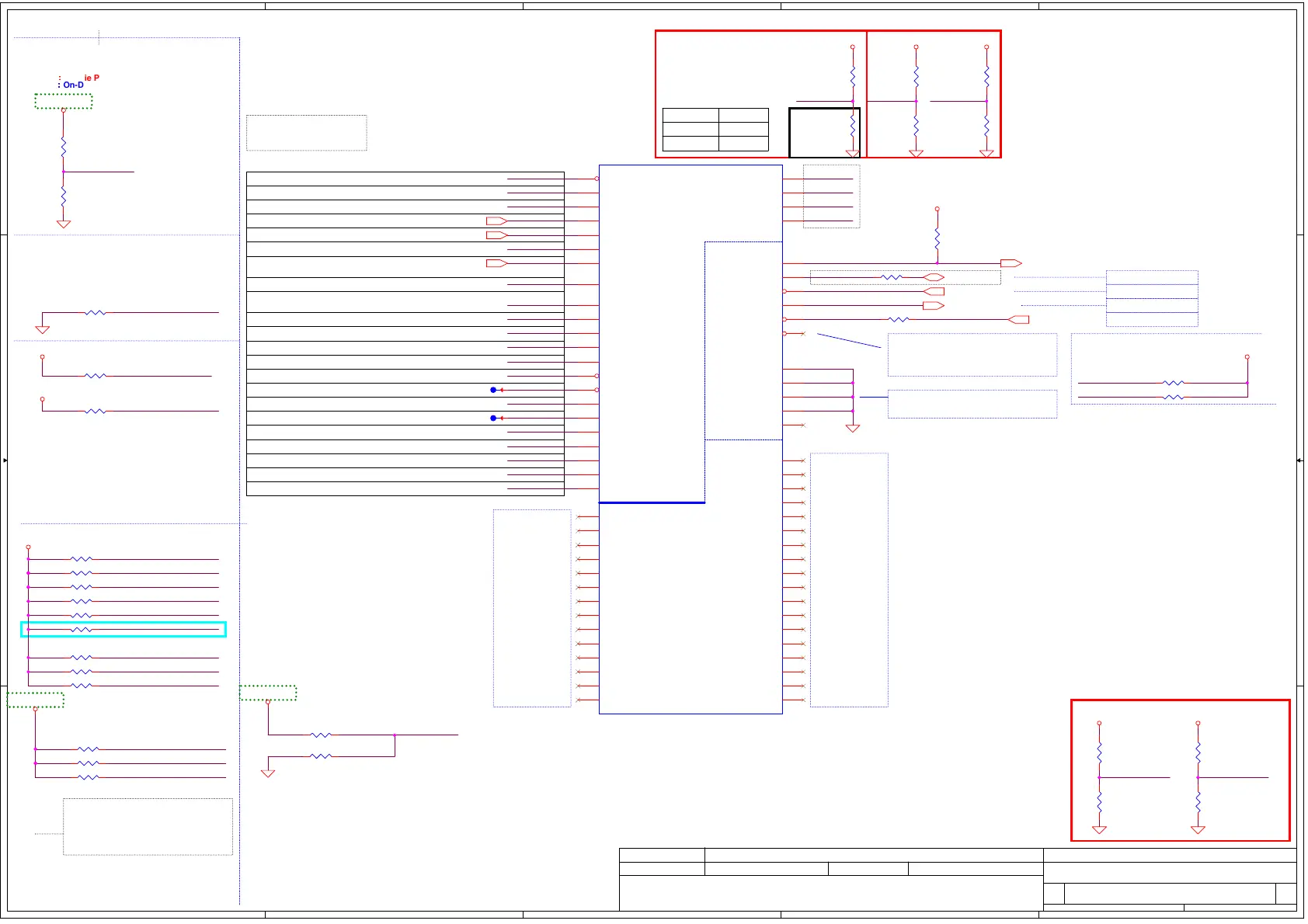

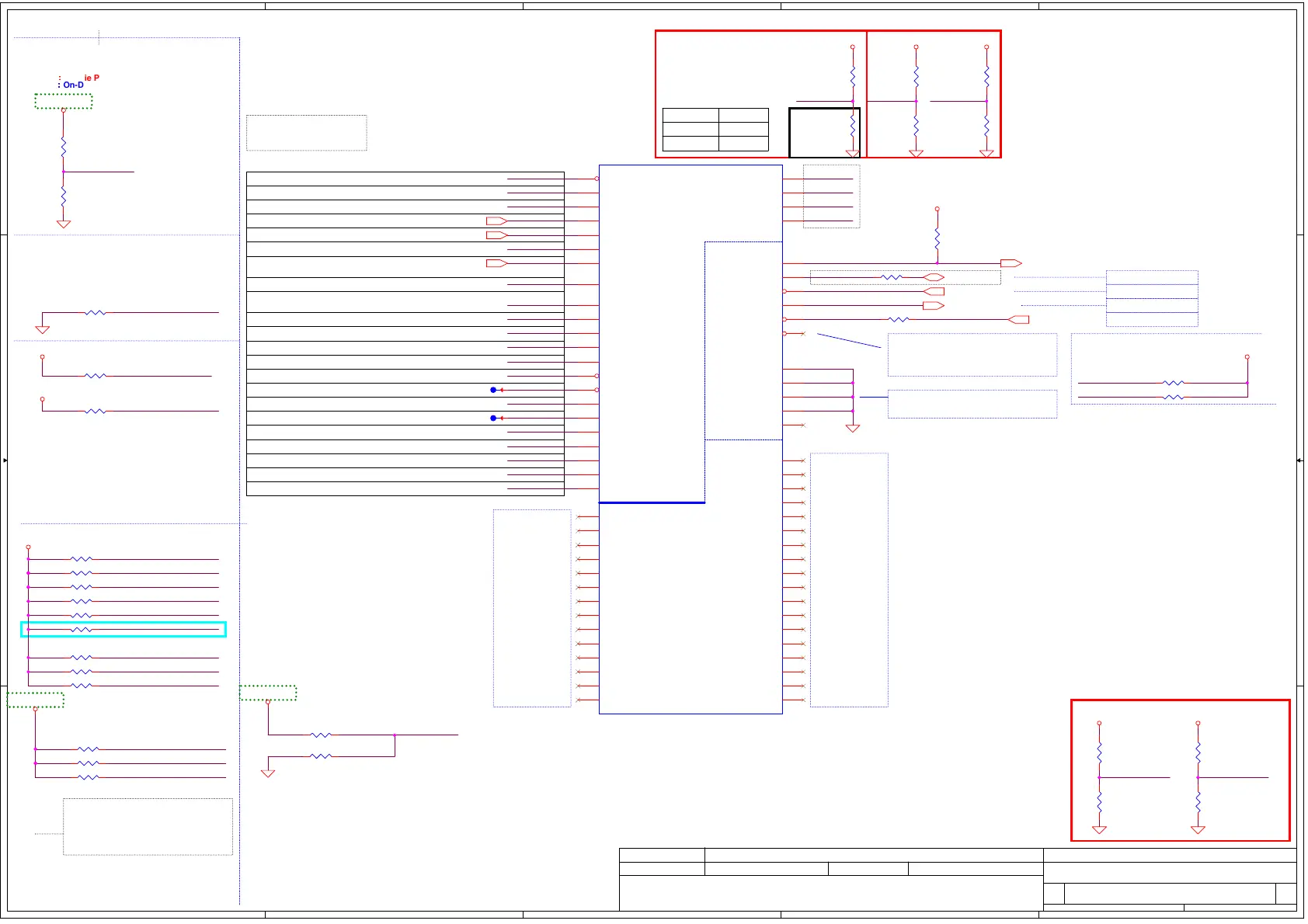

On-Die PLL Voltage Regulator

L

:

::

:

On-Die PLL Voltage Regulator disable

GPIO28

H

:

::

:

On-Die PLL voltage regulator enable

INIT3_3V

Th

is signal has weak internal

PU, can't pull low,leave NC

PCH_GPIO27 (Have internal Pull-High)

Deep S4,S5 wake event signal

TS_VSS1~4

PD to GND

PECI CPU-EC

Checklist1.5 P.69

CTRL+ALT+DEL

non CPU power ok

130c shut down

HDA_SYNC PH(PLL =+1.5VS)

Deep S4,S5 wake event signal

RTC alarm,Power BTN,GPIO27

No use can NC

No use PU 10K +3VS

No use PU 10K +3VALW

No use PD 10K to GND

No use PU 10K +3VS

Can't PU

Can't PU

No use PU 10K +3VS

SATA5GP&TEMP_ALERT# CRB PU 10K +3VS

No use PU +3VS

No use PU +3VALW

Fan Tachometer Inputs

TACH1~7 only on server

can insted to GPIO

No use PU 10K +3VS

No use PU 10K +3VS

No use PU 10K +3VS

No use PU 10K +3VS

No use PU 10K +3VS

BT ON/OFF

SATA2GP/GPIO36 & SATA3GP/GPIO37

Sampled at Rising edge of PWROK.

Weak internal pull-down.

(weak internal pull-down is disabled

after PLTRST# de-asserts)

NOTE: This signal should NOT be

pulled high when strap is sampled

GPIO36/GPIO37 is Strap functionality

tha

t requires internal pull down to be sampled at rising PWROK.

When uses as SATA2GP/SATA3GP for mechanical presence detect

-use a external pull up 150K-200K ohm to Vcc3_3

When used as GP input

-ensure GPI is not driven high during strap sampling window

When Unused as GPIO or SATA*GP

-use 8.2K-10K pull-down

check list page 47

CRB1.0 PU 10K to +3VALW

GPIO24 Unmultiplexed

NOTE: GPIO24 configuration

register bits are not cleared by

CF9h reset event.

No use PU 10K +3VS

No use PU 10K +3VALW

No use PU +3VALW

No use PU +3VS

RAM flag

DDR

3/DDR3LNo use PU +3VALW

RAM flag

No use PU +3VALW

9/15 Layout

request remove

Test point

They will route

by itself

9/15 Layout

request remove

Test point

They will route

by itself

GPIO71

0

1

eD

P

LVDS

LVDS/eDP

11/21 EDP@->POP

12/13 Add

Debug Port DG 1.2 PU 4.7K +3VALW_PCH

PCH_THRMTRIP#_R

EC_SCI#

PCH_GPIO39

PCH_GPIO49

PCH_GPIO28

PCH_GPIO34

PCH_PECI_R

PCH_GPIO71

EC_KBRST#

H_THRMTRIP#

EC_SMI#

PCH_GPIO17

PCH_GPIO6

PCH_GPIO1

PCH_GPIO37

PCH_GPIO38

PCH_GPIO27

PCH_GPIO35

PCH_GPIO57

PCH_GPIO48

PCH_GPIO24

PCH_GPIO22

EC_LID_OUT#

PCH_GPIO12

PCH_GPIO27

PCH_GPIO1

PCH_GPIO6

PCH_GPIO34

PCH_GPIO48

PCH_GPIO17

PCH_GPIO49

PCH_GPIO36

PCH_GPIO16

PCH_GPIO69

PCH_GPIO70

PCH_GPIO68

PCH_GPIO16

PCH_GPIO0

PCH_GPIO0

PCH_GPIO71 PCH_GPIO69 PCH_GPIO70

EC_KBRST#

PCH_GPIO36

PCH_GPIO24

PCH_GPIO68

PCH_GPIO39 PCH_GPIO22

EC_SMI#

PCH_GPIO38

PCH_GPIO28

PCH_GPIO57

EC_LID_OUT#

PCH_GPIO12

+3VS

+3VS

+3VS +3VS +3VS

+3VS+3VS

+3VS +3VS

+3VALW_PCH

+VCCSUS3_3

+VCCSUS3_3

+VCCSUS3_3

EC_SCI#<29>

EC_SMI#<29>

EC_LID_OUT#<29> GATEA20 <29>

H_CPUPWRGD <5>

H_THRMTRIP# <5>

EC_KBRST# <29>

H_PECI <5,29>

Title

Siz

e Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1.0

PCH (6/9) GPIO, CPU, MISC

Custom

18 45Friday, April 20, 2012

2011/11/22 2012/11/22

Compal Electronics, Inc.

Q1VZC M/B LA-8941P Schematic

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1.0

PCH (6/9) GPIO, CPU, MISC

Custom

18 45Friday, April 20, 2012

2011/11/22 2012/11/22

Compal Electronics, Inc.

Q1VZC M/B LA-8941P Schematic

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1.0

PCH (6/9) GPIO, CPU, MISC

Custom

18 45Friday, April 20, 2012

2011/11/22 2012/11/22

Compal Electronics, Inc.

Q1VZC M/B LA-8941P Schematic

R205

1K_0402_5%

@

1 2

R204

10K_0402_5%

1 2

R235

10K_0402_5%

@

12

R201

10K_0402_5%

EDP@

1 2

R209 10K_0402_5%@

1 2

T21PAD @

R2070_0402_5%

@

1 2

R212 10K_0402_5%

1 2

R229

10K_0402_5%

12

R213 10K_0402_5%

1 2

R225 10K_0402_5%

1 2

R232 10K_0402_5%

1 2

R231

10K_0402_5%

12

R210 390_0402_5%

1 2

R522 10K_0402_5%

1 2

R228 1K_0402_5%

1 2

R221 10K_0402_5%

1 2

T20PAD @

R200

10K_0402_5%@

12

R227 10K_0402_5%

1 2

R226 10K_0402_5%@

1 2

R214 1K_0402_5%@

1 2

R199

10K_0402_5%

@

12

R233

10K_0402_5%

@

12

R216 10K_0402_5%

1 2

R222 10K_0402_5%

1 2

R211 200K_0402_5%

12

R206

10K_0402_5%

1 2

R203

10K_0402_5%

1 2

R223 10K_0402_5%

1 2

R198

10K_0402_5%

LVDS@

12

R219 10K_0402_5%

1 2

R218 10K_0402_5%

1 2

R224 10K_0402_5%

1 2

R202

4.7K_0402_5%

12

R220 10K_0402_5%

1 2

CPU/MISC

NCTF

GPIO

U16F

COUGARPOINT_FCBGA989

HM77@

GPIO27

E16

GPIO28

P8

GPIO24 / MEM_LED

E8

GPIO57

D6

LAN_PHY_PWR_CTRL / GPIO12

C4

VSS_NCTF_1

A4

VSS_NCTF_2

A44

VSS_NCTF_3

A45

VSS_NCTF_4

A46

VSS_NCTF_5

A5

VSS_NCTF_6

A6

VSS_NCTF_7

B3

VSS_NCTF_8

B47

VSS_NCTF_9

BD1

VSS_NCTF_10

BD49

VSS_NCTF_11

BE1

VSS_NCTF_12

BE49

TACH2 / GPIO6

H36

TACH0 / GPIO17

D40

TACH3 / GPIO7

E38

SATA3GP / GPIO37

M5

SATA5GP / GPIO49

V3

SCLOCK / GPIO22

T5

SLOAD / GPIO38

N2

SDATAOUT0 / GPIO39

M3

SDATAOUT1 / GPIO48

V13

PROCPWRGD

AY11

RCIN#

P5

PECI

AU16

THRMTRIP#

AY10

GPIO8

C10

BMBUSY# / GPIO0

T7

GPIO15

G2

TACH1 / GPIO1

A42

SATA2GP / GPIO36

V8

INIT3_3V#

T14

STP_PCI# / GPIO34

K1

GPIO35

K4

SATA4GP / GPIO16

U2

VSS_NCTF_32

F49

A20GATE

P4

TACH4 / GPIO68

C40

TACH6 / GPIO70

C41

TACH7 / GPIO71

A40

TACH5 / GPIO69

B41

VSS_NCTF_17

BH3

VSS_NCTF_18

BH47

VSS_NCTF_19

BJ4

VSS_NCTF_20

BJ44

VSS_NCTF_21

BJ45

VSS_NCTF_22

BJ46

VSS_NCTF_23

BJ5

VSS_NCTF_24

BJ6

VSS_NCTF_25

C2

VSS_NCTF_26

C48

VSS_NCTF_27

D1

VSS_NCTF_28

D49

VSS_NCTF_29

E1

VSS_NCTF_30

E49

VSS_NCTF_31

F1

NC_4

AK10

NC_3

AH10

NC_2

AK11

NC_1

AH8

NC_5

P37

VSS_NCTF_13

BF1

VSS_NCTF_14

BF49

VSS_NCTF_15

BG2

VSS_NCTF_16

BG48

Loading...

Loading...