5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Note:

0

Note:

01

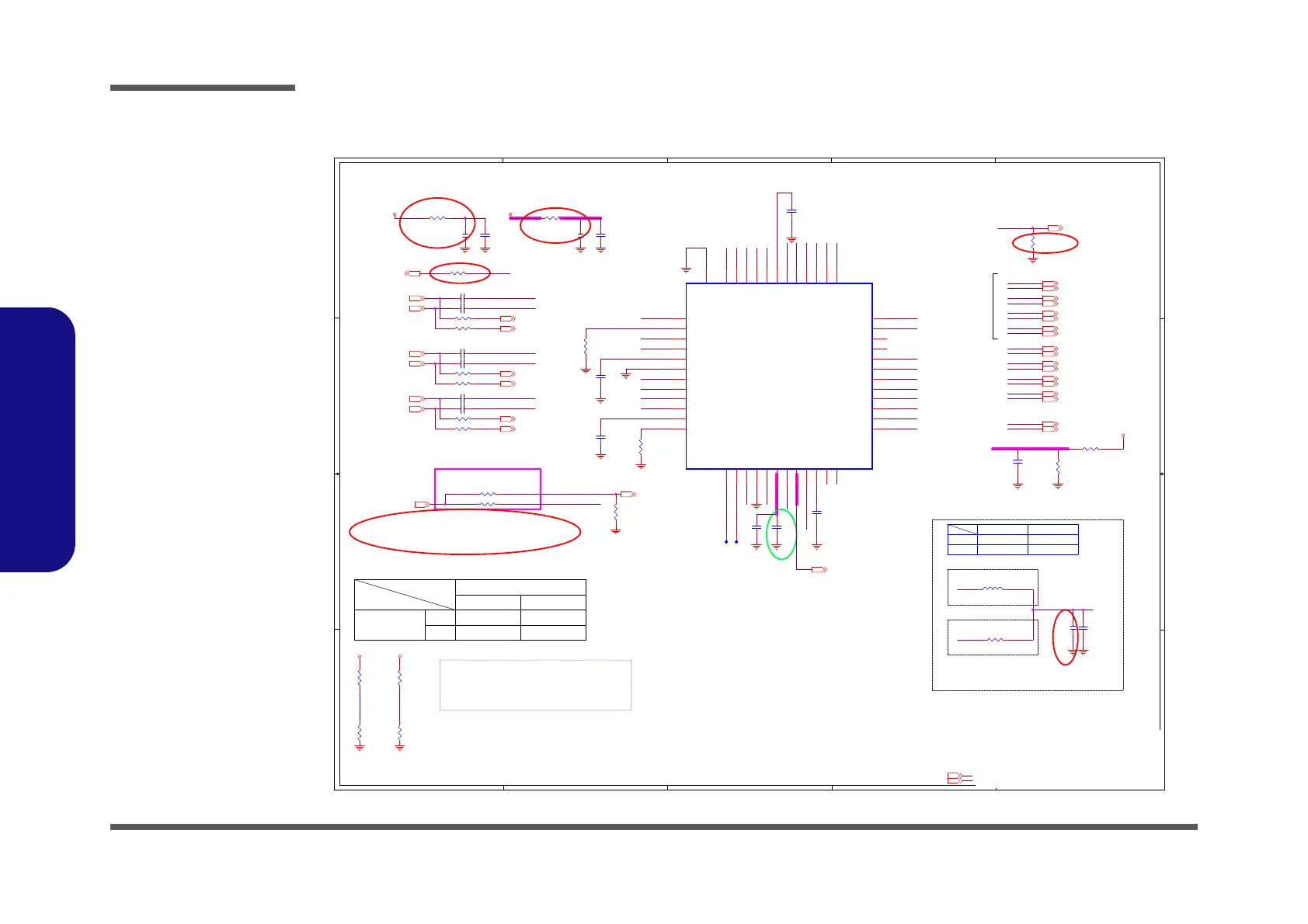

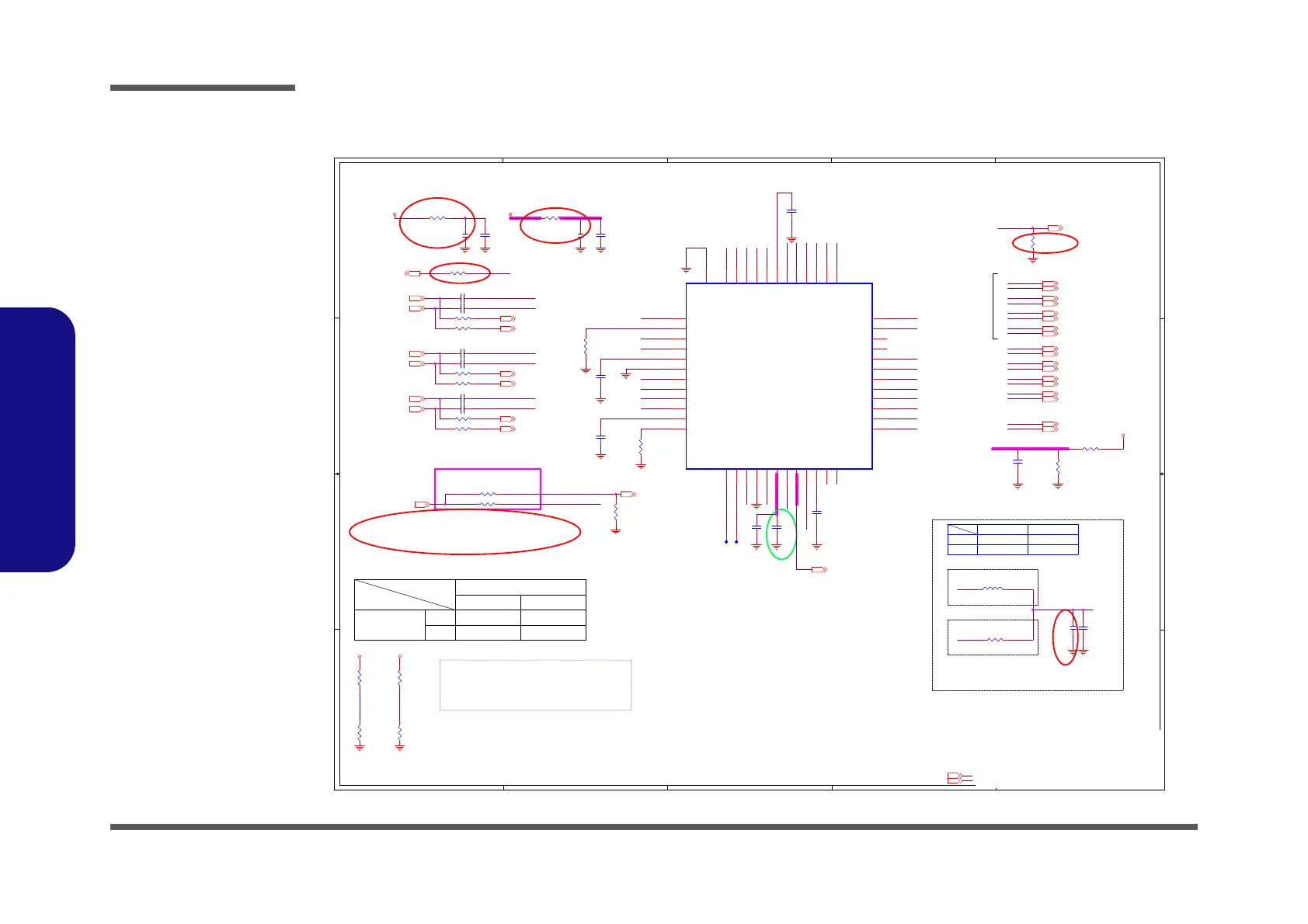

MODE_CFG0(PIN47)

Dual Mode Regulator Configuration

SWR MODE

MODE_CFG1(PIN48)

Power

1

1. Entire trace of Panel VCC should be wider than 80-mil

: PIN47 4.7K pull low, PIN48 4.7K pull high

: PIN47 4.7K pull high, PIN48 4.7K pull low

: PIN47 4.7K pull high, PIN48 4.7K pull high

LDO MODE

Mode Configure Table(Power On Latch)

EEPROM MODE

RTD2136 Supports three operation mode for system design.

6-03-02136-031

ROM ONLY Mode

ROM ONLY MODE

EP Mode

Connect

NC

NC

Connect

SWR

LDO

2.2-uH(L) 0 Olm(R)

EEPROM Mode

Reserved 4.7K resistor pull up/low for mode selection

EP MODE

1. Cap should be closed to chip

6-19-41001-019

X

1.C308, C312 Capacitors should be closed to PIN17

To LVDS Connector

Single link

LVD S

PIN47 PIN48

ἧ䓐

eDP

㗪

,BRIGHTNESS

䚜㍍

㍍⇘

ED P CONNECTO R

CapCap Cap

1A

20140929

20140929

20141211 BCN

20140929

20140929

20140929

1016

BRIGHTNESS_EC_PS

DVCC33

LVDS-U0N

LVDS-U0P

LVDS-U1N

LVDS-U1P

DP_REXT

HPD

TEST_MODE

DAUXn

DAUXp

DRX1p

DRX1n

DRX0p

DRX0n

AVCC33

VCCK_V12

PIN17

PANEL_PW M

DVCC33

VCCK_V12

DVCC33

MODE_CFG1

MODE_CFG0

P_DDC_CLK

P_DDC_DATA

ENBLT

MODE_CFG0

VCCK_V12

AVCC33

VCCK_V12

PIN17

MODE_CFG1

PANEL_PWM

PIN17

LVDS-U2N

LVDS-U2P

LVDS-UCLKP

BRIGHTNESS_EC_PS

LVDS-UCLKN

SMC_EDP_CLK

HPD

SMD_EDO_DAT

LVDS-L0PLVDS-L0P

DAUXn

DAUXp

DRX0p

DRX0n

DRX1p

DRX1n

LVDS-L1N

LVDS-L1P

LVDS-L2N

LVDS-L2P

LVDS-LCLKN

LVDS-LCLKP

LVDS-L0N

LVDS-L0P

LVDS-U1N

LVDS-U1P

LVDS-U2N

LVDS-U2P

LVDS-UCLKN

LVDS-UCLKP

LVDS-U0N

LVDS-U0P

P_DDC_CLK

P_DDC_DATA

LVDS-L0N

LVDS-LCLKP

LVDS-LCLKN

LVDS-L1N

LVDS-L1P

VCCK_V12

LVDS-L2P

LVDS-L2N

ENBLT

LVDS_PLVDD_EN

3.3VS 3.3VS

3.3VS 3.3VS

PLVDD

EDP_AUXP[6]

EDP_TXN_0[6]

EDP_TXN_1[6]

EDP_TXP_1[6]

EDP_TXP_0[6]

EDP_AUXN[6]

EDP_HPD[6,12]

LVDS-LCLKP [12]

LVDS-U2P [12]

LVDS-LCLKN [12]

LVDS-U2N [12]

LVDS-L2P [12]

LVDS-U1P [12]

LVDS-L2N [12]

LVDS-U1N [12]

LVDS-L0P [12]

LVDS-L1P [12]

LVDS-L0N [12]

LVDS-L1N [12]

LVDS-UCLKP [12]

LVDS-U0P [12]

LVDS-UCLKN [12]

LVDS-U0N [12]

ENBLT [12]

PANEL_PW M [12]

P_DDC_DATA [12]

P_DDC_CLK [12]

3.3VS[3,6,9,10,12,13,22,23,24,25,26,28,29,30,31,32,34,35,36,37,38,39,42,44]

DP_AUX# [12]

DP_AUX [12]

DP_TXP0 [12]

DP_TXN0 [12]

DP_TXP1 [12]

DP_TXN1 [12]

L_BRIGHTNESS_R[25]

LVDS_PLVDD_EN [12]

PLVDD[12]

Title

Size Document Number R e v

Date: Sheet

of

6-71-N1500-D02A

2.0A

[11] RTD2136(EDP TO LVDS)

Custom

11 55Tuesday, December 16, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number R e v

Date: Sheet

of

6-71-N1500-D02A

2.0A

[11] RTD2136(EDP TO LVDS)

Custom

11 55Tuesday, December 16, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number R e v

Date: Sheet

of

6-71-N1500-D02A

2.0A

[11] RTD2136(EDP TO LVDS)

Custom

11 55Tuesday, December 16, 2014

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

R122 0_04

R402 *0_04

RTD2136N

U8

RTD2136N-CG

DP_HPD

1

TEST_MODE

2

AUX_CH_N

3

AUX_CH_P

4

DP_V33

5

DP_GND

6

LANE0_P

7

LANE0_N

8

LANE1_P

9

LANE1_N

10

DP_V12

11

DP_REXT

12

CIICSCL

13

CIICSDA

14

SWR_VCCK/LDO_VCCK

15

GND

16

SWR_LX/LDO_FB

17

SWR_VDD/LDO_VDD

18

PWMOUT

19

PANEL_VCC

20

PWMIN

21

PVCC

22

TXE3+

23

TXE3-

24

TXOC-

36

TXOC+

35

TXO3-

34

TXO3+

33

TXE0-

32

TXE0+

31

TXE1-

30

TXE1+

29

TXE2-

28

TXE2+

27

TXEC-

26

TXEC+

25

MODE_CFG1

48

MODE_CFG0

47

MIICSCL

46

MIICSDA

45

BL_EN

44

VCCK

43

TXO0-

42

TXO0+

41

TXO1-

40

TXO1+

39

TXO2-

38

TXO2+

37

EPAD_GND

49

C316

0.1u_10V_X7R_04

C293 0.1u_10V_X7R_04

R137

*4.7K_04

C331

2.2u_6.3V_X5R_06

R133

4.7K_04

C279

0.1u_10V_X7R_04

R129

*4.7K_04

R410 *0_04

R147

*1K_04

C305

0.1u_10V_X7R_04

R121

100K_04

C294 0.1u_10V_X7R_04

C326

0.1u_10V_X7R_04

C286

2.2u_6.3V_X5R_06

R132

12K_1%_04

R145

10K_04

C308

2.2u_6.3V_X5R_06

R403 *0_04

C333

4.7u_25V_X5R_08

R142 0_04

R140 0_06

R406 *0_04

C291 0.1u_10V_X7R_04

R143

10K_04

C292 0.1u_10V_X7R_04

C312

0.1u_10V_X7R_04

R144 *0_04

C323

*4.7u_6.3V_X5R_06

R211 0_06

C325

0.1u_10V_X7R_04

C290 0.1u_10V_X7R_04

R412 *0_04

R214 0_06

R153*0_06

C289 0.1u_10V_X7R_04

L16

*BCNR3010C-2R2M

1 2

C280

0.1u_10V_X7R_04

R408 *0_04

R135

4.7K_04

C341

0.1u_10V_X7R_04

Loading...

Loading...