Programming

Bit Name Comment

CW.3 Reserved - -

CW.2 IR

(InitRequest)

1

bin

The controller requests

terminal for initialization.

The send and receive

functions are blocked, the

FIFO indicators are reset,

and the interface is again

initialized with the value.

The interface

acknowledges completion

of the initialization via bit

SW.2 (IA).

0

bin

The controller once again

requests the interface to

prepare for serial data

exchange.

CW.1 RA

(ReceiveAccepted)

toggle The controller

acknowledges receipt of

data by changing the state

of this bit. Only then new

data can be transferred

from the interface to the

controller.

CW.0 TR

(TransmitRequest)

toggle Via a change of state of

this bit the controller

notifies the interface that

the DataOut bytes contain

the number of bytes

indicated via the OL bits.

The interface

acknowledges receipt of

the data in the status byte

via a change of state of

word SW.0 (TA). Only

now new data can be

transferred from the

controller to the interface.

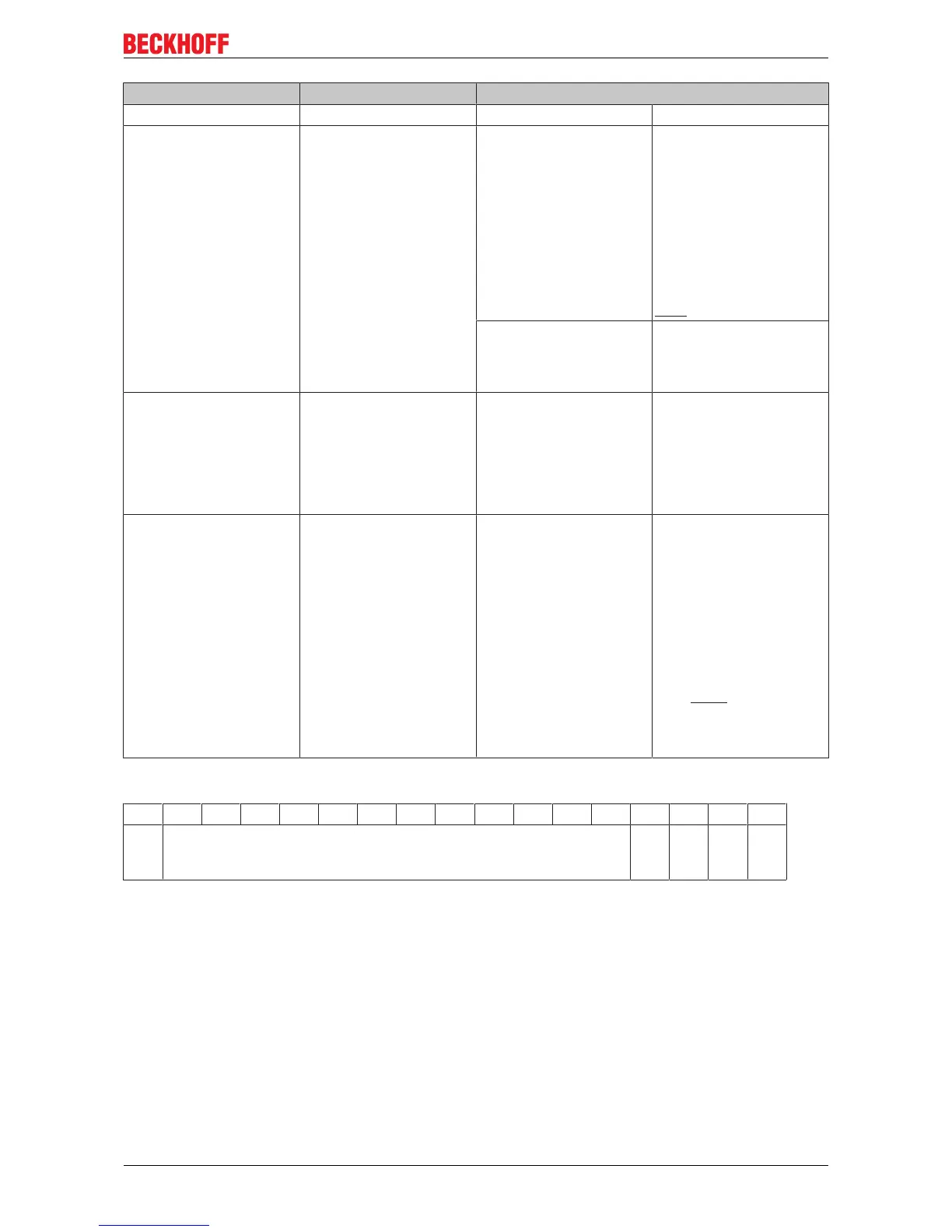

Table2: Status word

Bit 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Nam

e

Length of data in the buffer ((IL bits) BUF

_F

IA RR TA

Legend

CX8080 43Version: 1.0.0

Loading...

Loading...