1. IC's

SEMICONDUCTORS

STM32F101ZE (DIGITAL : IC711)

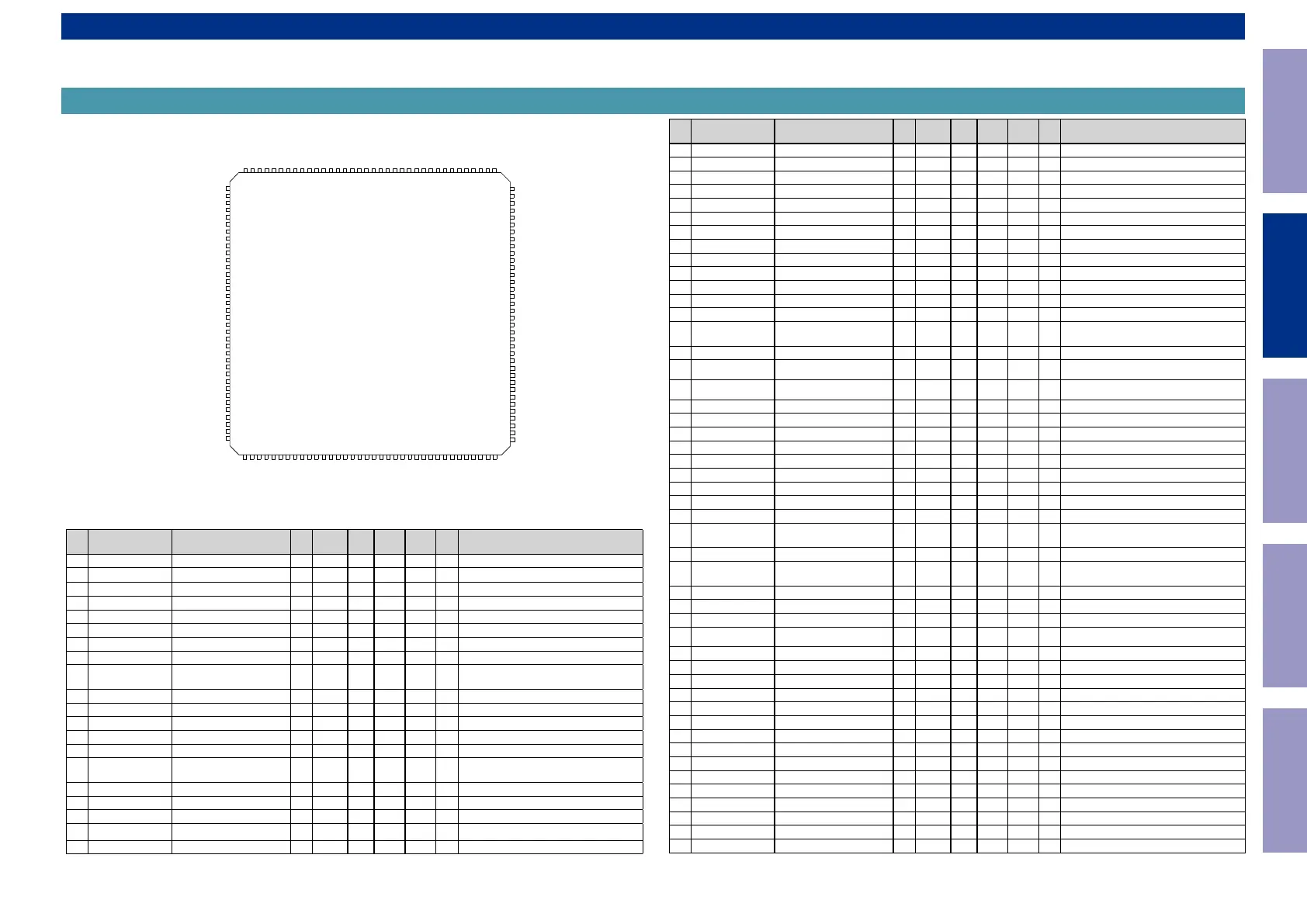

STM32F101ZG Terminal Functions

Pin Pin Name Symbol

I/O Pullup STBY

Pass-

Trough

BT

STBY

stop

Function

1 PE2 DC_PROTECT

I M3VPu I I I I

DC Protection Detect

2 PE3 USB_DAC_MUTE

O - O/L O/L O/L O/L

USB_DAC_MUTE control

3 PE4 POWER_DOWN

I M3VPu I I I I

Power Down detect

4 PE5 FRONT_RLY(SPK_RLY_ON)

O - O/L O/L O/L O/L

Front SPK RLY control

5 PE6 C/S_RLY

O - O/L O/L O/L O/L

Surround/Center SPK RLY control

6 VBAT VBAT

- - - - - -

3.3V

7 PC13 MIC_DET

I Pd I I I I

MIC detect

8 PC14 / OSC32_IN OSC32_IN

- - - - - -

9

PC15 / OSC32_

OUT

OSC32_OUT

- - - - 0 -

10 PF0 ISEL_B

I Pu I I I I

FUNCTION ENDORDER input(A)

11 PF1 ISEL_A

I Pu I I I I

FUNCTION ENDORDER input(B)

12 PF2 HI-B_RLY

O - O/L O/L O/L O/L

HI-B_RLY control

13 PF3 CVBS_SW2

O - O/L O/L O/L O/L

CVBS(Video)SW2 control

14 PF4 CVBS_SW5

O - O/L O/L O/L O/L

CVBS(Video)SW5 control

15 PF5 CP_SDA

O - O/L O/L O/L O/L

APPLE AUTH CHIP_I2C_SDA (for AVR-

X250BT option)

16 VSS_5

- - - - - -

GND

17 VDD_5

- - - - - -

3.3V

18 PF6 CEC_POWER2

O - L H L O/L

CEC_POWER2 control

19 PF7 USB_EN

O - O/L O/L O/L O/L

USB_CURRENT IC control

20 PF8 HPD3

O - O/L O/L O/L O/L

HDMI INPUT3 HOT PLUG control

STM32F101xC, STM32F101xD, STM32F101xE Pinouts and pin descriptions

Doc ID 14610 Rev 8 23/112

3 Pinouts and pin descriptions

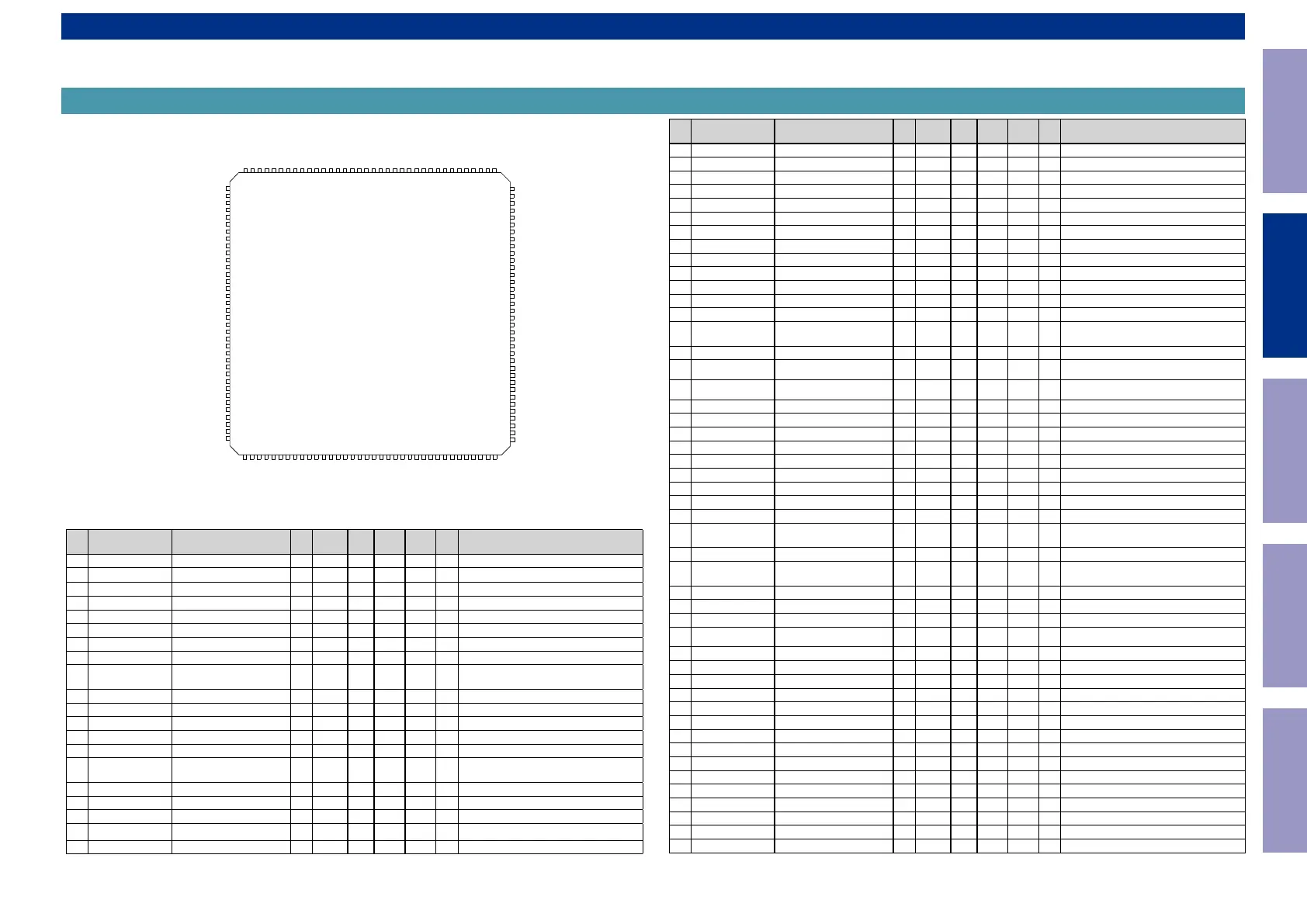

Figure 3. STM32F101xC, STM32F101xD and STM32F101xE access line LQFP144 pinout

V

DD_3

V

SS_3

PE1

PE0

PB9

PB8

BOOT0

PB7

PB6

PB5

PB4

PB3

PG15

V

DD_11

V

SS_11

PG14

PG13

PG12

PG11

PG10

PG9

PD7

PD6

V

DD_10

V

SS_10

PD5

PD4

PD3

PD2

PD1

PD0

PC12

PC11

PC10

PA15

PA14

PE2

V

DD_2

PE3

V

SS_2

PE4

NC

PE5

PA13

PE6

PA12

VBAT

PA11

PA10

PC14-OSC32_IN

PA9

PC15-OSC32_OUT

PA8

PF0

PC9

PF1

PC8

PF2

PC7

PF3

PC6

PF4

V

DD_9

PF5

V

SS_9

V

SS_5

PG8

V

DD_5

PG7

PF6

PG6

PF7

PG5

PF8

PG4

PF9

PG3

PF10

PG2

OSC_IN

PD15

OSC_OUT

PD14

NRST

V

DD_8

PC0

V

SS_8

PC1

PD13

PC2

PD12

PC3

PD11

V

SSA

PD10

V

REF-

PD9

V

REF+

PD8

V

DDA

PB15

PA0-WKUP

PB14

PA1

PB13

PA2

PB12

PA3

V

SS_4

V

DD_4

PA4

PA5

PA6

PA7

PC4

PC5

PB0

PB1

PB2

PF11

PF12

VSS_6

V

DD_6

PF13

PF14

PF15

PG0

PG1

PE7

PE8

PE9

V

SS_7

V

DD_7

PE10

PE11

PE12

PE13

PE14

PE15

PB10

PB11

V

SS_1

V

DD_1

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

109

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

72

LQFP144

120

119

118

117

116

115

114

113

112

111

110

61

62

63

64

65

66

67

68

69

70

71

26

27

28

29

30

31

32

33

34

35

36

83

82

81

80

79

78

77

76

75

74

73

Pin Pin Name Symbol

I/O Pullup STBY

Pass-

Trough

BT

STBY

stop

Function

21 PF9 MAIN_VOL_DATA

O - O/L O/L O/L O/L

Volume Data

22 PF10 MAIN_VOL_CLK

O - O/L O/L O/L O/L

Volume CLK

23 PH0 / OSC_IN XTAL_IN

I - - - - -

XTAL_IN(8MHz)

24 PH1 / OSC_OUT XTAL_OUT

O - - - - -

XTAL_OUT(8MHz)

25 NRST RESET

I - - - - -

RESET

26 PC0 KEY1

I M3VPu I I I I

KEY1

27 PC1 KEY2

I M3VPu I I I I

KEY2

28 PC2 KEY3

I M3VPu I I I I

KEY3

29 PC3 OPTION

I M3VPu I I I I

MODEL OPTION

30 VSSA

- - - - - -

GND

31 VREF-

- - - - - -

GND

32 VREF+

- - - - - -

3.3V

33 VDDA

- - - - - -

3.3V

34 PA0 / WKUP CP_SCL

O - O/L O/L O/L O/L

APPLE AUTH CHIP_I2C_SCL (for AVR-

X250BT option)

35 PA1 USB_RESET

O - O/L O/L O/L O/L

BX8804(USB DECORDER) RESET

36 PA2 USB_RX

O

USB-

3V3Pu

O/L O/L O/L O/L

BX8804(USB DECORDER) RX

37 PA3 USB_TX

I

USB-

3V3Pu

I I I I

BX8804(USB DECORDER) TX

38 VSS_4

- - - - - -

GND

39 VDD_4

- - - - - -

3.3V

40 PA4 DSP_CS

O - O/L O/L O/L O/L

DSP Chip Select

41 PA5 DSP_CLK

O D3VPu O/L O/L O/L O/L

DSP_CLK

42 PA6 DSP_MISO

I D3VPu I I I I

DSP MISO

43 PA7 DSP_MOSI

O - O/L O/L O/L O/L

DSP MOSI

44 PC4 HPD4

O - O/L O/L O/L O/L

HDMI INPUT4 HOT PLUG control

45 PC5 HPD5

O - O/L O/L O/L O/L

HDMI INPUT5 HOT PLUG control

46 PB0 DIR_MISO

I - I I I I

DIR_MISO

47 PB1 DIR_CLK

O - O/L O/L O/L O/L

DIR_CLK(separated from AVR1312 DSP_

CLK)

48 PB2 / BOOT1 BOOT1

I - - - - -

GND

49 PF11 DIR_MOSI

O - O/L O/L O/L O/L

DIR MOSI(separated from AVR1312 DSP_

MOSI)

50 PF12 DSP_RST

O - O/L O/L O/L O/L

DSP Reset control

51 VSS_6

- - - - - -

GND

52 VDD_6

- - - - - -

3.3V

53 PF13 DSP_MODE_SEL

I/O

Pull-

Down

O/L O/L O/L O/L

DSP_MODE_SEL

54 PF14 CODEC_MUTE

I(FT) - O/L O/L O/L O/L

CODEC Mute Detect (*FT = 5V tolerant)

55 PF15 DIR_RST

O - O/L O/L O/L O/L

DIR Reset

56 PG0 DIR_CE

O - O/L O/L O/L O/L

DIR Chip Select

57 PG1 DSP_SPC1_IRQ

I D3VPu I I I I

DSP INTERRRUPTQ

58 PE7 DSP_PCP_BSY

I D3VPu I I I I

DSP BSY

59 PE8 CEC_POWER

O - L H L O/L

CEC_POWER TIMING control

60 PE9 HDMI_SW

O - O/L O/L O/L O/L

HDMI Audio Data MCLK Select SW

61 VSS_7

- - - - - -

GND

62 VDD_7

- - - - - -

3.3V

63 PE10 DV5_POWER

O - O/L H H O/L

DV5_POWER TIMING control

64 PE11 HDMI_SPI_MISO

I - I I I I

HDMI OSD DATA input

65 PE12 HDMI_SPI_MOSI

O - O/L O/L O/L O/L

HDMI OSD DATA output

66 PE13 HDMI_SPI_CS

O +3VHPu O/L O/L O/L O/L

HDMI OSD Chip Select

67 PE14 HDMI_SPI_CLK

O - O/L O/L O/L O/L

HDMI OSD Clock

68 PE15 HDMI_SPI_HOLD

O - O/L O/L O/L O/L

HDMI OSD HOLD

Only major semiconductors are shown, general semiconductors etc. are omitted to list.

The semiconductor which described a detailed drawing in a schematic diagram are omitted to list.

Before Servicing

This Unit

Electrical Mechanical Repair Information Updating

34

Loading...

Loading...