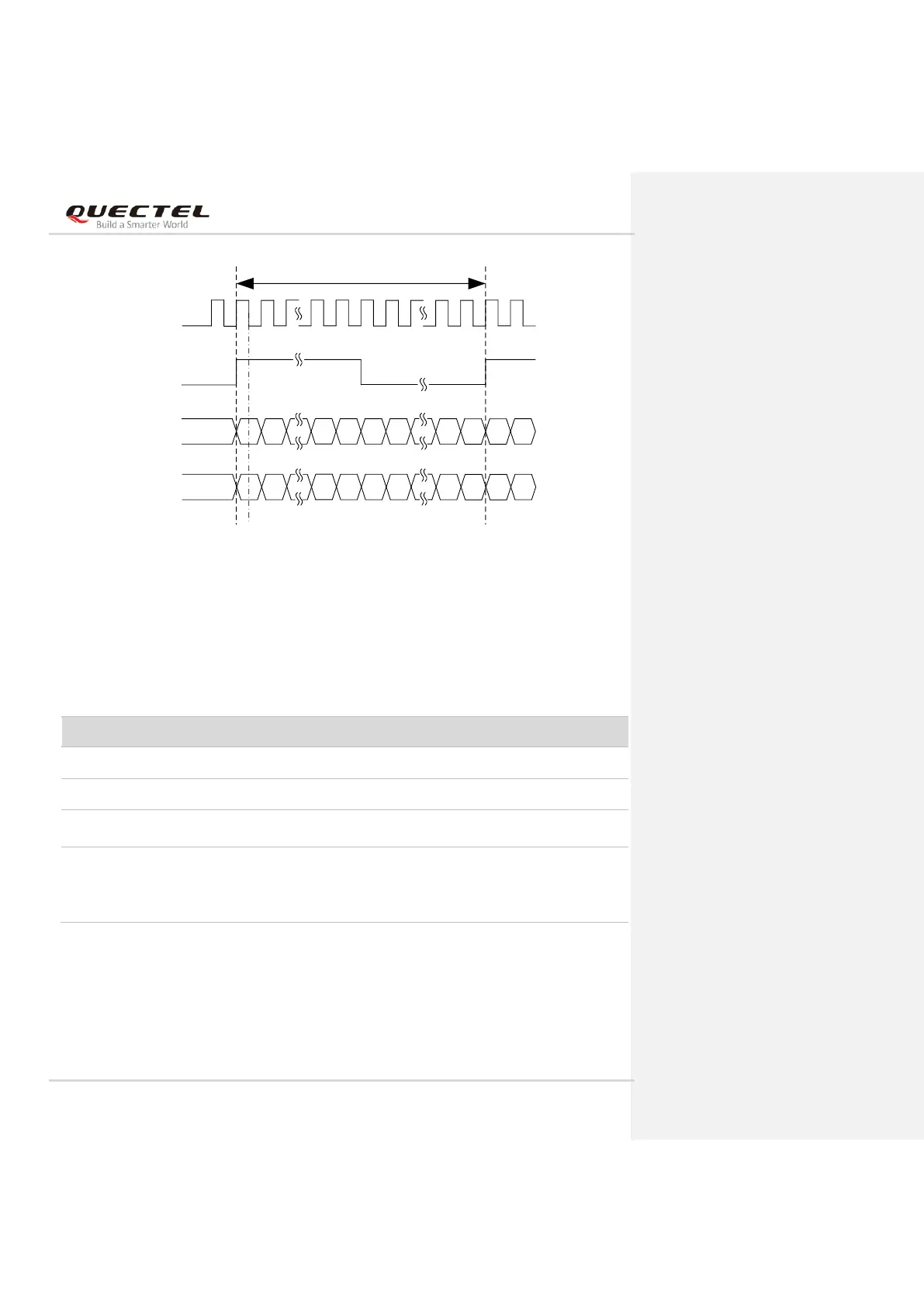

Figure 26: Auxiliary Mode Timing

The following table shows the pin definition of PCM interface which can be applied on audio codec

design.

Table 14: Pin Definition of PCM Interface

The clock and mode can be configured by AT command, and the default configuration is master mode

using short frame synchronization format with 2048 kHz PCM_CLK and 8 kHz PCM_SYNC. Refer to

document [3] for details about AT+QDAI command.

Loading...

Loading...