Load Instructions

47

S7-400 Instruction List

A5E00267845-01

Load Instructions

Loading address identifiers into ACCU1. The contents of ACCU1 are first saved to ACCU2. The status word is not affected.

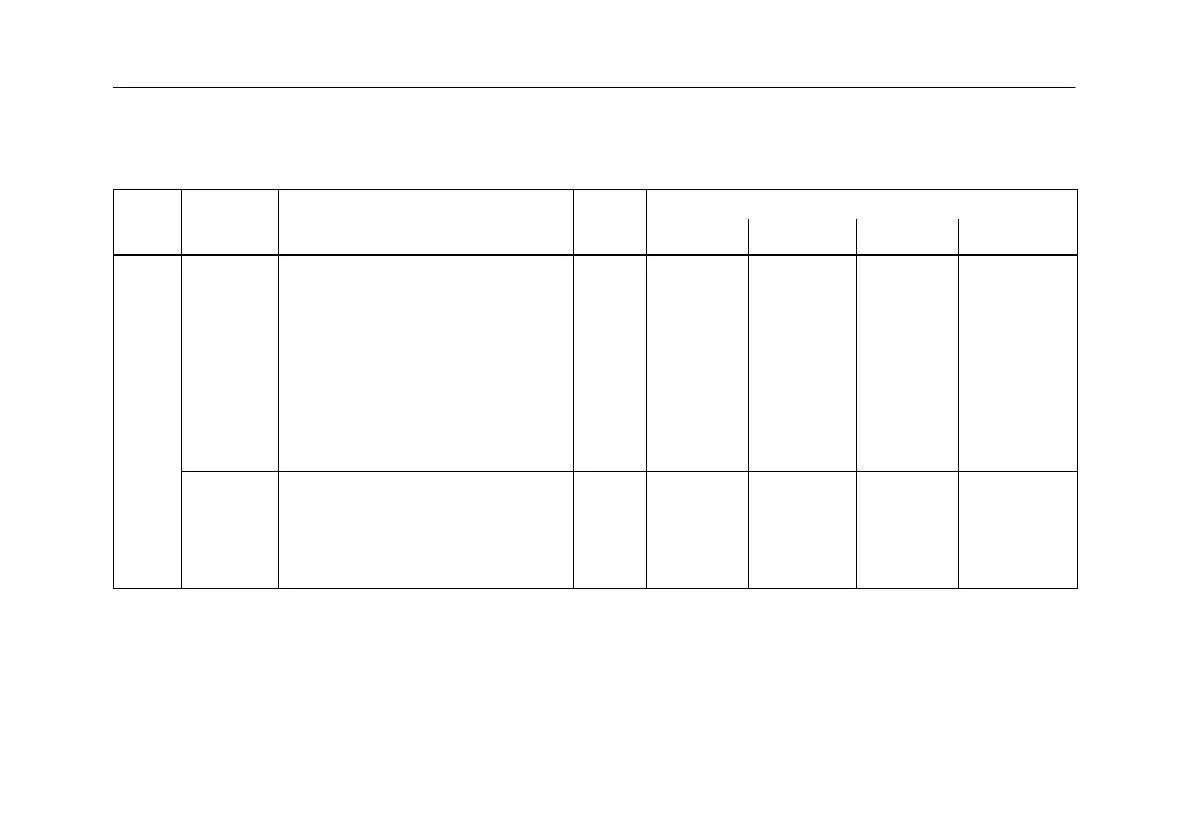

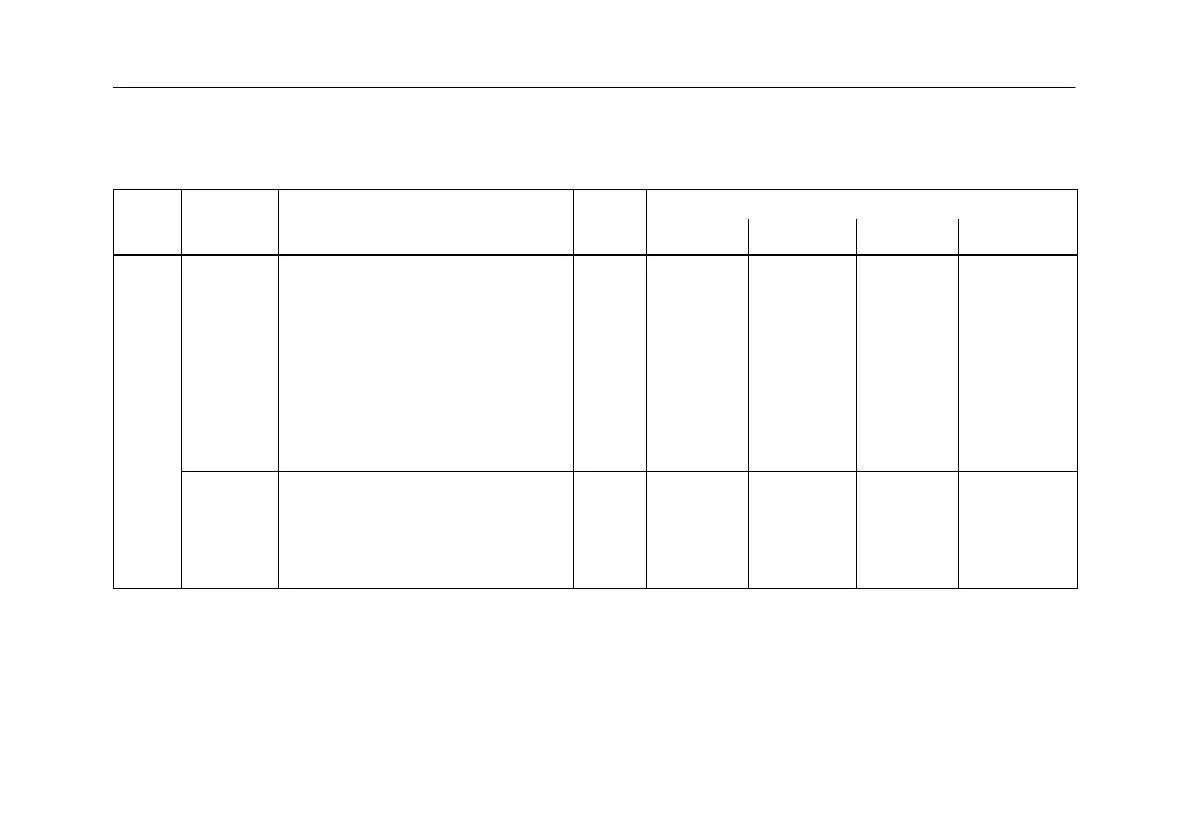

tion

ID

Description

Words

CPU 412 CPU 414 CPU 416 CPU 417

L

IB a

QB a

PIB a

Load ...

Input byte

Output byte

Peripheral input byte

2)

1

1)

/2

1

1)

/2

2

0.1/0.125

0.1/0.125

0.125

0.06/0.075

0.06/0.075

0.075

0.04/0.05

0.04/0.05

0.05

0.03/0.042

0.03/0.042

0.042

MB a

LB a

Bit memory byte

Local data byte

1

3)

/2

2

0.1/0.125

0.125

0.06/0.075

0.075

0.04/0.05

0.05

0.03/0.042

0.042

DBB a

DIB a

Data byte

Instance data byte

... into ACCU1

2

2

0.2

0.2

0.12

0.12

0.08

0.08

0.09

0.09

g [d]

g [AR1,m]

g [AR2,m]

B[AR1,m]

B[AR2,m]

Parameter

Memory-indirect, area-internal

4)

Register-indirect, area-internal (AR1)

4)

Register-indirect, area-internal (AR2)

4)

Area-crossing (AR1)

4)

Area-crossing (AR2)

4)

Via parameter

4)

2

2

2

2

2

2

0.1+/0.2+

0.125+/0.2+

0.125+/0.2+

0.125+/0.2+

0.125+/0.2+

0.125+/0.2+

0.06+/0.12+

0.075+/0.12+

0.075+/0.12+

0.075+/0.12+

0.075+/0.12+

0.075+/0.12+

0.04+/0.08+

0.05+/0.08+

0.05+/0.08+

0.05+/0.08+

0.05+/0.08+

0.05+/0.08+

0.03+/0.09+

0.42+/0.09+

0.42+/0.09+

0.42+/0.09+

0.42+/0.09+

0.42+/0.09+

+ Plus time required for loading the address of the instruction (see page 20)

1)

With indirect instruction addressing; Address area 0 to 127

2)

The following peripheral acknowledgement time must be observed with CPU 414-4H and CPU 417-4H: solo xx s, redundant xx s

3)

With direct instruction addressing; Address area 0 to 255

4)

I, Q, P, M, L / DB, DI

Loading...

Loading...