© 2004 Cisco Systems, Inc. All rights reserved. Printed in USA.

Presentation_ID.scr

393939

© 2004 Cisco Systems, Inc. All rights reserved.

RST-3508

9805_05_2004_c2

Best Practices

• Baseline the CPU in steady state

Normally which processes are causing the highest CPU usage

• When troubleshooting

Are high CPU processes different from the baseline?

Is the CPU consistently elevated or just spiking?

Are there TCNs in the network caused by flapping ports?

Is there excessive broadcast or multicast traffic in the

management subnet or VLAN?

Is there excessive management traffic such as SNMP polling?

• Isolate the management VLAN from VLANs with

user data traffic

Particularly heavy broadcast traffic such as IPX or AppleTalk

404040

© 2004 Cisco Systems, Inc. All rights reserved.

RST-3508

9805_05_2004_c2

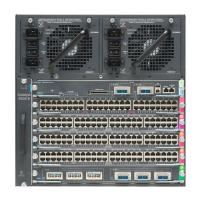

Cisco Catalyst 4500 Architecture

• 3-slot, 6-slot chassis—one supervisor

with two or five module slots

• 7-slot chassis—one or two

supervisors with five module slots

• 10-slot chassis—one or two

supervisors (Supervisor V only) with

eight module slots

• Cisco IOS supervisors provide:

Central forwarding engine

(Fast Forwarding Engine, FFE)

Buffering and 64 Gbps fabric (Packet

Processing Engine, PPE)…96 Gbps

fabric with Supervisor V and PPE2

• 12 Gbps bandwidth to each module

• Auto MDIX on 10/100/1000 Ports

• Modules are transparent:

Contain simple “stub” ASICs, PHYs

No buffering or local switching

Switching

Switching

Module

Module

Forwarding Engine (FFE)

Forwarding Engine (FFE)

Switching

Switching

Module

Module

Switching

Switching

Module

Module

Switching

Switching

Module

Module

Switching

Switching

Module

Module

Shared Memory

Shared Memory

Fabric (PPE)

Fabric (PPE)

12 Gbps

Note: Supervisor Engine V Supports

3 Additional Line Card Slots

12 Gbps

12 Gbps

12 Gbps

12 Gbps

Loading...

Loading...