CFG2

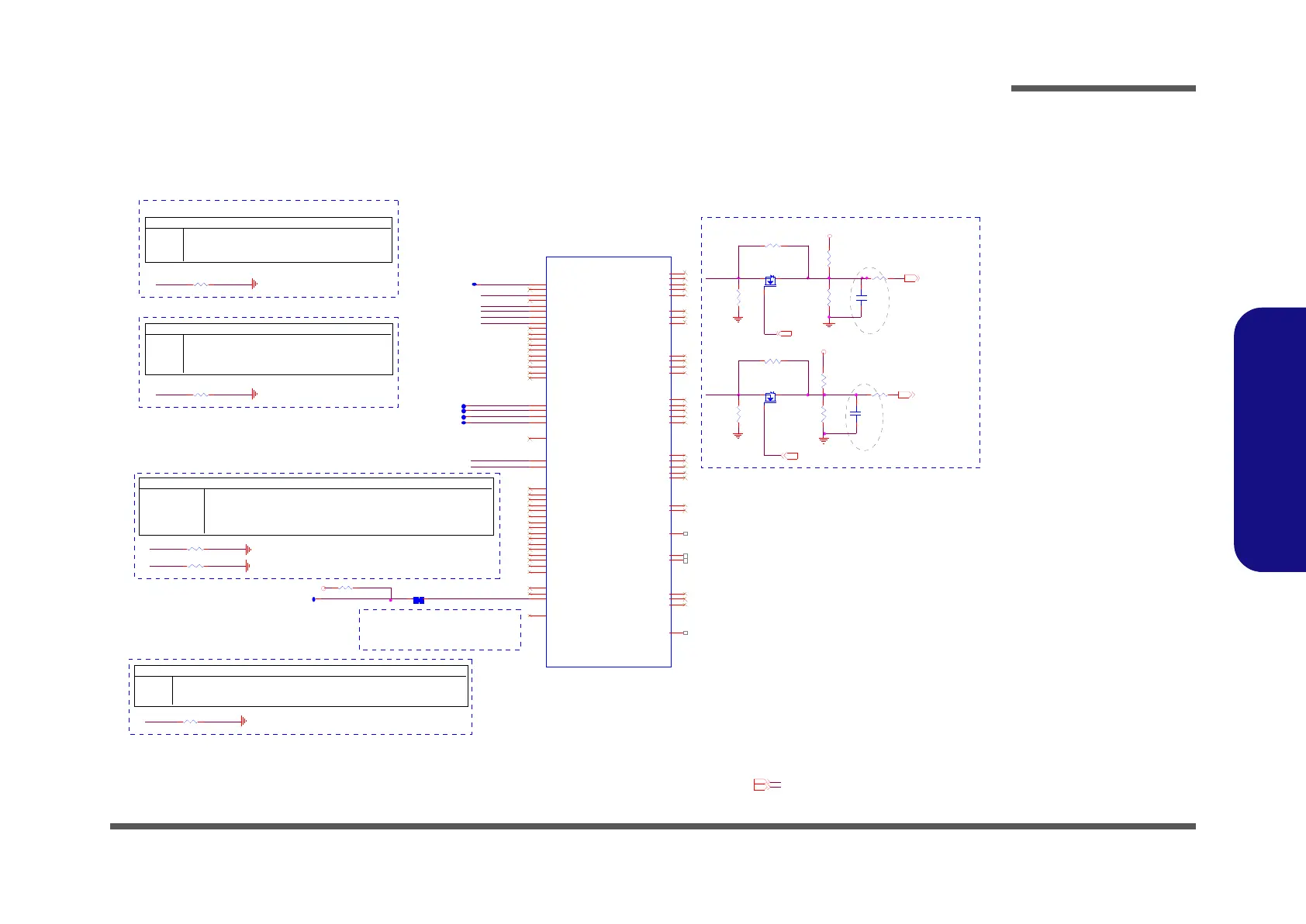

VR EF_CH _A _D IMM

R 514 10K_1%_04

3.3V

H_SNB _IV B#_PW RC TR L

H_C PU_ RS VD2

H_C PU_ RS VD1

H_C PU_ RS VD4

H_C PU_ RS VD3

On CRB

H_SNB_IVB#_PWRCTRL = low, 1.0V

H_SNB_IVB#_PWRCTRL = high/NC, 1.05V

CFG7

PEG DEFER TRAINING

1: (Default) PEG Train immediately following xxRESETB de assertion

0: PEG Wait for BIOS for training

R6 4 2 *0 _ 0 4

MVR E F _ DQ _D IM 0

R6 4 3 *0 _ 0 4

C367

0.1u_10V_X5R_04

MV R EF _ DQ _ DI M 1

CFG 6

CFG 5

CFG4

CFG2

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG[6:5]

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

CFG2

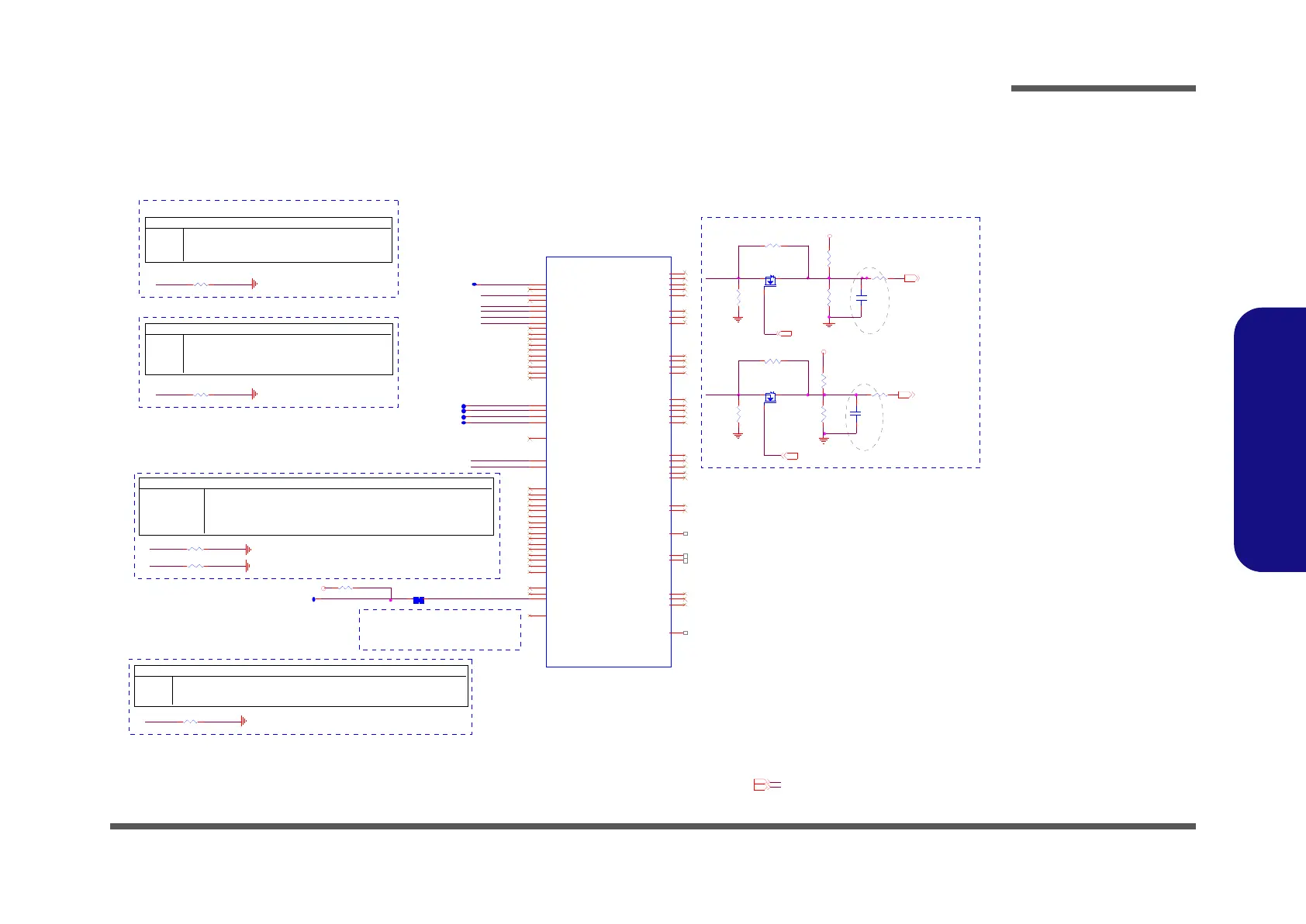

Sandy Bridge Processor 7/7 ( RESERVED )

PCIE Port Bifurcation Straps

CFG4

CFG7

RESERVED

U49 E

PZ98827-364B -01F

CFG [0 ]

AK28

CFG [1 ]

AK29

CFG [2 ]

AL26

CFG [3 ]

AL27

CFG [4 ]

AK26

CFG [5 ]

AL29

CFG [6 ]

AL30

CFG [7 ]

AM 3 1

CFG [8 ]

AM 3 2

CFG [9 ]

AM 3 0

CFG [1 0]

AM 2 8

CFG [1 1]

AM 2 6

CFG [1 2]

AN 28

CFG [1 3]

AN 31

CFG [1 4]

AN 26

CFG [1 5]

AM 2 7

CFG [1 6]

AK31

CFG [1 7]

AN 29

RS VD3 4

AM 33

RS VD3 5

AJ27

RS VD3 8

J16

RS VD4 2

AT34

RS VD3 9

H16

RS VD4 0

G16

RS VD4 1

AR 35

RS VD4 3

AT33

RS VD4 5

AR 34

RS VD5 6

AT2

RS VD5 7

AT1

RS VD5 8

AR 1

RS VD4 6

B34

RS VD4 7

A33

RS VD4 8

A34

RS VD4 9

B35

RS VD5 0

C35

RS VD5 1

AJ32

RS VD5 2

AK32

RS VD3 0

AE7

RS VD3 1

AK2

RS VD2 8

L7

RS VD2 9

AG 7

RSVD 2 7

J15

RSVD 1 6

C30

RSVD 1 5

D23

RSVD 1 7

A31

RSVD 1 8

B30

RSVD 2 0

D30

RSVD 1 9

B29

RSVD 2 2

A30

RSVD 2 1

B31

RSVD 2 3

C29

RSVD 2 4

J20

RS VD3 7

T8

RSVD 6

B4

RSVD 7

D1

RSVD 8

F25

RSVD 9

F24

RSVD 1 1

D24

RSVD 1 2

G25

RSVD 1 3

G24

RSVD 1 4

E23

RS VD3 2

W8

RS VD3 3

AT26

RSVD 2 5

B18

RS VD4 4

AP35

RSVD 1 0

F23

RSVD 5

AJ2 6

VAXG_VAL _SEN SE

AJ3 1

VSSAXG_VA L_SEN SE

AH 31

VCC _VAL _S ENSE

AJ3 3

VSS_VAL _SENS E

AH 33

KEY

B1

VCC_DIE_SENSE

AH 27

VCC IO_ SEL

A19

RS VD5 4

AN 35

RS VD5 5

AM 35

R516 *10mil_short

10/21

H_SN B_IVB#_ PW RC TRL_ R

CFG7

CFG Straps for Processor

3.3V2 ,3,1 1 ,1 2,16 ,18 ,19 ,2 0,2 2,2 3 ,2 4 ,25 ,2 7 ,2 8, 29 ,3 0 ,3 3,3 5 ,3 7 ,38 ,3 9

CFG5

Display Port Presence Strap

1:(Default) Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG4

VRE F_C H_A_D IMM

R1 5 9

1K_1%_04

R500 *1K_04

Q9

*A O 3 40 2 L

G

DS

R49 1 * 1K _04

R153

*1K _04

Q1 0

*A O 3 40 2 L

G

DS

R1 6 0

1K_1%_04

R149

*1K _04

R15 5

1K _ 1 % _ 04

R492 *1K_04

R4 9 3 * 1 K_0 4

R5 0 3 * 1 K_0 4

R15 0

1K _ 1 % _ 04

1.5V

1.5V

DRAMRST_CNTRL 3,19

DR AMR ST_C NT R L 3,1 9

1.5V3,6,9, 10,25,29,33,35,37,38

CFG0

C35 7

0.1u_10V_X 5R _04

10/21

MV R EF _ DQ _D IMM A 9

R25 4 0_ 04

CFG6

MV REF _ D Q_ DIM MB 10

R27 7 0_ 04VR EF_CH _B _D IMM

VRE F_C H_B_D IMM

Loading...

Loading...