INTERRUPTS

AND

EXCEPTIONS

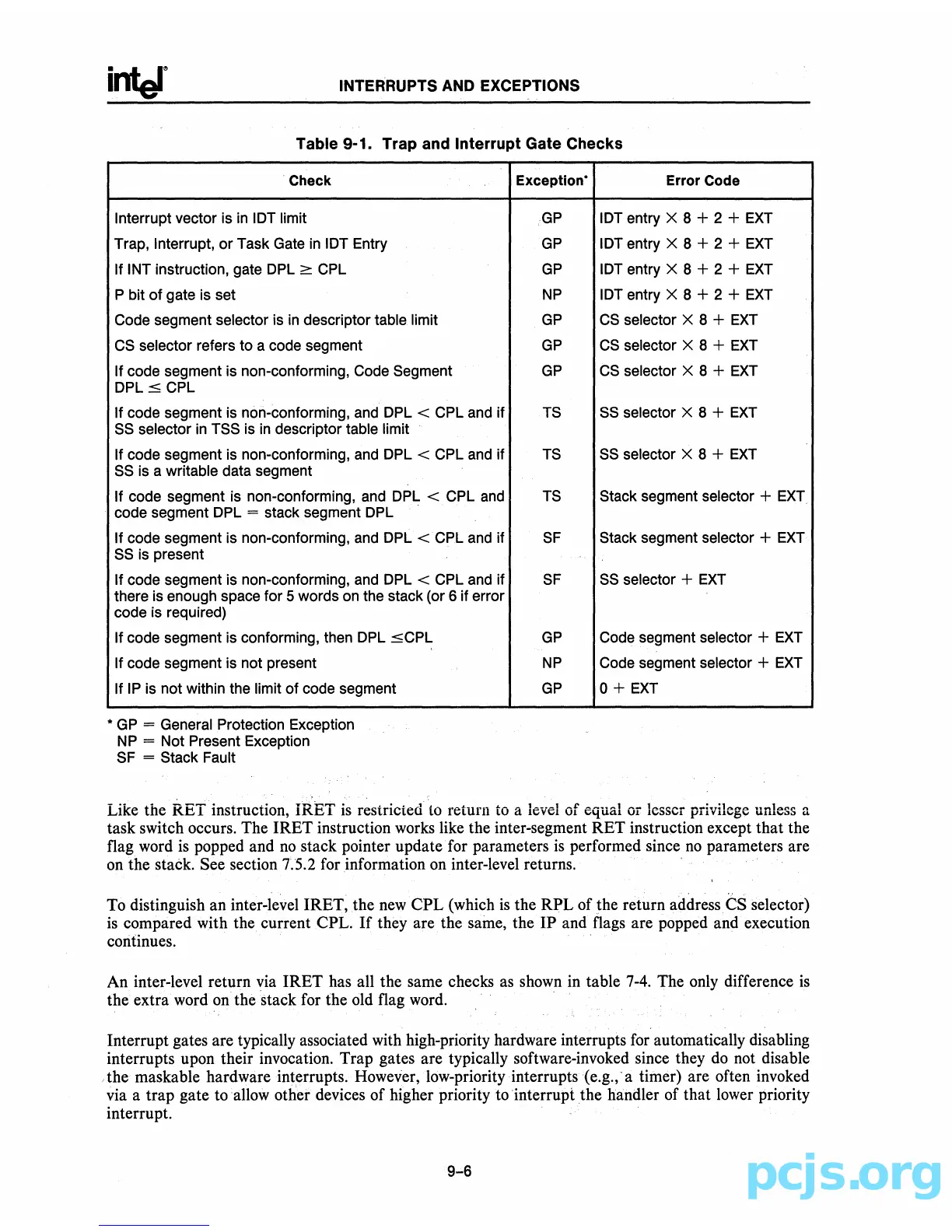

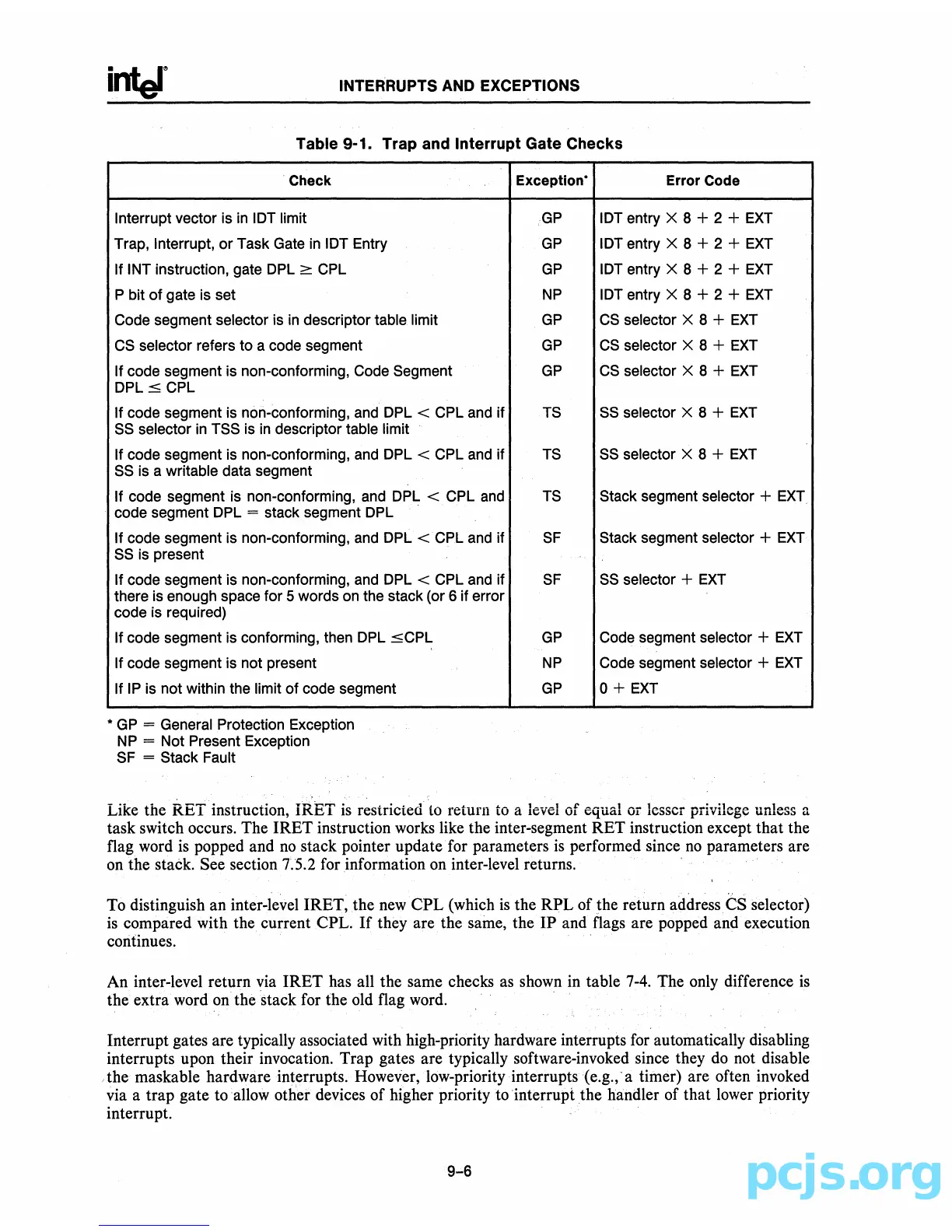

Table 9-1, Trap and

Interrupt

Gate Checks

Check

Interrupt vector

is

in

lOT

limit

Trap, Interrupt, or Task Gate

in

lOT

Entry

If

INT

instruction, gate

OPL

CPL

P bit of gate is

set

Code segment selector

is

in

descriptor table

limit

CS selector refers to a code segment

If

code segment

is

non-conforming, Code Segment

OPL

=:;

CPL

If

code segment

is

non-conforming, and

OPL

<

CPL

and

if

SS

selector

in

TSS

is

in

descriptor table

limit

If

code segment is non-conforming, and

OPL

< CPL and

if

SS

is

a writable data segment

If

code segment

is

non-conforming, and

OPL

< CPL and

code segment

OPL

= stack segment

OPL

If

code segment is non-conforming, and

OPL

<CPL

and

if

SS

is

present

If

code segment is non-conforming, and

OPL

<

CPL

and

if

there

is

enough space for 5 words on the stack (or 6

if

error

code is required)

If

code segment

is

conforming, then

OPL

=:;CPL

If

code segment

is

not present

If

IP

is not

within

the

limit

of code segment

•

GP

= General Protection Exception

NP

=

Not

Present Exception

SF

= Stack Fault

, '

','.

Exception'

Error Code

GP

lOT

entry X 8 + 2 +

EXT

GP

IDTentry X 8 + 2 +

EXT

GP

lOT

entry X 8 + 2 +

EXT

NP

lOT

entry X 8 + 2 +

EXT

GP

CS selector X 8 +

EXT

GP

CS selector X 8 +

EXT

GP

CS selector X 8 +

EXT

T8

88

selector X 8 +

EXT

TS

SS selector X 8 +

EXT

TS Stack segment selector +

EXT

SF Stack segment selector +

EXT

SF SS selector +

EXT

GP

Code segment selector +

EXT

NP

Code segment selector +

EXT

GP

0+

EXT

Like the

RET

instruction,

ntET

is

restricted

to

return to a level

of

equal or lesscr privilege unless a

task switch occurs. The

IRET

instruction works like the inter-segment

RET

instruction except

that

the

flag

word

is popped and

no

stack pointer update for parameters

is

performed since

no

parameters are

on the stack. See section 7:5.2 for information on inter-level returns. '

To distinguish an inter-ievel

IRET,

the

new

CPL

(which is the

RPL

of the return

CS

selector)

is compared with the current CPL.

If

they are the same, the

IP

and flags are popped and execution

continues. '

An

inter-level return via

IRET

has all the same checks as shown in table

7-4.

The only difference

is

the

extra

word

on

the stack for the old flag word.

Interrupt gates are typically associated with high-priority hardware interrupts for automatically disabling

interrupts upon their invocation. Trap gates are typically software-invoked since they do not disable

,the

maskable hardware interrupts. However, low-priority interrupts

{e.g.;a

timer) are often invoked

via a

trap

gate to allow other devices

of

higher priority to 'interrupt

the

handler of

that

lower priority

interrupt.

9-6

Loading...

Loading...