7

Serial Communications Connection Procedure

18

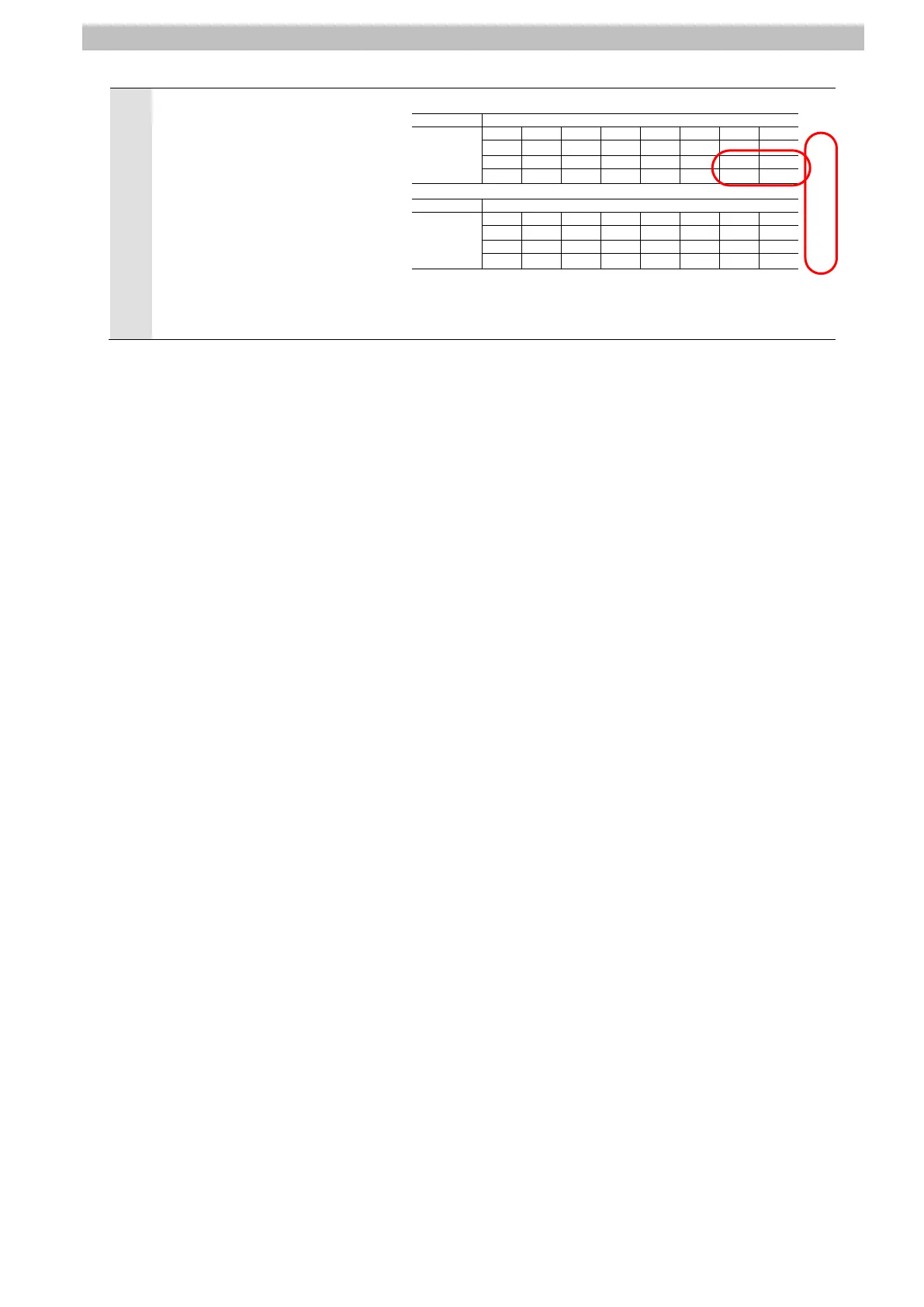

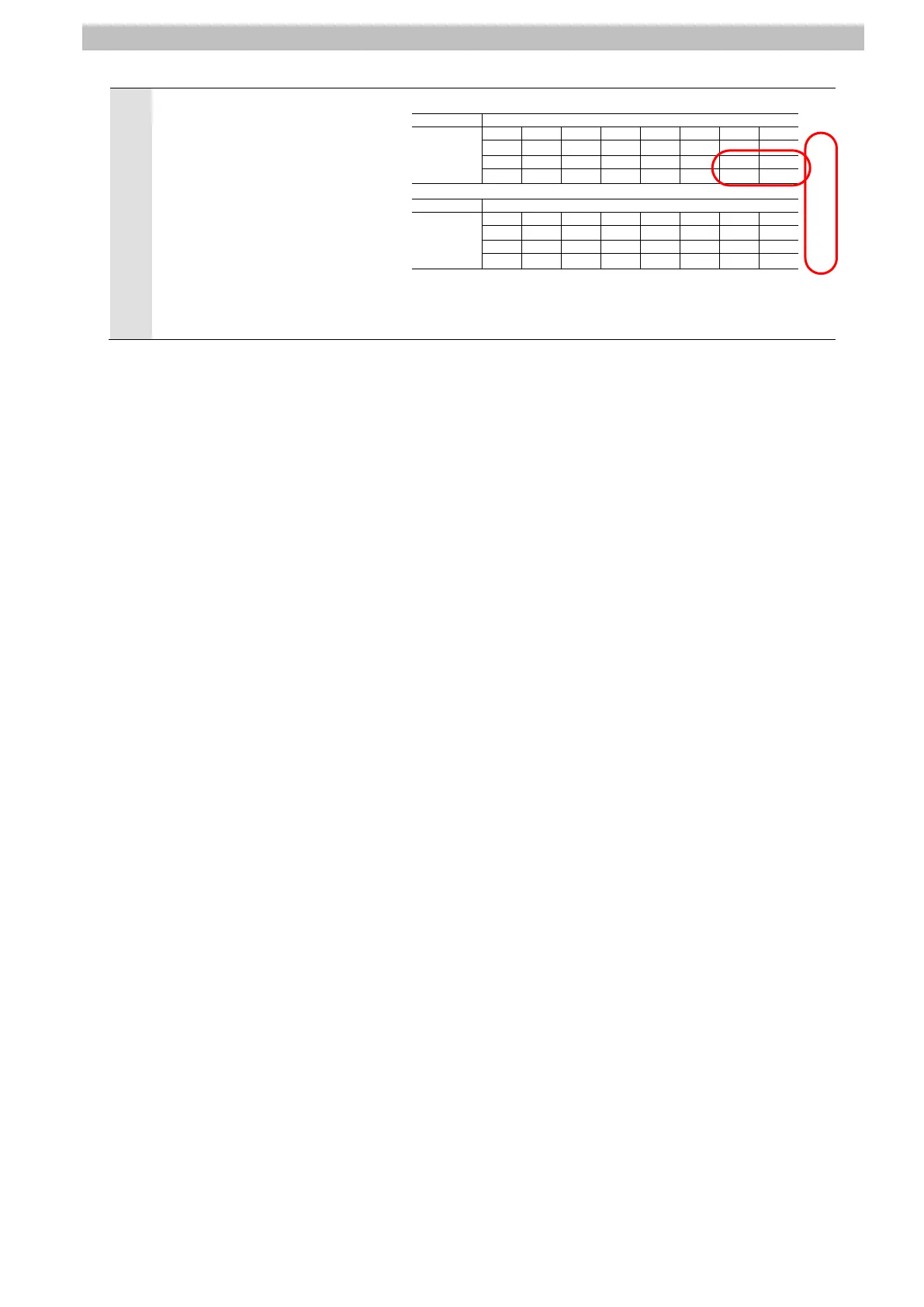

The read data [00], [02], [00],

and [00] in step 13 correspond

to the table of "Direct I/O and

electromagnetic brake status"

shown on the right.

OUT0 (Bit 0) = 0

OUT1 (Bit 1) = 1

This indicates that they accord

with the OUTPUT status of I/O

(direct I/O) signals in step 17.

■Direct I/O and electromagnetic brake status (00D4h, 00D5h)

00D4h

00D5h

Loading...

Loading...