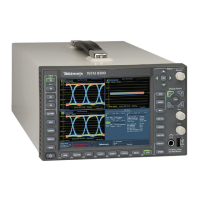

Theory of Oper ation

Rasterizing Engine

The Rasterizer engine resides in the waveform processing FPGAs. This block

builds up the variable intensity images in the fast static RAM. For each pixel of the

display, the Rasterizer Engine increments the intensity of that pixel every time the

waveform hits its coordinates. As a result, the waveform areas hit more frequently

display mor

e brightly. For any given frame, the intensity map is built up in one

memory chip and read out of the other. The functions swap on the next frame.

Recursion a nd Picture Processing Engine

The output of the rasterizer feeds the picture and recursive processing engine in

the display (DSY) FPGA. This engine adds the previous frame to the present

frame to reduce flicker and improve brightness. It also converts the picture and

waveform signals from the input rate of 50 or 59.94 Hz to 60 Hz frame rate to

work with the XGA monitor. The p icture and waveform data combine with the

graphi

cs and audio bar information from the control processor, and then output to

the XGA DAC to drive the external monitor. Note that the parallel data from the

serial digital input and the parallel stream from the composite decoder connect

directly to this FPGA to provide the picture functionality, bypassing the waveform

processing engine.

Cont

rol Processor

The control processor is in charge of all the operational modes in the instrument. It

draws the audio bars, communicates with the front panel through RS232 signaling,

and

controls most other internal devices though either the parallel or the I2C bus.

A few parts communicate through other bus types like JTAG or SPI. Audio data is

input to the control processor via the 8 bit HPI bus.

The control processor interfaces to the Ethernet through a dual rate switch. This

allows the network connection to run at 10 or 100 MB/s.

2–4 WVR6020, WVR7020, and WVR7120 Waveform Rasterizers Service Manual

Loading...

Loading...