Tuner DSP general purpose I/O flag 1.

pin 97

Tuner DSP general purpose I/O flag 2.

pin 98

Tuner DSP general purpose I/O flag 3.

pin 99

Tuner DSP general purpose I/O flag 4

Tuner DSP general purpose I/O flag 5.

Tuner DSP general purpose I/O flag 6.

Tuner DSP general purpose I/O flag 7.

Tuner DSP general purpose I/O flag 8.

Ground supply (peripheral cells only).

Positive supply (peripheral cells only).

Tuner DSP general purpose I/O flag 9.

Tuner DSP general purpose I/O flag 10.

LSB Gain control output 1 to DICE 1.

MSB Gain control output 2 to DICE 1.

LSB Gain control output 1 to DICE 2.

MSB Gain control output 2 to DICE 2.

Tuner DSP general purpose I/O flag 11.

Tuner DSP general purpose I/O flag 12.

Audio DSP general purpose I/O flag

(e.g. IBOC_BLEND).

Serial data output IBOC I-signal.

Serial data output IBOC Q-signal.

Ground supply (for memories).

1.8V positive supply (for memories only).

Serial clock output I2C bus to the I2C clock

inputoftheDICE.

Serial data input/output I2C bus to the data

inputoftheDICE.

100 kHz clock current output reference to DICE2.

100 kHz clock not current output reference

to DICE2.

Ground supply (peripheral cells only).

Ground supply for oscillator and PLLs.

Crystal oscillator input.

Crystal oscillator output.

1.8V supply for oscillator and PLLs.

Negative phase of the first differential IF input.

Positive phase of the first differential IF input.

Ground supply for IF ADCs.

Decoupling for IF ADCs positive reference voltage.

Ground reference voltage for IF ADCs.

Decoupling for IF ADCs bandgap voltage.

Positive phase of the second differential IF input.

Negative phase of the second differential IF input.

Automatic Frequency Control.

AGC

Automatic Gain Control.

AM

Basic IO System Read Only Memory.

CD

Common Mode Rejection Ratio.

CRD

Cordic Rotate and Derotate.

DAC

DigitaltoAnalogConverter.

DARC

Digital In Car Entertainment.

DSP

Digital Signal Processor.

EPICS

Economic Parameterised Integrated CoreS.

FIR

Finite Impulse Response.

FM

Inter IC Communication.

I2S

Inter IC Sound (Philips standard).

IAC

Interference Absorption Circuit.

IBOC

Intermediate Frequency.

IFAD

Intermediate Frequency Analog to Digital Converter.

IIS

Inter IC Sound (any data format).

IP

Intellectual Property.

KAGC

frequency MultiPleXed signal (audio/data).

MSS

Precision Adjacent Channel Suppression.

PDC

Primary Decimation Chain.

PRAM

Program Random Access Memory.

PROM

Program Read Only Memory.

RDS

Samplerate converter DSP.

SPDIF

Sony/Philips Digital Interface Format.

SRC

X (typically for DSP data) Random Access Memory.

YRAM

Y (typically for DSP coefficients) Random Access Memory.

YROM

Y (typically for DSP coefficients) Read Only Memory.

ZIF

Zero IF.

Terminal Description

051-9426-90 S-24CS16A01-T8T1G EEP ROM

Serial data input/output.

Write protect signal input.

Analog to Digital converter.

ADC

Analog to Digital converter.

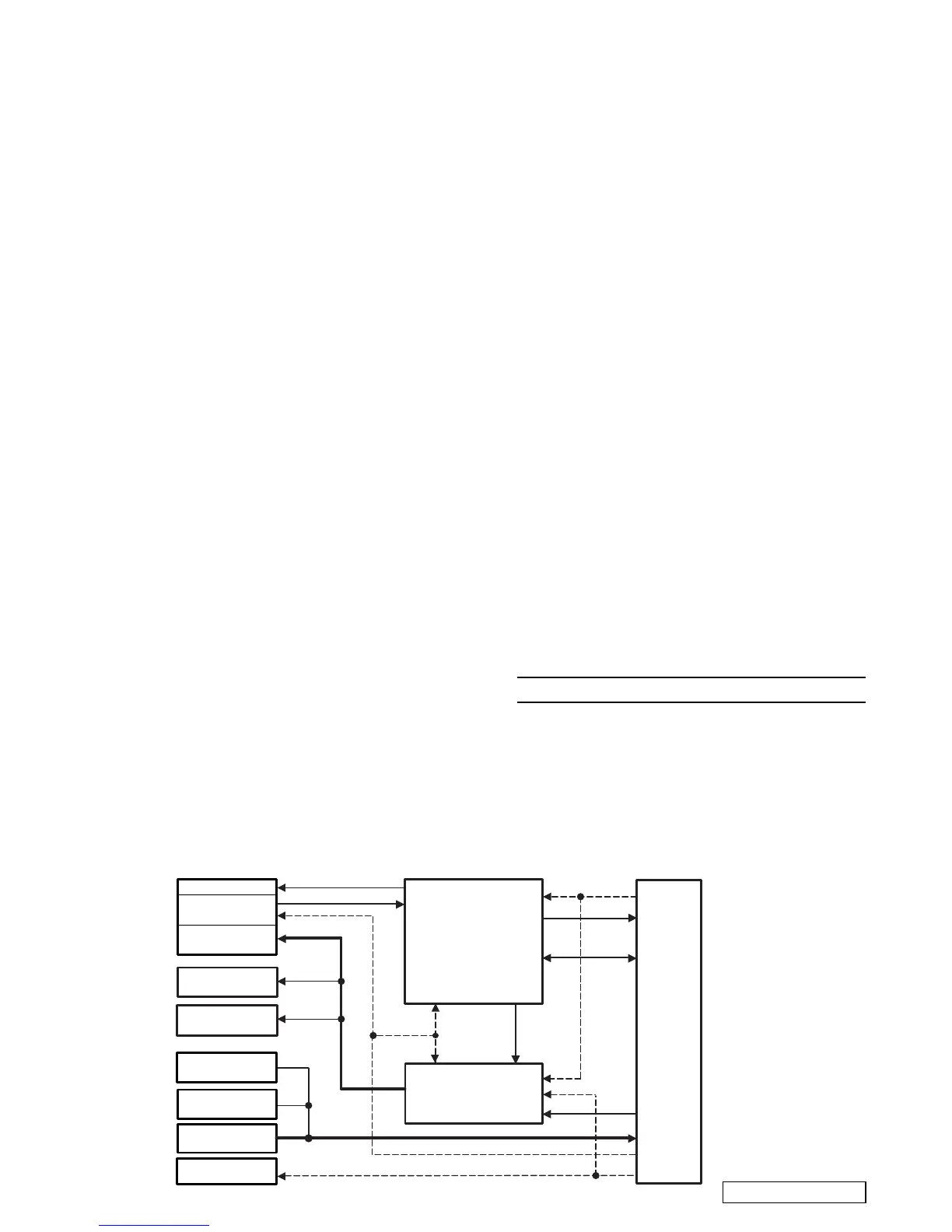

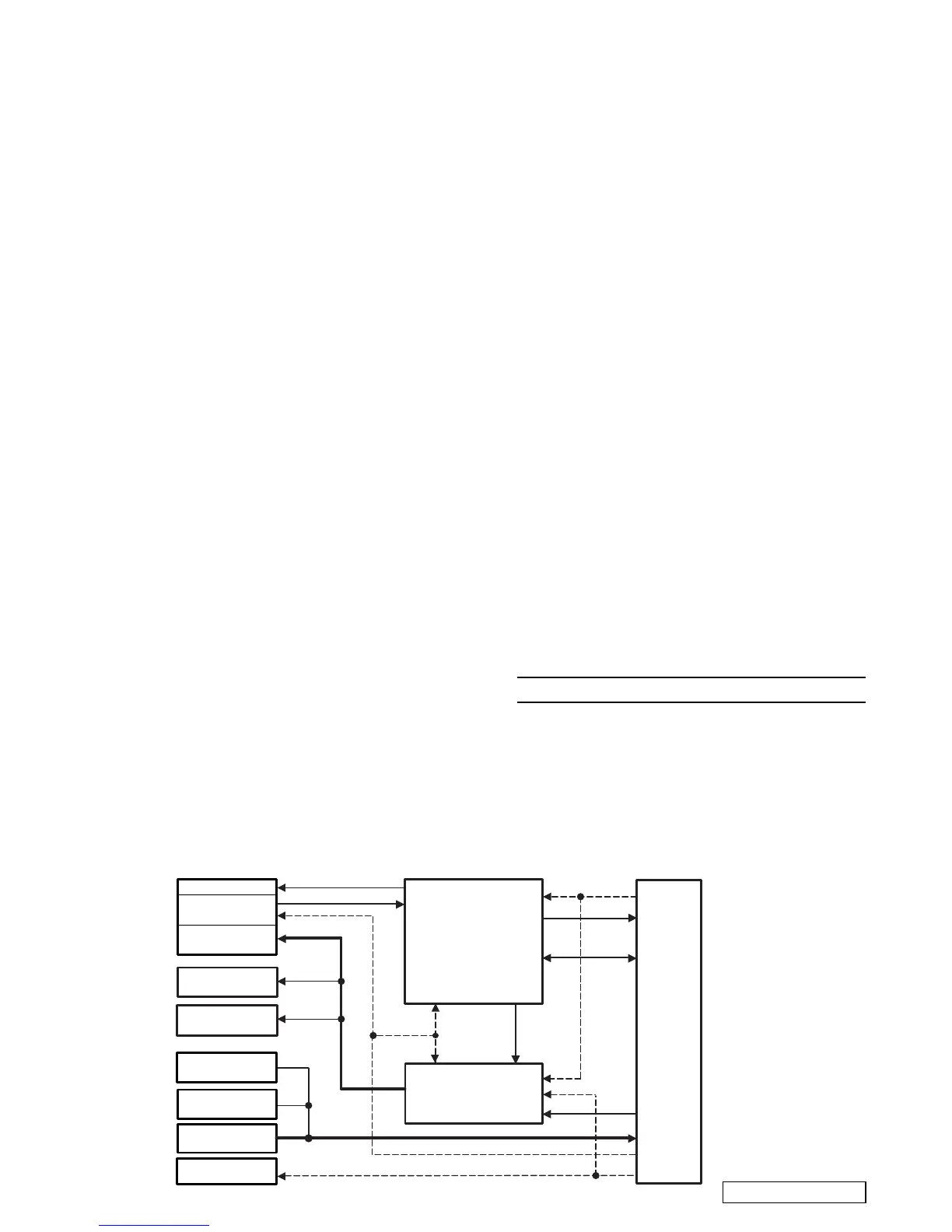

CD mechanism section:929-5000-80

BLOCK DIAGRAM

J101

SLED / LOADING

MOTOR

SPINDLE MOTOR

RF-AMP

SERVO PROCESSOR

IC2

TC94A15F

MOTOR DRIVER

IC1

BA5830FP-E2

IF-VDD

8.0V

AOUT

SFSY

SBSY

/RST

BUS0

BUS1

BUS2

BUS3

BUCK

/CCE

DATA

LDMUT

LDCONT

SW /

DET

3.3V

PICK UP UNIT

LASER

DETECTOR

A,B,C,E,F

FOCUS

TRACKING COIL

S2

LIMIT

SWITCH

CHUCKING

SWITCH

Q1,2

PHOTO

TR A,B

D1,2

LED A,B

S1

CLCK

BCK

LRCK

MBOV

IPF

8V

CD-VDD

3.3V

5.0V

PF-2945A-A/PF-2982B-A

-5-

Loading...

Loading...