D D

C C

B B

A A

check IN_CA,1/13

check IN_CA,1/13

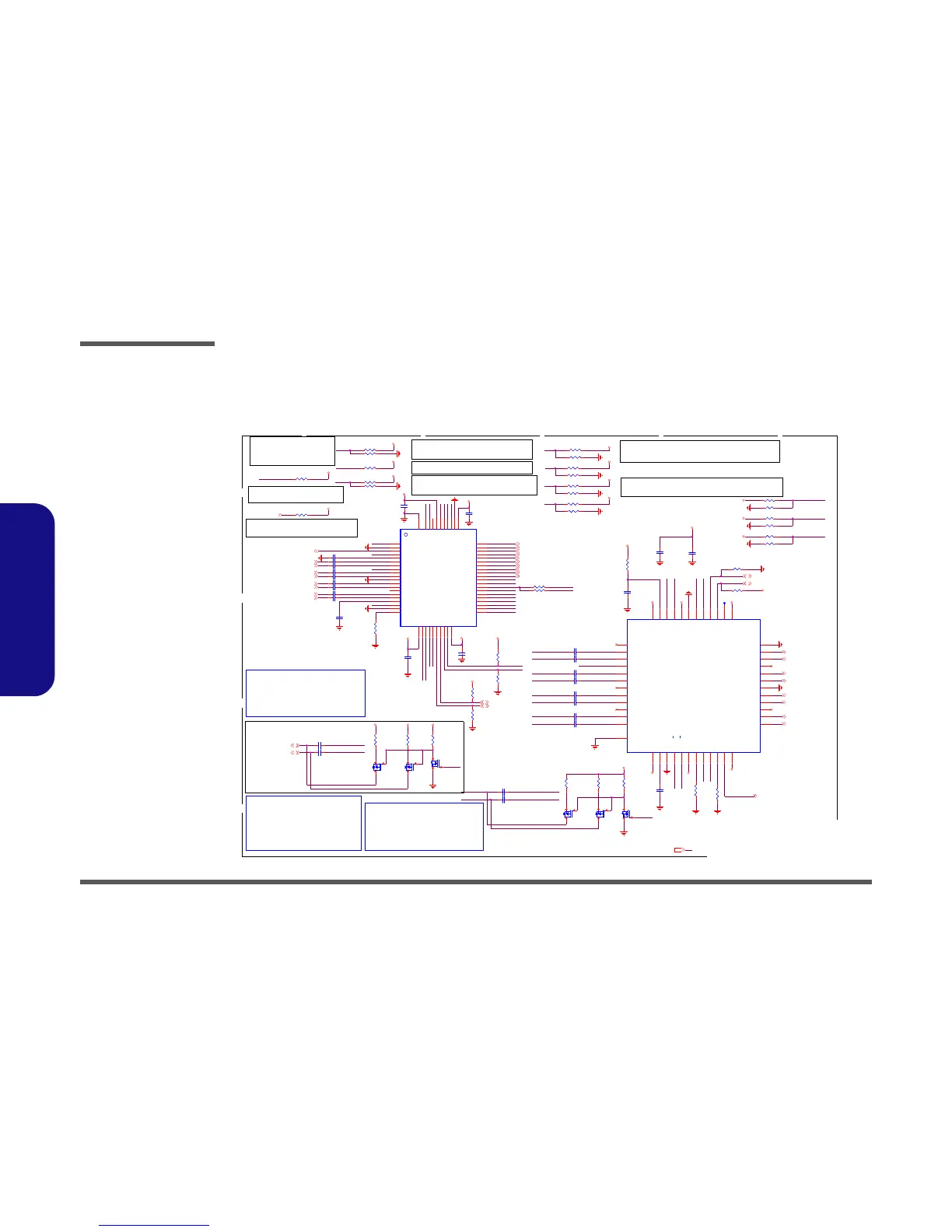

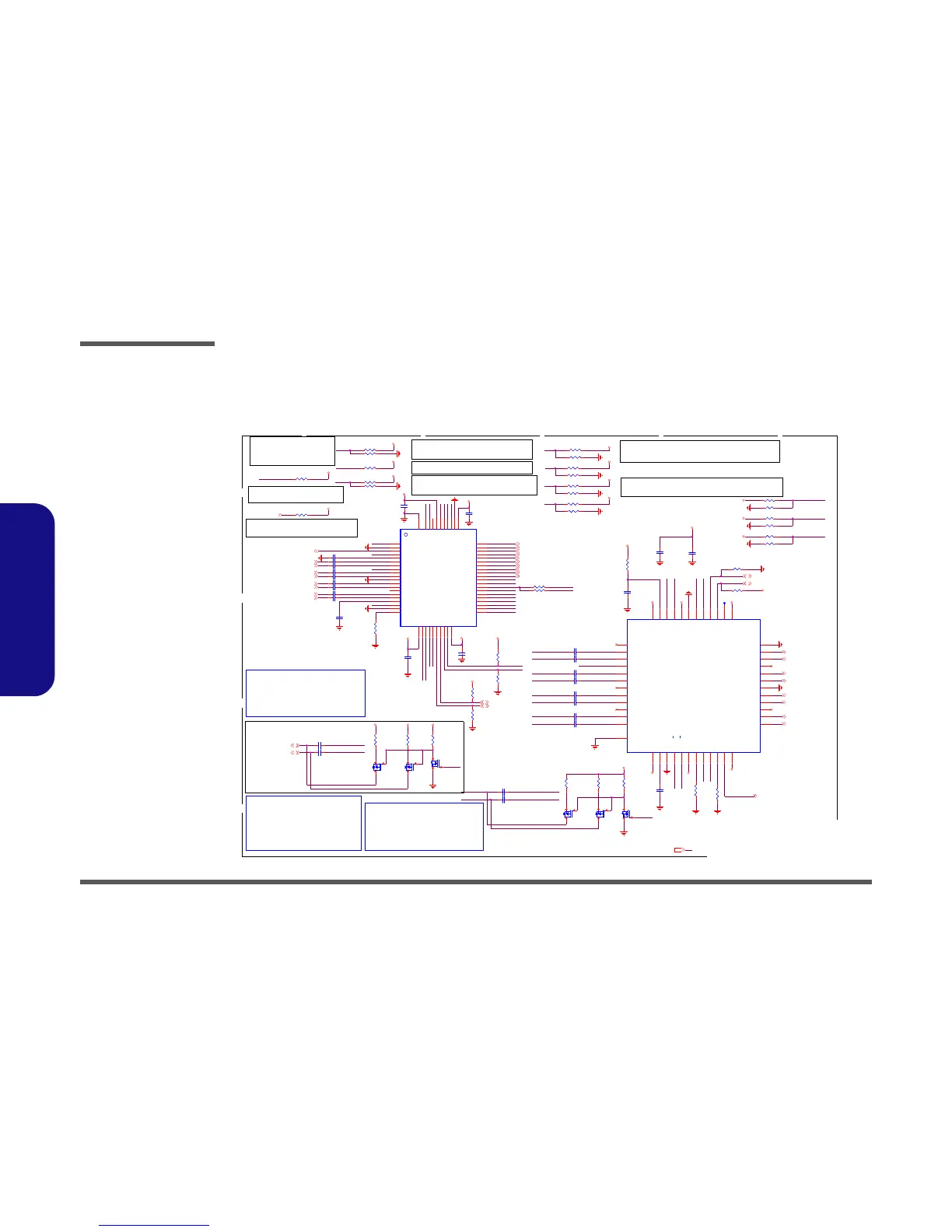

DESIGN NOTE:CFG0

Configuration pin for automatic EQ and

Aux interception; Internal pull down at

150Kohm,3.3V I/O

L: default, automatic EQ enable and Aux interception enable

H: automatic EQ disable and AUX interception enable

M: automatic EQ disable and AUX interception

disable,no pre-emphasis, 600mVpp swing

DESIGN NOTE:CFG1

Configuration pin for auto test and input offset

cancellation,3.3V IO, internal pull up at 150K

H: default, auto test disable and input offset cancellation

enable

L: auto test enable and input offset cancellation enable

M: auto test disable and input offset cancellation disable

DESIGN NOTE:PEQ

Programmalbe input equalization levels;internal pull

down at 150k ,3.3v I/O

L: default, LEQ, compensate channel loss up to 12dB at

HBR2

H: HEQ, compensate channel loss up to 15dB at HBR2

M:LLEQ, compensate channel loss up to 5dB at HBR2

DEFAULT:LOW

Auto test enable; Internal pull down at ~150K

*

, 3.3V I/O.

L: Auto test disable & input offset cancellation enable (default)

H: Auto test enable & input offset cancellation enable

M: Auto test disable & input offset cancellation disable

Automatic EQ disable; Internal pull down at ~150K

*

, 3.3V IO

L: Automatic EQ enable (default)

H: Automatic EQ disable

Programmable input equalization levels; Internal pull down at

~150K

*

, 3.3V I/O.

L: default, LEQ, compensate channel loss up to 11.5dB @ HBR2

H: HEQ, compensate channel loss up to 14.5dB @ HBR2

M: LLEQ, compensate channel loss up to 8.5dB @ HBR2

Port switching control or priority configuration;

Internal pull down at ~150K

*

, 3.3V I/O.

L: Port1 is selected or with higher priority (default)

H: Port2 is selected or with higher priority

Chip operational mode configuration;

Internal pull down at ~150K

*

, 3.3V I/O.

L: Control switching mode (default)

H: Automatic switching mode

3 Levels Input:

L: Low

H: High

M: VDD33/2, connect both

pull-up and pull-down resistors

AUX interception disable for Port y (y = 1, 2). Internal pull down at ~150K

*

, 3.3V I/O;

L: AUX interception enable, driver configuration is set by link training (default)

H: AUX interception disable, driver output with fixed 800mV and 0dB

M: AUX interception disable, driver output with fixed 400mV and 0dB

Hybrid DDC/AUX

Output swing adjustment for Port y (y = 1, 2). Internal pull down at ~150K

*

, 3.3V I/O;

L: default

H: +20%

M: -16.7%

CAD_S NK

PS8330B_CFG1

PS8330B_CFG0

PEQ

HPD_S RC

CAD_S RC

OUT2_HPD

IN_DDC_SDA

IN_DDC_SCL

PS8330B_AUXp

PS8330B_AUXn

OUT2_AUXp_SCL

OUT2_AUXn_SDA

PS8330B_AUXn

PS8330B_AUXp

IN_DDC_SDA

IN_DDC_SCL

IN_DDC_SCL

CAD_S RC

IN_A UXn

IN_DDC_SDA

IN_DDC_SCL

DP_A 1

DP_A#3

PS8330B_IN_D2n

IN_D2p

PI1

PI0

PSCFG0

PC11

PC20

PC21

PC10

PSPEQ

3.3VS

IN_D1p

PSPEQ

3.3VS

IN_CA _DET

PI0

PS8330B_IN_D3p

IN_D2n

DP_A#1

PS8330B_IN_D3n

IN_D3p

DP_A#2

IN_D3n

CAD_S RC

DP_A 3

PI1

PSCFG0

DP_A 2

PS8338B_SW

MUX_A UXP _DDC_S CL

MUX_A UXN_DDC_ SDA

IN_A UXp

IN_A UXn

PC10

IN_A UXp

IN_CA _DET

GND

MUX_A UXP _DDC_S CL

MUX_A UXN_DDC_ SDA

PC21

PC20

DP_A_HPD

PS8330B_IN_D0p

IN_D0p

PS8330B_IN_D0n

PS8330B_IN_D1p

IN_D0n

PS8330B_IN_D1n

DP_A 0

PS8330B_IN_D2p

IN_D1n

DP_A#0

PS8330B_CFG1

PS8330B_CFG0

PEQ

IN_DDC_SDA

PS8330B_IN_D0p

PS8330B_IN_D0n

IN0P_R

IN0N_R

PS8330B_IN_D1n

PS8330B_IN_D1p IN1P_R

IN1N_R

PS8330B_IN_D2n

PS8330B_IN_D2p IN2P_R

IN2N_R

PS8330B_IN_D3n

PS8330B_IN_D3p IN3P_R

IN3N_R

HPD_S RC_R HPD_SRC

OUT2_HPD

PC11

3.3VS 3.3VS

3.3VS

3.3VS

3.3VS 3.3VS 3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS 3.3VS 3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

3.3VS

OUT2_D0p 38

OUT2_D0n 38

OUT2_D1p 38

OUT2_D1n 38

OUT2_D2n 38

OUT2_D2p 38

OUT2_D3p 38

OUT2_D3n 38

DP_A 0 12

DP_A#0 12

DP_A 1 12

DP_A#1 12

DP_A 2 12

DP_A#2 12

DP_A 3 12

DP_A#3 12

DP_A_HPD 12

OUT2_AUXp_SCL 38

OUT2_AUX n_SDA 3 8

G_DPA_MODE 12

OUT2_HPD 38

OUT1_AUXp_SCL 12

OUT1_AUXn_SDA 12

MUX_0P15

MUX_HPD15

MUX_2P15

MUX_1N15

MUX_1P15

MUX_0N15

MUX_3N15

MUX_3P15

MUX_2N15

MUX_A UXN_DDC_ SDA15

MUX_A UXP _DDC_S CL15

3.3VS10,11,12,13,14,15,16,17,18,19,20,21,23,24,25,26,27,28,31,32,33,34,35,39,41,42,43,46,48,50,7,8,9

PS8338B_SW17

Title

Size Document Number Rev

Date: Sheet

of

6-71-P75D0-D03

2.0

[37] AR_PS8338B+PS8330B

A3

37 62Monday, August 03, 2015

!!DMFWP!DP/

SCHEM ATIC1

Title

Size Document Number Rev

Date: Sheet

of

6-71-P75D0-D03

2.0

[37] AR_PS8338B+PS8330B

A3

37 62Monday, August 03, 2015

!!DMFWP!DP/

SCHEM ATIC1

Title

Size Document Number Rev

Date: Sheet

of

6-71-P75D0-D03

2.0

[37] AR_PS8338B+PS8330B

A3

37 62Monday, August 03, 2015

!!DMFWP!DP/

SCHEM ATIC1

R88

*4.7K_ 04

R88

*4.7K_ 04

C141

0.01u_16V_X7R_04

C141

0.01u_16V_X7R_04

R410 100K_04R410 100K _04

Q43

MTN7002ZHS3

Q43

MTN7002ZHS3

G

DS

R72

4.7K_04

R72

4.7K_04

R98

*4.7K_ 04

R98

*4.7K_ 04

R619 *4.7K_04R619 *4.7K_04

C602 0.1u_10V_X7R_04C602 0.1u_10V_X7R_04

R92 *4.7K_04R92 *4.7K_04

R449 *4.7K_04R449 *4.7K_04

R595

4.99K_1%_04

R595

4.99K_1%_04

C111 0.1u_10V_X7R_04C111 0.1u_10V_X7R_04

R596

100K_04

R596

100K_04

C127 0.1u_10V_X7R_04C127 0.1u_10V_X7R_04

C112 0.1u_10V_X7R_04C112 0.1u_10V_X7R_04

R91 *4.7K_04R91 *4.7K_04

C104 0.1u_10V_X7R_04C104 0.1u_10V_X7R_04

R605 *4.7K_04R605 *4.7K_04

PS8330B

U32

PS8330B

PS8330B

U32

PS8330B

VDD33

1

CEXT

2

I2C_ADDR

3

SCL_CTLPEQ

4

SDA_CLTCFG0

5

VDD33

6

REXT

7

CAD_SRC

8

HPD_SRC

9

CAD_SNK

10

HPD_SNK

11

VDD33

12

OUT3n

13

OUT3p

14

NC

15

OUT2n

16

OOUT2p

17

GND

18

OUT1n

19

OUT1p

20

NC

21

OUT0n

22

OUT0p

23

GND

24

VDD33

36

RST#

35

SDA_DDC

34

SCL_DDC

33

VDD33

32

GND

31

AUX_SRCp

30

AUX_SRCn

29

AUX_SNKp

28

AUX_SNKn

27

PD#

26

VDD33

25

IN3n

48

IN3p

47

NC

46

IN2n

45

IN2p

44

NC

43

IN1n

42

IN1p

41

CFG1

40

IN0n

39

IN0p

38

NC

37

EPAD

49

C446

0.1u_10V_X7R_04

C446

0.1u_10V_X7R_04

Q44

AO3415

Q44

AO3415

G

D S

C459 2.2u_6.3V_X5R_04C459 2.2u_6.3V_X5R_04

C92

2.2u_6.3V_X5R_04

C92

2.2u_6.3V_X5R_04

R583

4.7K_04

R583

4.7K_04

Q42

AO3415

Q42

AO3415

G

D S

C670 0.1u_10V_X7R_04C670 0.1u_10V_X7R_04

R439 10K_04R439 10K_04

C675 0.1u_10V_X7R_04C675 0.1u_10V_X7R_04

C126 0.1u_10V_X7R_04C126 0.1u_10V_X7R_04

R71

100K_04

R71

100K_04

C125 0.1u_10V_X7R_04C125 0.1u_10V_X7R_04

R411 100K_04R411 100K _04

R99 *4.7K_04R99 *4.7K_04

Q10

MTN7002ZHS3

Q10

MTN7002ZHS3

G

DS

R70

100K_04

R70

100K_04

C673 0.1u_10V_X7R_04C673 0.1u_10V_X7R_04

R594

4.7K_04

R594

4.7K_04

C84 0.1u_10V_X7R_04C84 0.1u_10V_X7R_04

R412 1M_04R412 1M_04

R607 *0_04R607 *0 _04

R93 *4.7K_04R93 *4.7K_04

R83 *4.7K_04R83 *4.7K_04

C90

0.01u_16V_X7R_04

C90

0.01u_16V_X7R_04

R97

*4.7K_ 04

R97

*4.7K_ 04

C674 0.1u_10V_X7R_04C674 0.1u_10V_X7R_04

Q45

AO3415

Q45

AO3415

G

D S

R431 *4.7K_04R431 *4.7K_04

C106 0.1u_10V_X7R_04C106 0.1u_10V_X7R_04

R429 *4.7K_04R429 *4.7K_04

R622 *4.7K_04R622 *4.7K_04

R441 *4.7K_04R441 *4.7K_04

R606 0_04R606 0_04

C688 0.1u_10V_X7R_04C688 0.1u_10V_X7R_04

Q46

AO3415

Q46

AO3415

G

D S

C134

0.1u_16V_X7R_04

C134

0.1u_16V_X7R_04

C671 0.1u_10V_X7R_04C671 0.1u_10V_X7R_04

R448 *4.7K_04R448 *4.7K_04

R611 *4.7K_04R611 *4.7K_04

R89

*4.7K_ 04

R89

*4.7K_ 04

R430 4.99K_1%_04R430 4.99K_1%_04

R585

4.7K_04

R585

4.7K_04

C469

0.01u_16V_X7R_04

C469

0.01u_16V_X7R_04

C689 0.1u_10V_X7R_04C689 0.1u_10V_X7R_04

C91

0.1u_10V_X7R_04

C91

0.1u_10V_X7R_04

R597

100K_04

R597

100K_04

U8

PS8338B

U8

PS8338B

PI1/SCL_CTL

1

I2C_CTL_EN

2

IN_HPD

3

IN_CA_DET

4

VDD33

5

IN_D0p

6

IN_D0n

7

PEQ

8

IN_D1p

9

IN_D1n

10

GND

11

IN_D2p

12

IN_D2n

13

PD

14

IN_D3p

15

IN_D3n

16

CEXT

17

SW

18

GND

19

REXT

20

VDD33

21

IN_DDC_SCL

22

IN_DDC_SDA

23

IN_AUXp

24

IN_AUXn

25

OUT1_AUXp_SCL

26

OUT1_AUXn_SDA

27

OUT2_AUXp_SCL

28

OUT2_AUXn_SDA

29

VDD33

30

OUT2_D3n

31

OUT2_D3p

32

OUT2_CA_DET

33

OUT2_D2n

34

OUT2_D2p

35

OUT2_D1n

36

OUT2_D1p

37

OUT2_HPD

38

OUT2_D0n

39

OUT2_D0p

40

OUT1_D3n

41

OUT1_D3p

42

OUT1_CA_DET

43

OUT1_D2n

44

OUT1_D2p

45

OUT1_D1n

46

OUT1_D1p

47

OUT1_HPD

48

OUT1_D0n

49

OUT1_D0p

50

VDD33

51

GND

52

PC21

53

PC20

54

PC11

55

PC10

56

VDD33

57

CFG1

58

CFG0

59

PI0/SDA_CTL

60

EPAD

61

R96

*4.7K_ 04

R96

*4.7K_ 04

C458 2.2u_6.3V_X5R_04C458 2.2u_6.3V_X5R_04

R90

*4.7K_ 04

R90

*4.7K_ 04

R586

4.7K_04

R586

4.7K_04

C672 0.1u_10V_X7R_04C672 0.1u_10V_X7R_04

C83 0.1u_10V_X7R_04C83 0.1u_10V_X7R_04

C93 0.1u_10V_X7R_04C93 0.1u_10V_X7R_04

R584

4.7K_04

R584

4.7K_04

C105 0.1u_10V_X7R_04C105 0.1u_10V_X7R_04

R440 *4.7K_04R440 *4.7K_04

C601 0.1u_10V_X7R_04C601 0.1u_10V_X7R_04

Loading...

Loading...