Datasheet

9

Networkin

Silicon —GD82559ER

3.2.3 S

stem and Power Mana

ement Si

nals

3.3 Local Memor

Interface Si

nals

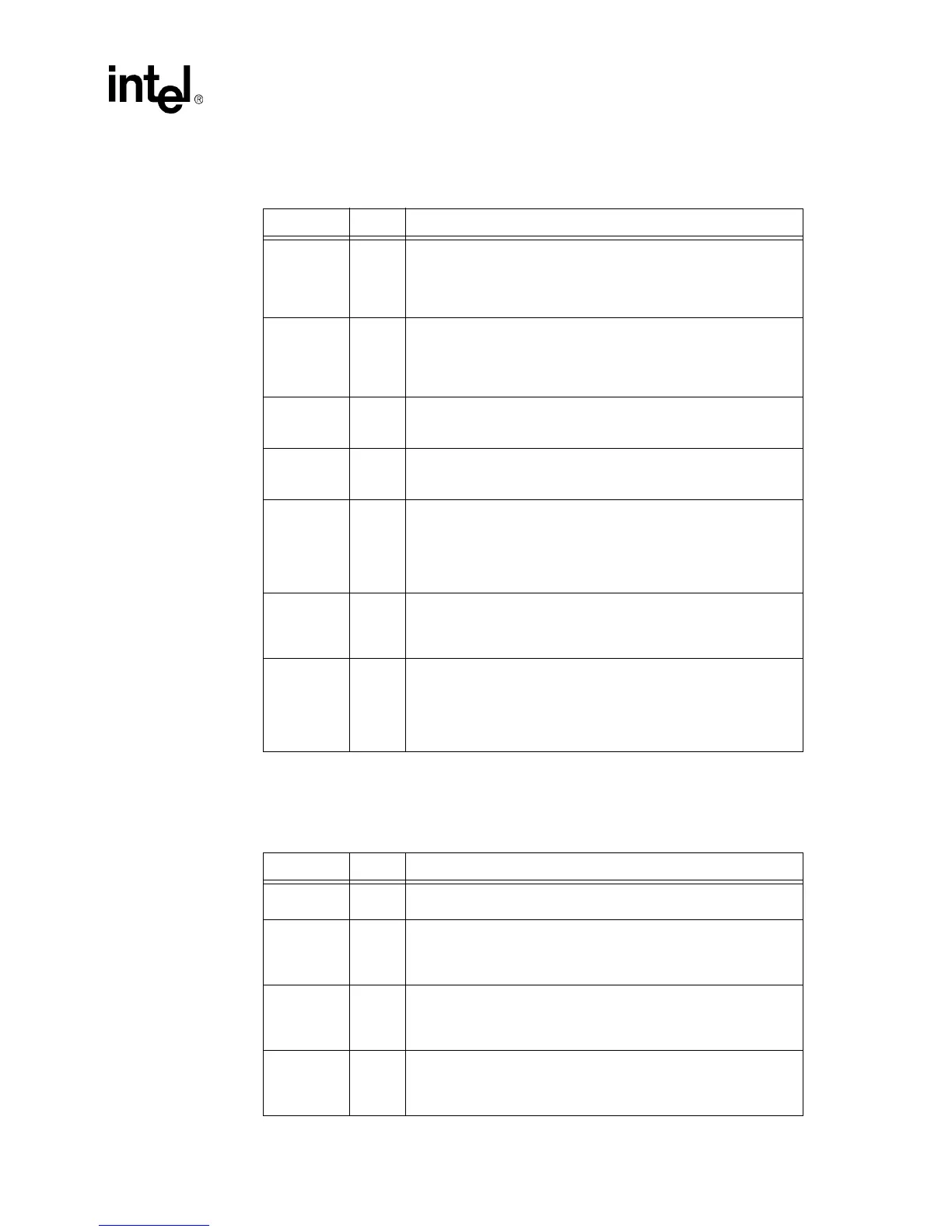

Symbol Type Name and Function

CLK IN

Clock.

The Clock si

nal provides the timin

for all PCI transactions

and is an input si

nal to ever

PCI device. The 82559ER re

uires a

PCI Clock si

nal

fre

uenc

reater than or e

ual to 16 MHz

for

nominal operation. The 82559ER supports Clock si

nal suspension

usin

the Clockrun protocol.

CLKRUN#

IN/OUT

O/D

Clockrun.

The Clockrun si

nal is used b

the s

stem to pause or slow

down the PCI Clock si

nal. It is used b

the 82559ER to enable or

disable suspension of the PCI Clock si

nal or restart of the PCI clock.

When the Clockrun si

nal is not used, this pin should be connected to

an external pull-down resistor.

RST# IN

Reset.

The PCI Reset si

nal is used to place PCI re

isters,

se

uencers, and si

nals into a consistent state. When RST# is

asserted, all PCI output si

nals will be tri-stated.

PME# O/D

Power Management Event.

The Power Mana

ement Event si

nal

indicates that a power mana

ement event has occurred in a PCI bus

s

stem.

ISOLATE# IN

Isolate.

The Isolate si

nal is used to isolate the 82559ER from the

PCI bus. When Isolate is active

low

, the 82559ER does not drive its

PCI outputs

except PME#

or sample its PCI inputs

includin

CLK

and RST#

. If the 82559ER is not powered b

an auxiliar

power

source, the ISOLATE# pin should be pulled hi

h to the bus Vcc

throu

h a 4.7K-62K resistor.

ALTRST# IN

Alternate Reset.

The Alternate Reset si

nal is used to reset the

82559ER on power-up. In s

stems that support an auxiliar

power

suppl

, ALTRST# should be connected to a power-up detection circuit.

Otherwise, ALTRST# should be tied to V

cc

.

VIO

B

IN

Voltage Input/Output.

The VIO pin is the a volta

e bias pin for the

PCI interface. This pin should be connected to 5V ± 5% in a 5 volt PCI

s

stem and 3.3 volts in a 3.3 volt PCI s

stem. Be sure to install a 10K

pull-up resistor. This resistor acts as a current limit resistor in s

stem

where the VIO bias volta

e ma

be shutdown. In this cases the

82559ER ma

consume additional current without a resistor.

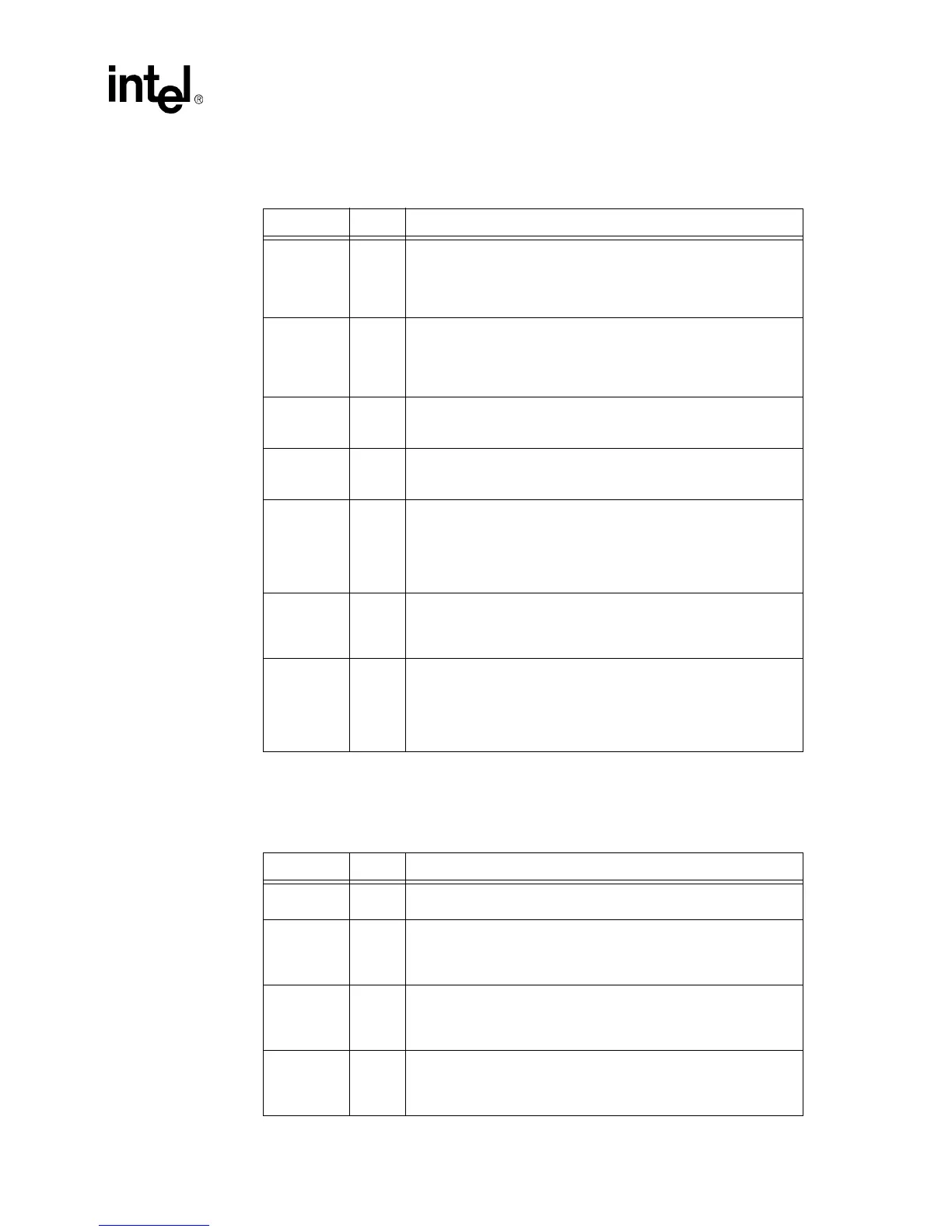

Symbol Type Name and Function

FLD[7:0] T/S

Flash Data Input/Output.

These pins are used for Flash data

interface.

FLA[16]/

CLK25

OUT

Flash Address[16]/25 MHz Clock.

This multiplexed pin is controlled

b

the status of the Flash Address[7]

FLA[7]

pin. If FLA[7] is left

floatin

, this pin is used as FLA[16]; otherwise, if FLA[7] is connected

to a pull-up resistor, this pin is used as a 25 MHz clock.

FLA[15]/

EESK

OUT

Flash Address[15]/EEPROM Data Output.

Durin

Flash accesses,

this multiplexed pin acts as the Flash Address [15] output si

nal.

Durin

EEPROM accesses, it acts as the serial shift clock output to

the EEPROM.

FLA[14]/

EEDO

IN/OUT

Flash Address[14]/EEPROM Data Output.

Durin

Flash accesses,

this multiplexed pin acts as the Flash Address [14] output si

nal.

Durin

EEPROM accesses, it acts as serial input data to the EEPROM

Data Output si

nal.

Loading...

Loading...