4-5

MAJOR IC INTERNAL BLOCK DIAGRAM AND PIN DESCRIPTION

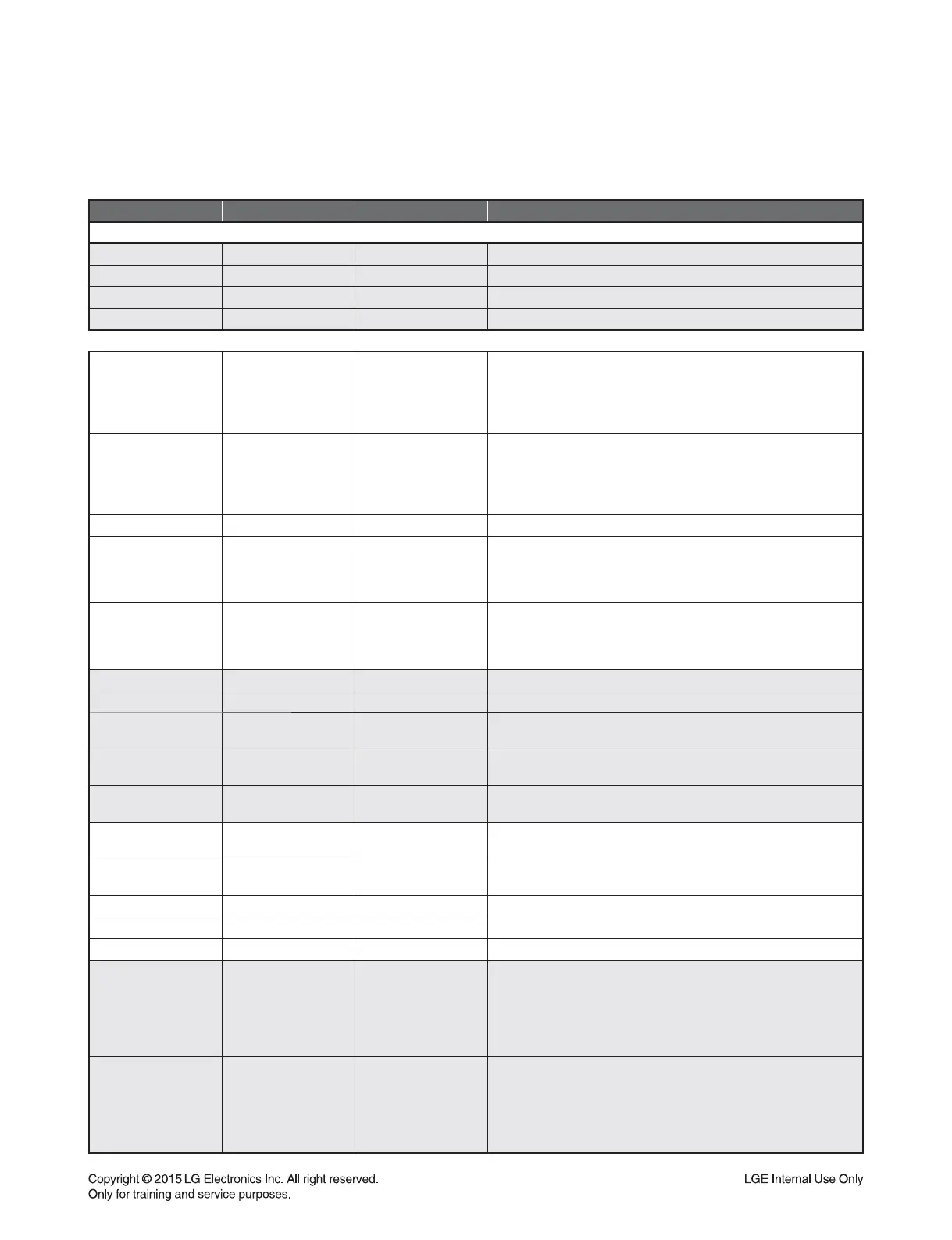

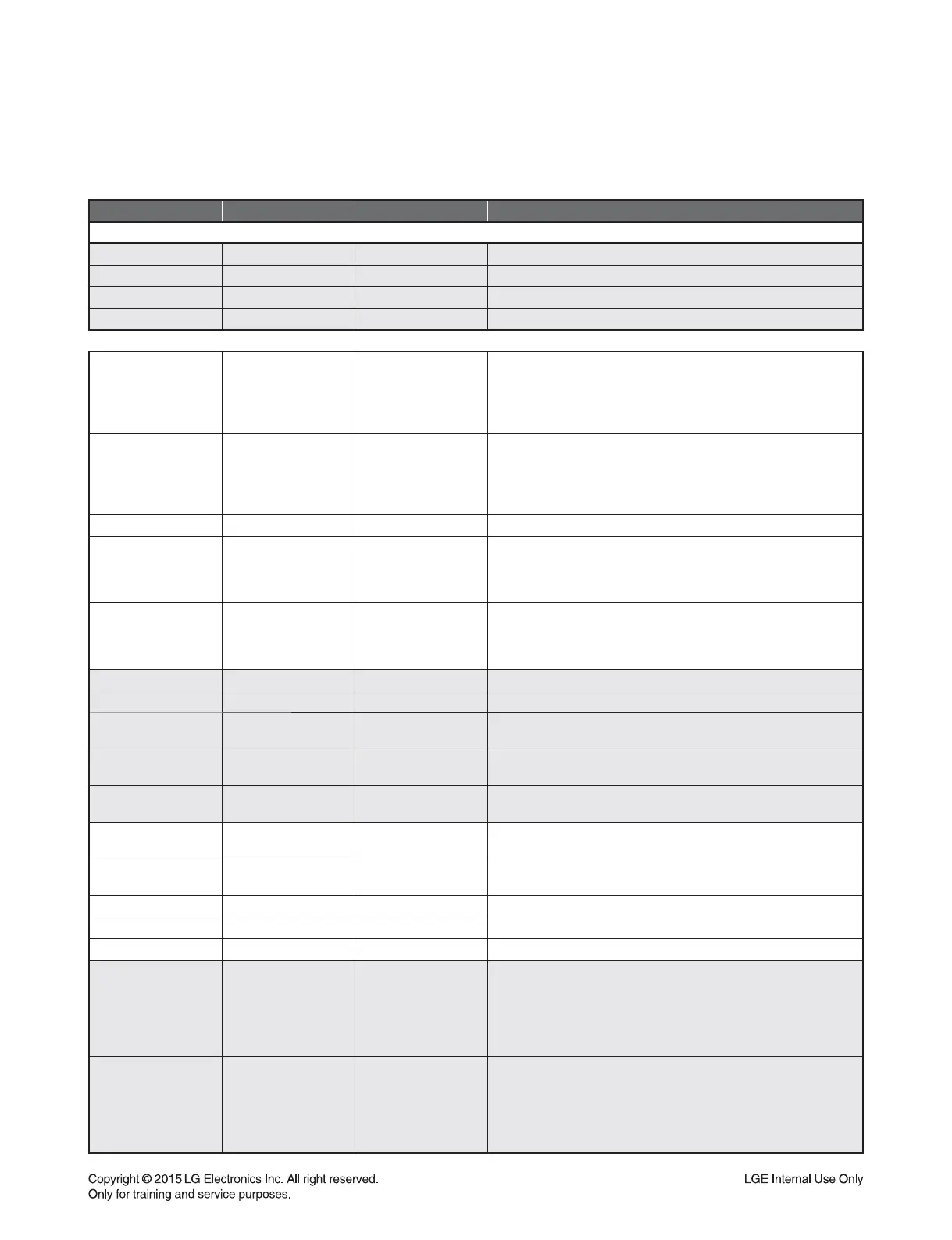

1. MT8553/ MT8563 PIN DESCRIPTION

1-1. Pin Function

PIN NO. SYMBOL TYPE DESCRIPTION

SERVO

E4 AUX1 Analog I/O Auxiliary Input. Alternateive Function : Signal Monitoring

F6 AVDD12 Analog Power(1.2V) Power Pin

D6 AVDD33_1 Analog Power(3.3V) Power Pin

E7 AVDD33_3 Analog Power(3.3V) Power Pin

K1 FECFREQ

3.3V LVTTL I/O,

5V-tolerance,

Slow slew,

2, 4, 6, 8 mA PDR,

75K pull-up (3.3 V)

Frequency selection signal output, or LDD serial interface data

or 12C SDA.

The pin is spike-free at power-on stage.

K3 FECMOD

3.3V LVTTL I/O,

5V-tolerance,

Slow slew,

2, 4, 6, 8 mA PDR,

75K pull-up (0 V)

High frequency modulation mode selection signal output,

or LDO serial interface command enable.

The pin is spike-free at power-on stage.

Multifunction: Line-in input data

L6 FEDMO Analog Output Disk motor control output. DAC output.

L2 FEEJECT_

3.3V LVTTL I/O,

5V-tolerance,

6 mA driving,

75K pull-up (3.3 V)

Eject/stop key input, active low.

The pin is spike-free at power-on stage.

Alternate function : General IO.

P4 FEFG

3.3V LVTTL I/O,

5V-tolerance,

6 mA PDR,

75K pull-up (3.3 V)

Motor Hall sensor input.

The pin is spike-free at power-on stage.

N2 FEFMO Analog Output Feed motor 1 control. DAC output.

N3 FEFMO2 Analog Output Feed motor 2 control. DAC output.

L5 FEFMO3 Analog I/O

Feed motor 3 control. DAC output.

Alternative Function : Auxiliary servo input.

L4 FEFMO4 Analog I/O

Feed motor 4 control. DAC output.

Alternative Function : Auxiliary servo input.

H3 FOO Analog Output

Focus servo output.

PDM output of focus servo compensator.

A4 FPDOCD Analog Input

Laser Power Monitor Input for CD APC / Differential negative

input

B4 FPDODVD Analog Input

Laser Power Monitor Input for DVD APC / Differential positive

input

J2 FEGAINSW1 Analog Output Read gain switch 1.

J3 FEGAINSW2 Analog Output Read gain switch 2.

P2 FEGAINSW3 Analog Output Read gain switch 3.

M2 FEGIO0

3.3V LVTTL I/O,

5V-tolerance,

2, 4, 6, 8mA PDR,

75K pull-down (0 V)

LDD serial interface data.

The pin is spike-free at power-on stage.

The pin is not allowed to pull-up in circuit layout.

Alternate function :

1. Internal monitored signal output

2. General IO

K4 FEGIO1

3.3V LVTTL I/O,

5V-tolerance,

2, 4, 6, 8 mA PDR,

75K pull-down (0 V)

LDD serial interface CLK.

The pin is spike-free at power-on stage.

The pin is not allowed to pull-up in circuit layout.

Alternate function :

1. Internal monitored signal output

2. General IO

Loading...

Loading...