2 Operating Manual

Series PSS CPU/PSS1 CPU

Overview

The CPU module is the safety system's central processing unit.

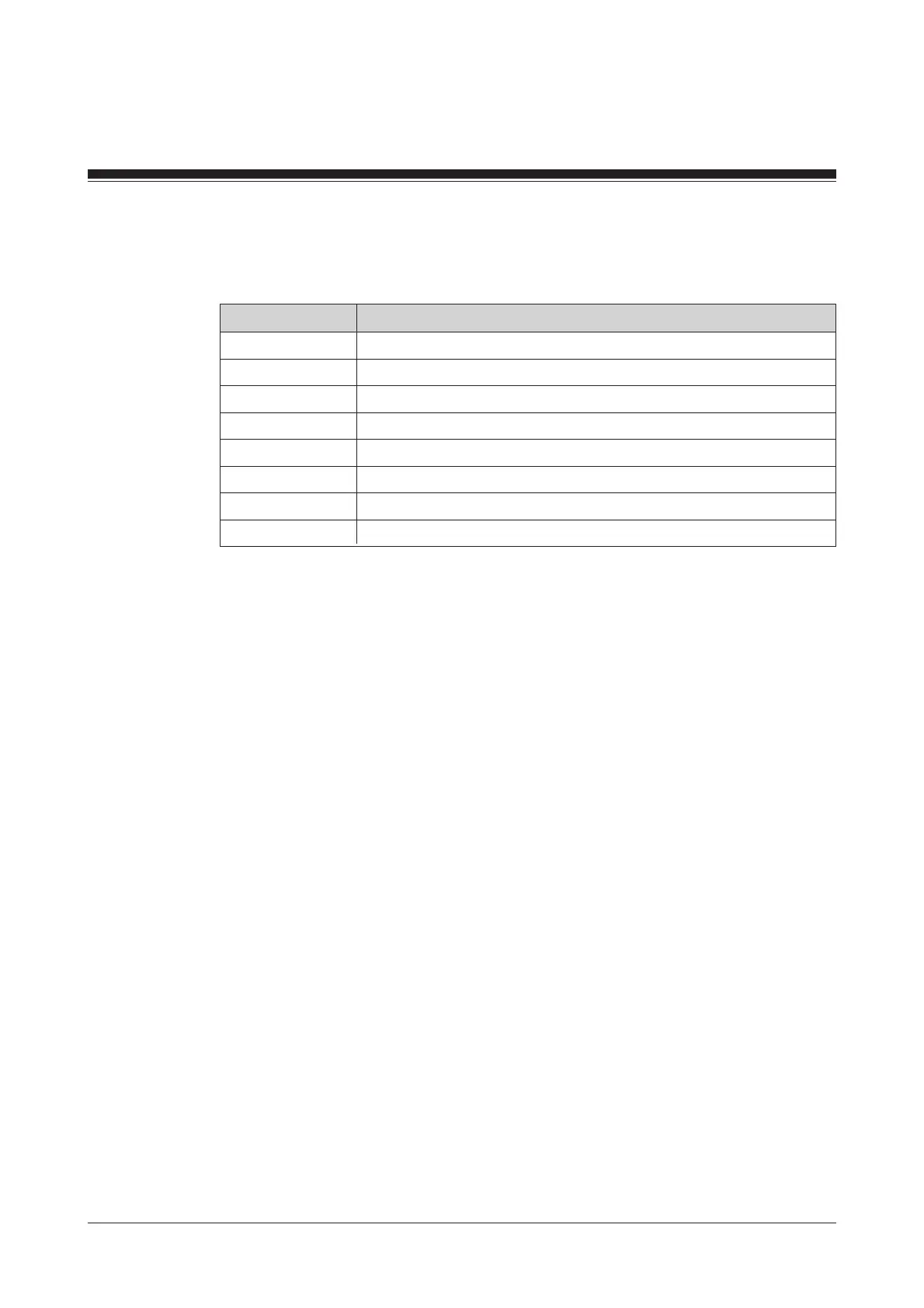

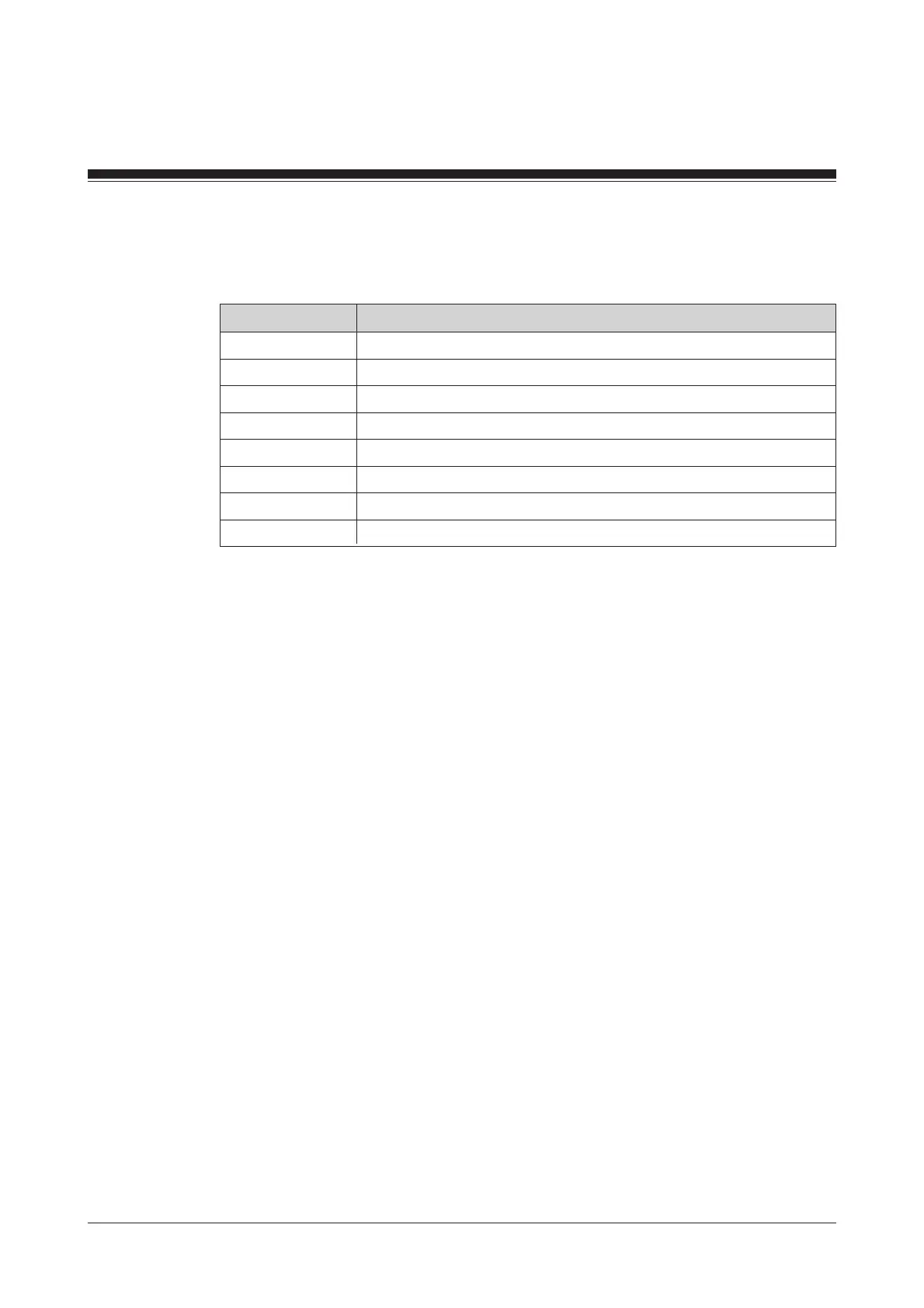

CPU Safety System

PSS CPU PSS 3000

PSS1 CPU PSS 3100

PSS CPU 2 PSS 3000

PSS1 CPU 2 PSS 3100

PSS SB CPU PSS SB 3000 (PSS 3000 with SafetyBUS p interface)

PSS1 SB CPU PSS SB 3100 (PSS 3100 with SafetyBUS p interface)

PSS SF CPU PSS SF 3000 (PSS 3000 with selective shutdown)

PSS1 SF CPU PSS SF 3100 (PSS 3100 with selective shutdown)

The CPU controls the integral on-board and, where necessary,

decentralised periphery modules. It processes and stores the user pro-

gram and variable data. The CPU is divided into a failsafe section and a

standard section.

Safety-related tasks are processed in the CPU's failsafe section. The

failsafe section is designed with three channels, i.e. three diverse

processors process the user program independently.

The standard section is designed with a single channel and processes all

the non-safety-related tasks.

A four-digit display and several LEDs provide information on the status of

the safety system and also indicate errors.

The CPU provides the following interfaces:

• PSS CPU, PSS1 CPU, PSS SB CPU, PSS1 SB CPU, PSS SF CPU,

PSS1 SF CPU:

- RS 485 programming interface

- RS 232 user interface

• PSS CPU 2, PSS1 CPU 2:

- RS232 / RS 485 programming interface

- RS 232 / RS 485 user interface

• Interface for the integral on-board periphery modules (failsafe and

standard modules)

• PSS SB CPU: SafetyBUS p interface for the decentralised periphery

modules (failsafe modules) and for the decentralised networking of

several safety systems

Loading...

Loading...