Logic Instructions with Timers and Counters

31

S7-400 Instruction List

A5E00267845-01

Logic Instructions with Timers and Counters

Examining the status of the addressed timer/counter and gating the result with the RLO according to the appropriate logic function.

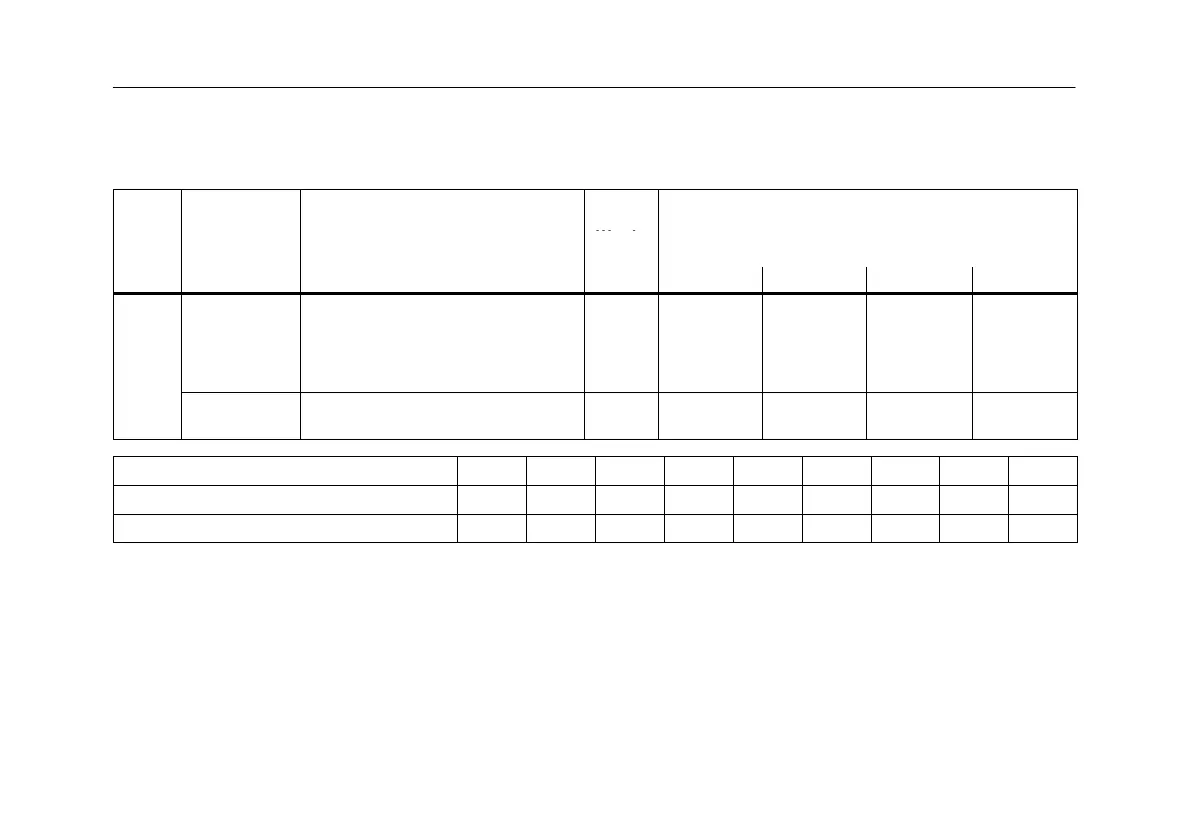

In-

Length

in

struc-

tion

Address ID Description

Words

CPU 412 CPU 414 CPU 416 CPU 417

A/AN

Tf

T [e]

Cf

C [e]

AND/AND NOT

Timer

Timer, memory-indirect addressing

Counter

Counter, memory-indirect addressing

1*/2

2

1*/2

2

0.1/0.125

0.1+

0.1/0.125

0.1+

0.06/0.075

0.06+

0.06/0.075

0.06+

0.04/0.05

0.04+

0.04/0.05

0.04+

0.03/0.042

0.03+

0.03/0.042

0.03+

Timerpara.

Counter para.

Timer/counter (addressing via param-

eter)

2 0.1+

0.1+

0.06+

0.06+

0.04+

0.04+

0.03+

0.03+

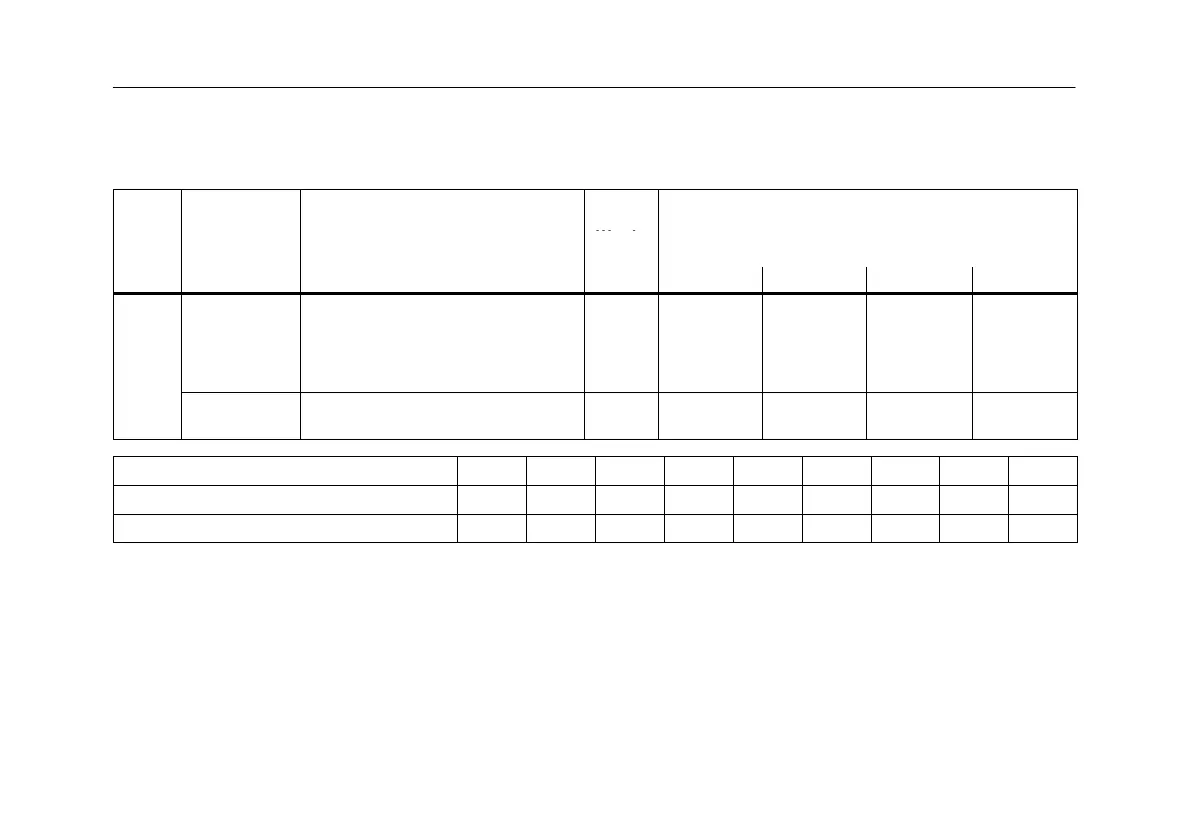

Status word for: A, AN BR CC1 CC0 OV OS OR STA RLO /FC

Instruction evaluates: – – – – – Yes – Yes Yes

Instruction affects: – – – – – Yes Yes Yes 1

+ Plus time required for loading the address of the instruction (see page 20)

*

)

With direct instruction addressing ;Address area 0 to 255

Loading...

Loading...