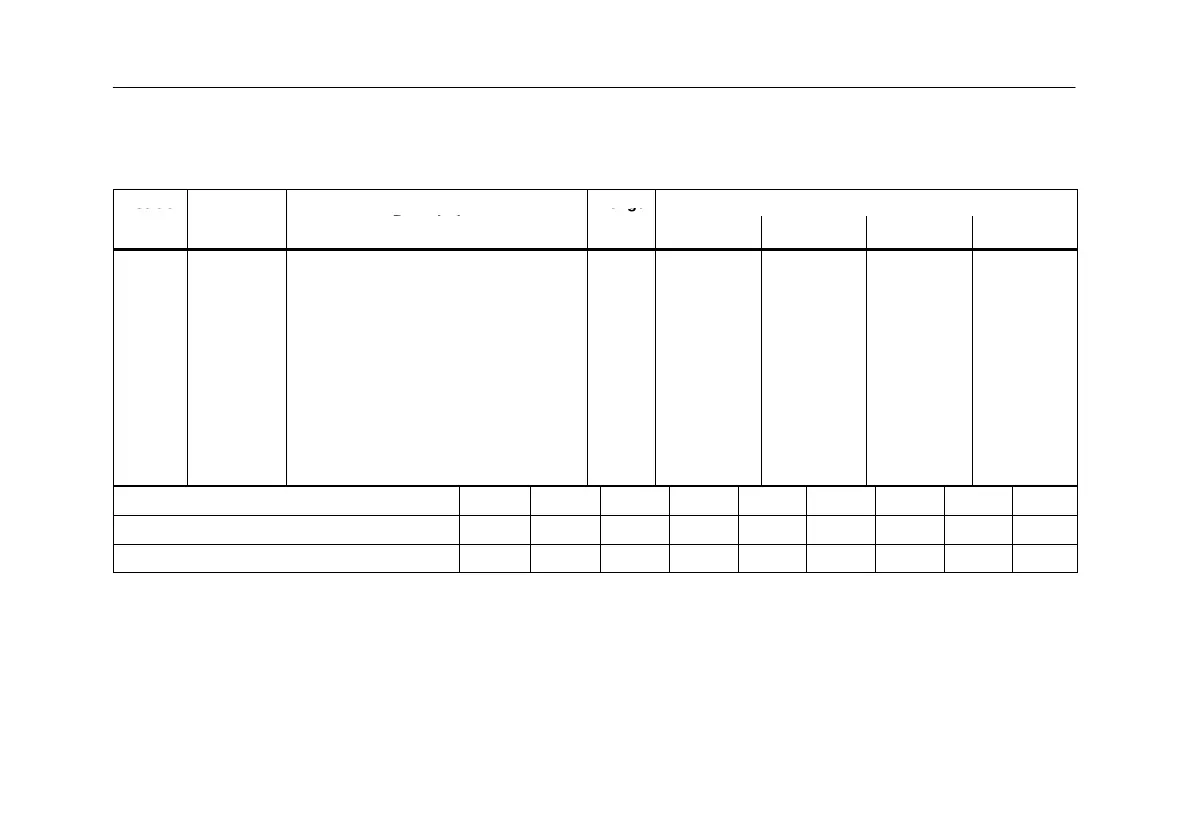

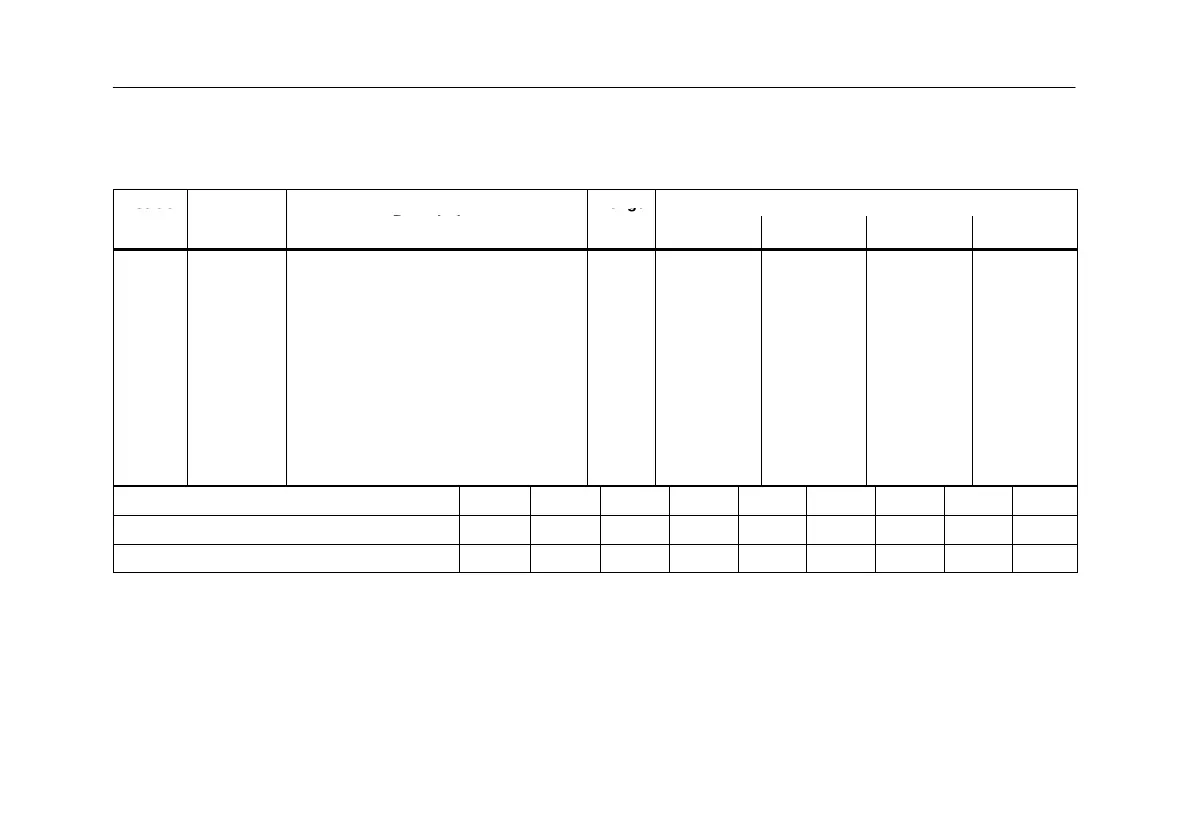

Setting/Resetting Bit Addresses

39

S7-400 Instruction List

A5E00267845-01

Setting/Resetting Bit Addresses

Assigning the value “1” or “0” to the addressed instruction when RLO = 1. The instructions can be dependent on the MCR (see page 97).

tion

ID

Description

h in

Words

CPU 412 CPU 414 CPU 416 CPU 417

S

R

I/Q a.b

M a.b

L a.b

DBX a.b

DIX a.b

c [d]

c [AR1,m]

c [AR2,m]

[AR1,m]

[AR2,m]

Parameter

Set addressed bit to “1”

Set addressed bit to “0”

Input/output

Bit memory

Local data bit

Data bit

Instance data bit

Memory-indirect, area-internal

***

Register-indirect, area-internal (AR1)

***

Register-indirect, area-internal (AR2)

***

Area-crossing (AR1)

***

Area-crossing (AR2)

***

Via parameter

1*/2

1**/2

2

2

2

2

2

2

2

2

2

0.2

0.2

0.2

0.3

0.3

0.2+/0.3+

0.2+/0.3+

0.2+/0.3+

0.2+/0.3+

0.2+/0.3+

0.2+/0.3+

0.12

0.12

0.12

0.18

0.18

0.12+/0.18+

0.12+/0.18+

0.12+/0.18+

0.12+/0.18+

0.12+/0.18+

0.12+/0.18+

0.08

0.08

0.08

0.12

0.12

0.08+/0.12+

0.08+/0.12+

0.08+/0.12+

0.08+/0.12+

0.08+/0.12+

0.08+/0.12+

0.06

0.06

0.06

0.12

0.12

0.06+/0.12+

0.06+/0.12+

0.06+/0.12+

0.06+/0.12+

0.06+/0.12+

0.06+/0.12+

Status word for: S, R BR CC1 CC0 OV OS OR STA RLO /FC

Instruction evaluates: – – – – – – – Yes –

Instruction affects: – – – – – 0 Yes – 0

+ Plus time required for loading the address of the instruction (see page 20)

*)

With direct instruction addressing; Address area 0 to 127

**)

With direct instruction addressing; Address area 0 to 255

***)

I, Q, M, L / DB, DI

Loading...

Loading...