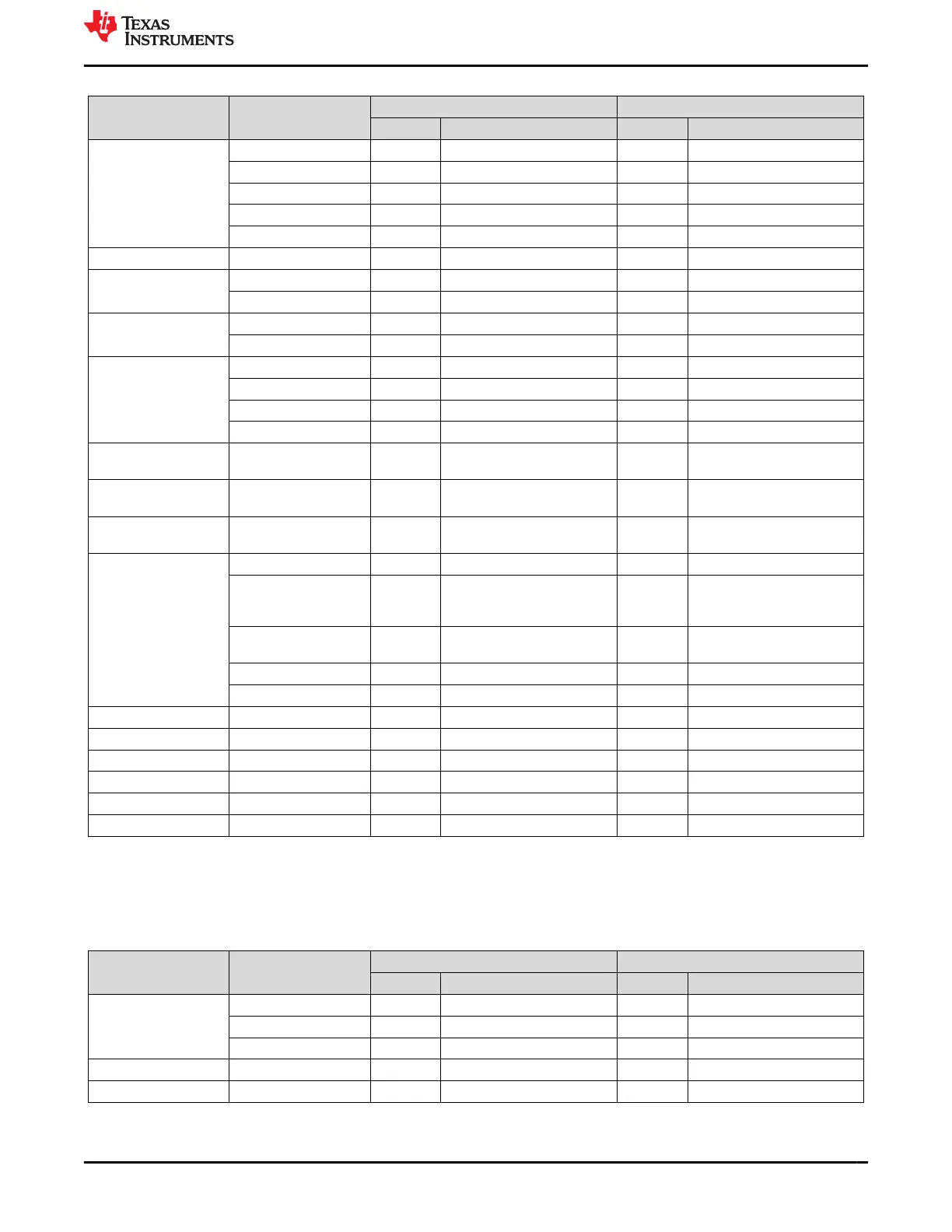

Table 5-10. Miscellaneous NVM Settings (continued)

Register Name Field Name

TPS65941213-Q1 TPS65941111-Q1

Value Description Value Description

FREQ_SEL BUCK1_FREQ_SEL 0x0 2.2 MHz 0x0 2.2 MHz

BUCK2_FREQ_SEL 0x0 2.2 MHz 0x0 2.2 MHz

BUCK3_FREQ_SEL 0x0 2.2 MHz 0x0 2.2 MHz

BUCK4_FREQ_SEL 0x0 2.2 MHz 0x0 2.2 MHz

BUCK5_FREQ_SEL 0x0 2.2 MHz 0x0 2.2 MHz

FSM_STEP_SIZE PFSM_DELAY_STEP 0xb 0xb 0xb 0xb

LDO_RV_TIMEOUT_

REG_1

LDO1_RV_TIMEOUT 0xf 16ms 0xf 16ms

LDO2_RV_TIMEOUT 0xf 16ms 0xf 16ms

LDO_RV_TIMEOUT_

REG_2

LDO3_RV_TIMEOUT 0xf 16ms 0xf 16ms

LDO4_RV_TIMEOUT 0xf 16ms 0xf 16ms

USER_SPARE_REGS USER_SPARE_1 0x0 0x0 0x0 0x0

USER_SPARE_2 0x0 0x0 0x0 0x0

USER_SPARE_3 0x0 0x0 0x0 0x0

USER_SPARE_4 0x0 0x0 0x0 0x0

ESM_MCU_MODE_

CFG

ESM_MCU_EN 0x0 ESM_MCU disabled. 0x0 ESM_MCU disabled.

ESM_SOC_MODE_

CFG

ESM_SOC_EN 0x0 ESM_SoC disabled. 0x0 ESM_SoC disabled.

CUSTOMER_NVM_ID_

REG

CUSTOMER_NVM_ID 0x0 0x0 0x0 0x0

RTC_CTRL_2 XTAL_EN 0x0 Crystal oscillator is disabled 0x0 Crystal oscillator is disabled

LP_STANDBY_SEL 0x0 LDOINT is enabled in standby

state.

0x1 Low power standby state

is used as standby state

(LDOINT is disabled).

FAST_BIST 0x0 Logic and analog BIST is run

at BOOT BIST.

0x0 Logic and analog BIST is run

at BOOT BIST.

STARTUP_DEST 0x3 ACTIVE 0x3 ACTIVE

XTAL_SEL 0x0 6 pF 0x0 6 pF

PFSM_DELAY_REG_1 PFSM_DELAY1 0x58 0x58 0x0 0x0

PFSM_DELAY_REG_2 PFSM_DELAY2 0x9d 0x9d 0x1d 0x1d

PFSM_DELAY_REG_3 PFSM_DELAY3 0x0 0x0 0x0 0x0

PFSM_DELAY_REG_4 PFSM_DELAY4 0x0 0x0 0x0 0x0

GENERAL_REG_0 FAST_BOOT_BIST 0x0 LBIST is run during boot BIST 0x0 LBIST is run during boot BIST

GENERAL_REG_1 REG_CRC_EN 0x1 Register CRC enabled 0x1 Register CRC enabled

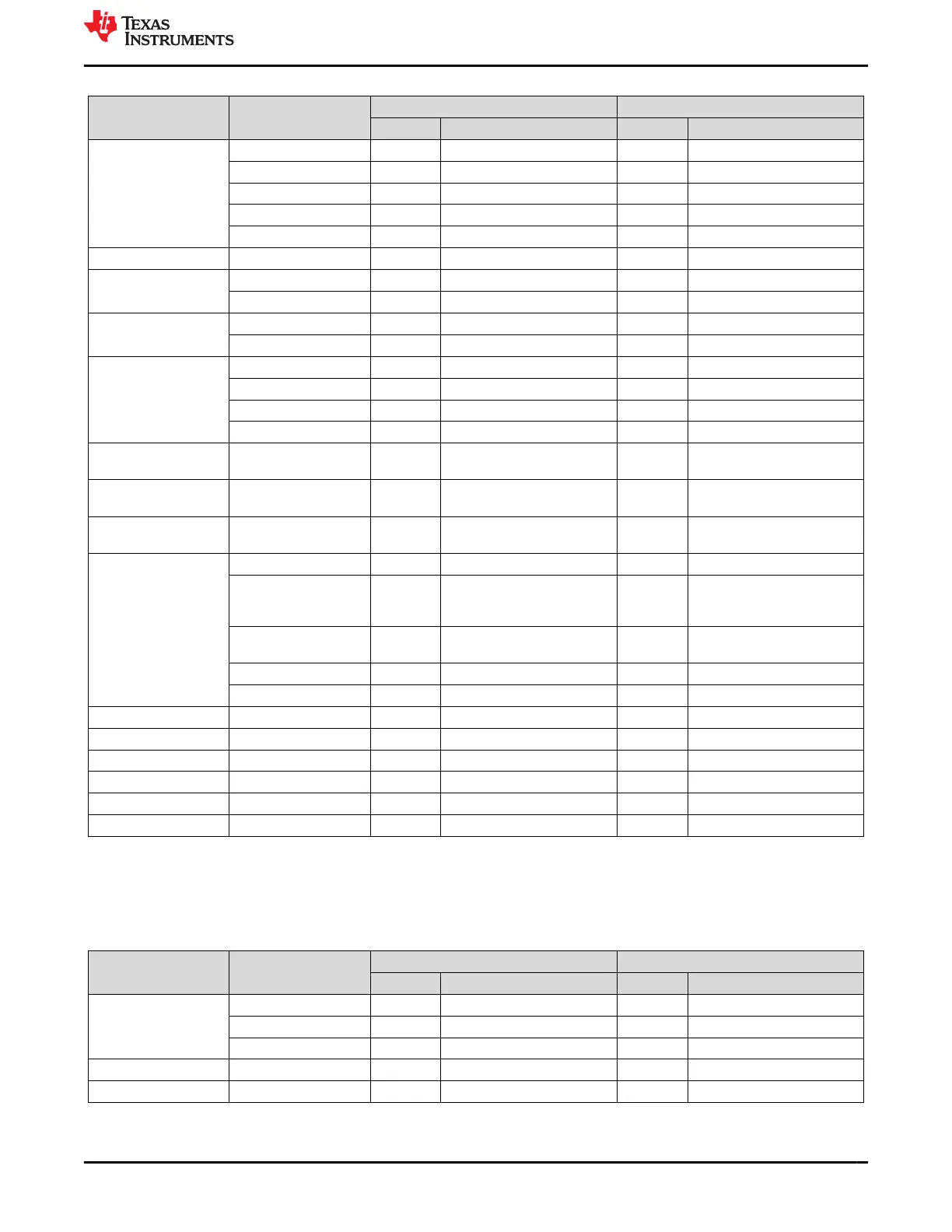

5.11 Interface Settings

These settings detail the default interface, interface configurations, and device addresses. These settings cannot

be changed after device startup.

Table 5-11. Interface NVM Settings

Register Name Field Name

TPS65941213-Q1 TPS65941111-Q1

Value Description Value Description

SERIAL_IF_CONFIG I2C_SPI_SEL 0x0 I2C 0x0 I2C

I2C1_SPI_CRC_EN 0x0 CRC disabled 0x0 CRC disabled

I2C2_CRC_EN 0x0 CRC disabled 0x0 CRC disabled

I2C1_ID_REG I2C1_ID 0x48 0x48 0x4c 0x4C

I2C2_ID_REG I2C2_ID 0x12 0x12 0x13 0x13

www.ti.com Static NVM Settings

SLVUC99 – JANUARY 2022

Submit Document Feedback

Optimized Dual TPS6594-Q1 PMIC User Guide for Jacinto

™

7 DRA829 or

TDA4VM Automotive PDN-0C

29

Copyright © 2022 Texas Instruments Incorporated

Loading...

Loading...