Table 4-1. S1 and S2: ADCIN1 and ADCIN2 Switch Settings (continued)

ADCINx Switch Settings

0 1 0 0 5

1 0 0 0 6

1 1 0 0 7

PA_HPD

LDO_3V3

GND

GND

PA_CC1

PA_CC2

PB_CC1

PB_CC2

LDO_3V3

PB_P OL

GPIO7

PA_US B3

GPIO6

ADCIN2

GND

PA_VBUS

PB_VBUS

P5V0

LDO_3V3

LDO_1V5

GND

ADCIN2

ADCIN1

PP _5V

P5V0

SYS _P WR

I2C1_SCL

I2C1_SDA

I2C1_IRQZ

I2C2_SCL

I2C2_SDA

I2C2_IRQZ

I2C3_SCL

I2C3_SDA

I2C3_IRQZ

GND

GND

PP HV

PP HV

GND

GND

A2A1

B2B1

C2

C1

D2D1

E2E1

Q1

CSD87501L

A2 A1

B2 B1

C2

C1

D2 D1

E2 E1

Q2

CSD87501L

P5V0

P5V

10.0k

R4

10.0k

R7

10.0k

R10

10k

R1

10k

R14

P3V3

P3V3

A0

1

A1

2

A2

3

VSS

4

SDA

5

SCL

6

WP

7

VCC

8

U2

CAT24C256WI-G

LDO_3V3

10.0k

R23

10.0k

R24

10.0k

R25

10.0k

R21

GND GND

10.0k

R17

10.0k

R18

10.0k

R19

I2C3_SCL

I2C3_SDA

0.1uF

C9

GND

PB_USB3

PA_P OL

PA_VBUS

PB_VBUS

63

1 8

2 7

54

S2

59.0kR22

249kR26

976kR27

GND

All Off S e tting 0

Switch 2 & 4 On Setting 2

Switch 3 & 4 On Setting 1

Switch 2 & 3 & 4 On Setting 3

Switch 3 On Setting 4

Switch 2 On Setting 5

Switch 1 On Setting 6

Switch 1 & 2 On Setting 7

LDO_3V3

ADCIN1

63

1 8

2 7

54

S1

59.0kR12

249kR13

976kR15

GND

LDO_3V3

TP1

TP2

TP3

TP4

TP5

TP6

D1

D2

10uF

C4

10uF

C5

10uF

C3

10uF

C8

1

3

56

4

2

78

J1

1uF

C48

GND

1uF

C52

GND

150pF

C49

150pF

C51

2 3

S4B

1 4

S4A

LDO_1V5

LDO_1V5

330pF

C1

330pF

C2

330pF

C7

330pF

C6

I2C3m_SDA

A1

I2C3m_SCL

A2

VSYS

A3

PA_GATE_VS YS

A4

PB_CC2

A5

GPIO2

A6

PP5V

A7

PB_VBUS

A8

I2C3m_IRQ

B1

I2C3m_SDA

B2

GPIO4

B3

PB_GATE_VS YS

B4

PB_CC1

B5

GPIO8

B6

PP5V

B7

PB_VBUS

B8

GPIO0

C1

GPIO5

C2

PP5V

C7

PB_VBUS

C8

I2C1s _IRQ

D1

I2C2s _S DA

D2

PP5V

D7

PB_GATE_VBUS

D8

I2C1s _S CL

E1

I2C2s _S CL

E2

PP5V

E7

PA_GATE_VBUS

E8

I2C1s _S DA

F1

I2C2s _IRQ

F2

PP5V

F7

PA_VBUS

F8

GPIO1

G1

LDO_1V5

G2

ADCIN2

G3

ADCIN1

G4

PA_CC1

G5

GPIO7

G6

PP5V

G7

PA_VBUS

G8

LDO_1V5

H1

GND

H2

LDO_3V3

H3

VIN_3V3

H4

PA_CC2

H5

GPIO3

H6

PP5V

H7

PA_VBUS

H8

GPIO9

C6

GPIO6

F6

TPS 65994YBG

U1

10uF

C50

GND

GND

PA_GATE_VBUS

PA_GATE_VBUS

PA_GATE_VSYS

PA_VBUS

PA_GATE_VSYS

PP HV

PB_GATE_VSYS PB_GATE_VBUS

PB_VBUS

PB_GATE_VBUS

PB_GATE_VSYS

PB_HPD

PA_DP_MODE

PB_DP_MODE

1

2

3

J10

P3V3 LDO_3V3

1

2

J12

LDO_3V3

499k

R11

40.2k

R16

499k

R20

40.2k

R28

TP14 TP15

TP17TP16

2.20k

R2

2.20k

R3

2.20k

R5

2.20k

R6

2.20k

R8

2.20k

R9

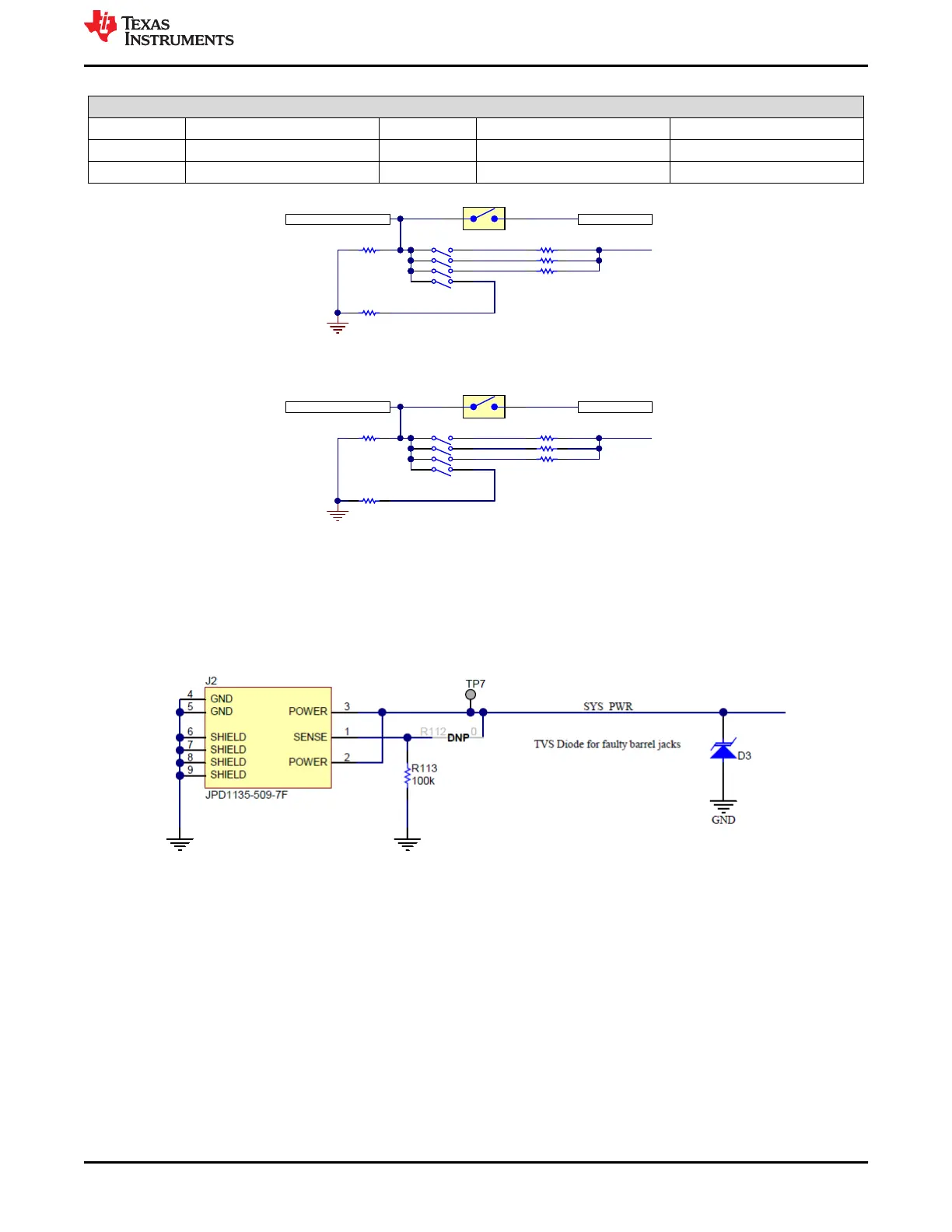

Figure 4-2. ADCIN1 and ADCIN2 Configuration Schematic

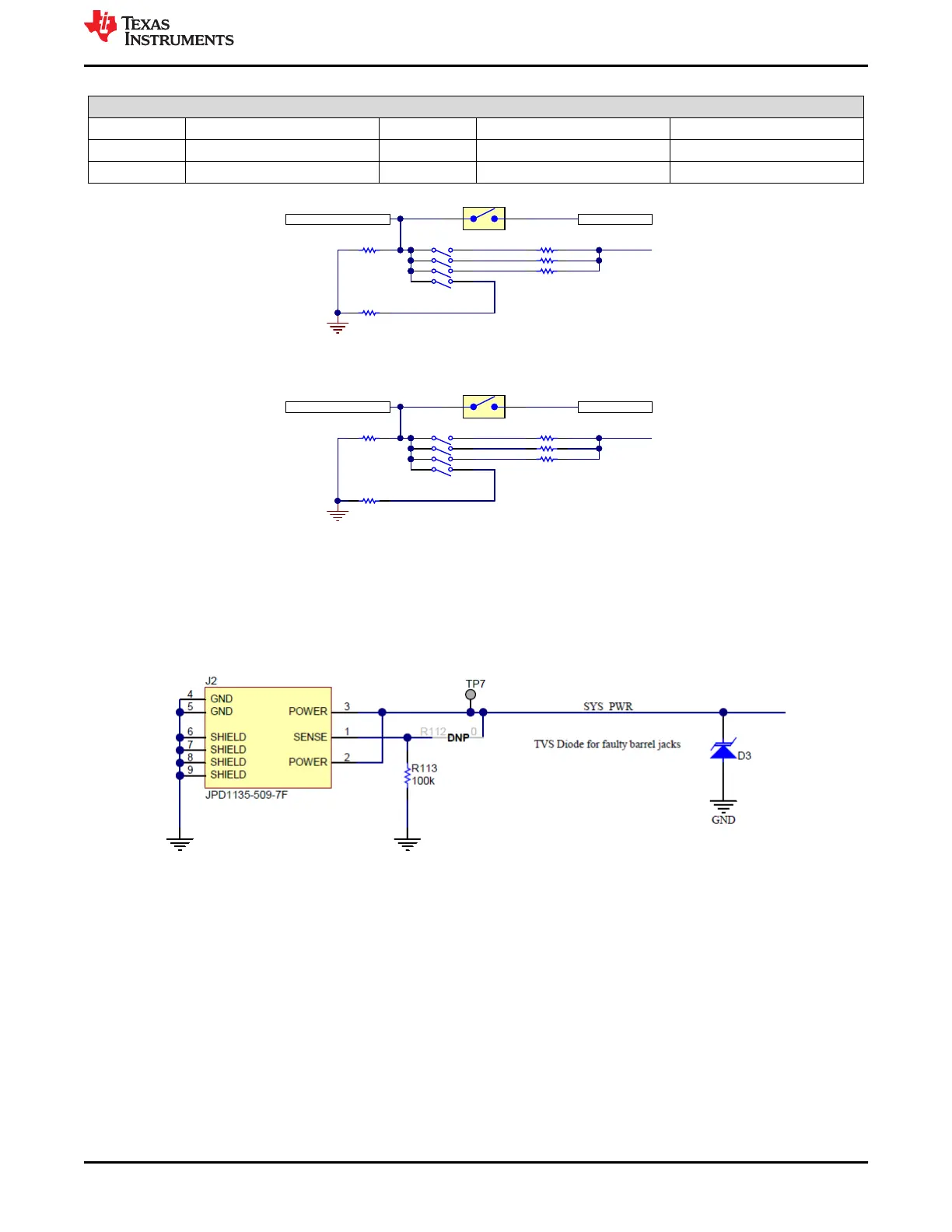

4.1.4 J2: Barrel Jack Power Connector

The barrel jack power connector accepts a 19-V to 20-V DC supply. A standard notebook adapter (or similar

adapter) provides the required power. This input provides the PP_EXT power rail 19-V to 20-V.

Figure 4-3. Barrel Jack (J2) Schematic

4.1.5 USB Type-C™ Connector (J3_PA, J3_PB)

The TPS65994 EVM has two full feature USB Type-C receptacles (port A/B) and routes VBUS, SSTX and SSRX

pairs, SBU1 and SBU2 pairs, and D+ and D– signals. The TPS65994 device can be used in self-powered and

bus-powered configurations for added flexibility. When self-powered, the EVM can provide up to 15 W (5 V, at 3

A) of power per port via the internal PP5V power path. The EVM is also capable of sinking 100 W (20 V, at 5 A)

of power via the external PP_EXT power path. The internal power path is used for sourcing power and the

external power path is used for sinking power.

www.ti.com

Setup

SLVUBM1C – JANUARY 2019 – REVISED JANUARY 2021

Submit Document Feedback

TPS65994 EVM User Guide 5

Copyright © 2021 Texas Instruments Incorporated

Loading...

Loading...