22 www.xilinx.com VC7203 IBERT Getting Started Guide

UG847 (v3.0) July 10, 2013

Chapter 1: VC7203 IBERT Getting Started Guide

Viewing GTX Transceiver Operation

After completing step 6 in Starting the SuperClock-2 Module, the IBERT demonstration is

configured and running. The status and test settings are displayed on the Links tab in the

Links window shown in Figure 1-19.

Note the line rate, TX differential output swing, and error count:

• The line rate for all four GTX transceivers is 12.5 Gb/s (see Status in Figure 1-19).

• The GTX transmitter differential output swing is preset to 250 mV.

• Verify that there are no bit errors.

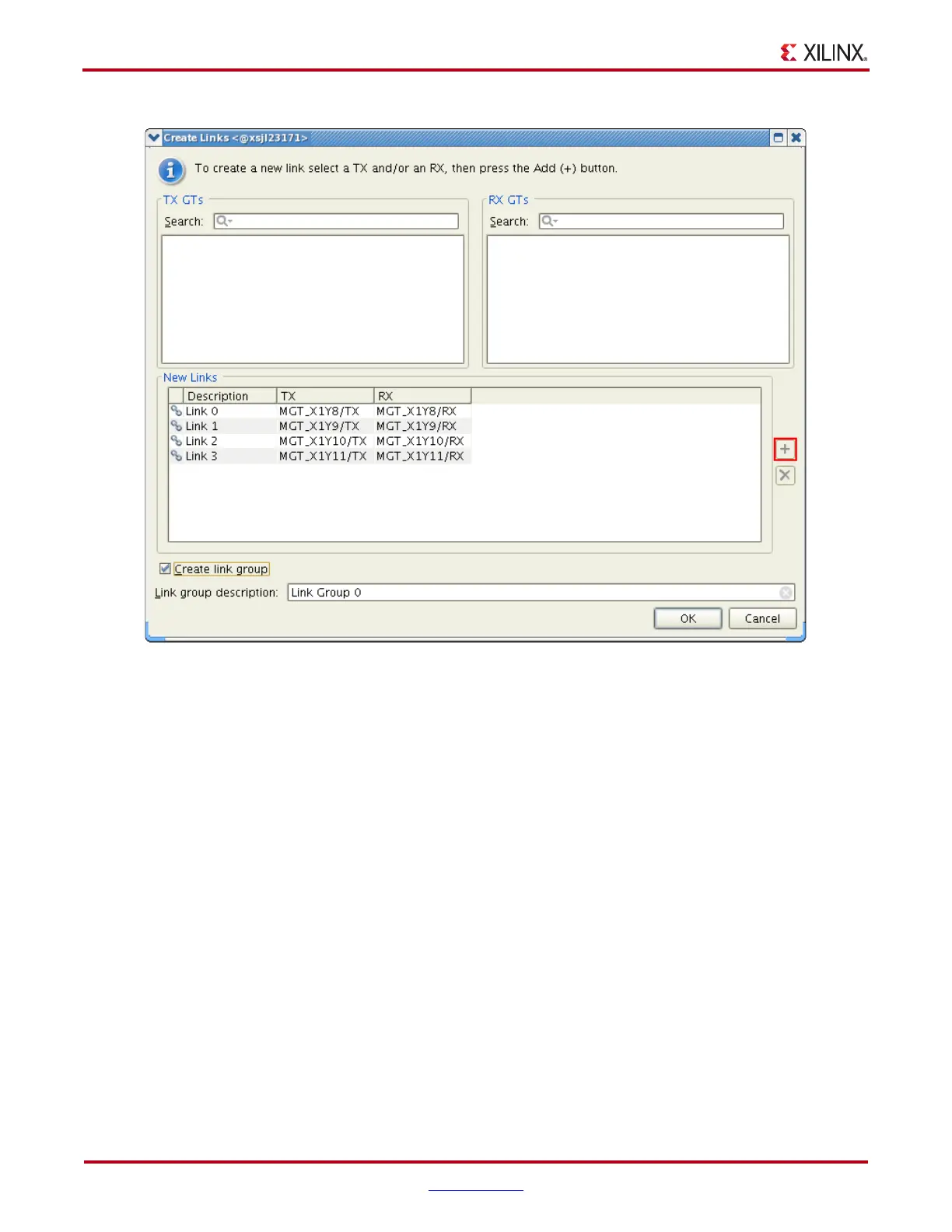

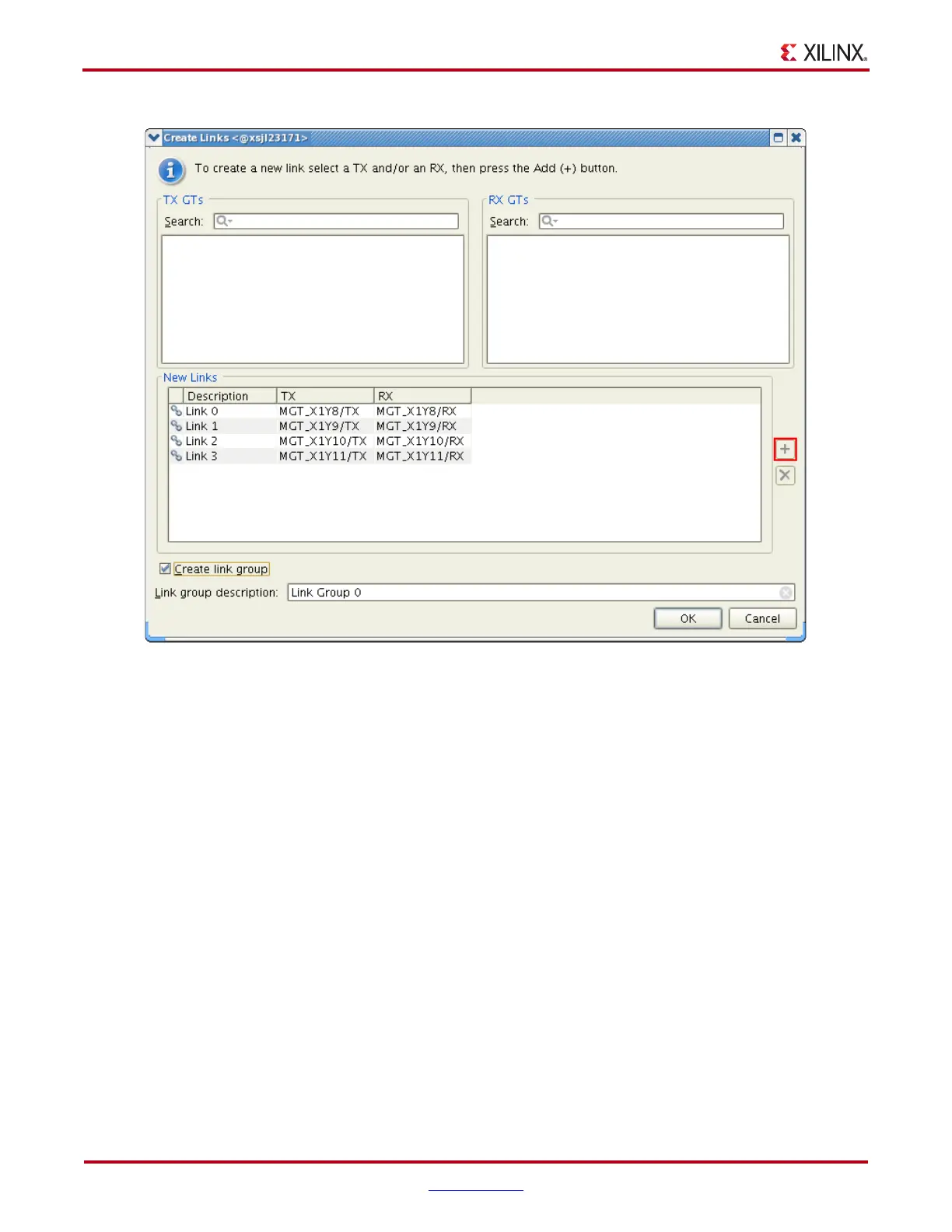

X-Ref Target - Figure 1-18

Figure 1-18: Create Links Window

Loading...

Loading...