VC7203 IBERT Getting Started Guide www.xilinx.com 23

UG847 (v3.0) July 10, 2013

SuperClock-2 Frequency Table

Additional information on the Vivado Design Suite software and IBERT core can be found

in Vivado Design Suite User Guide: Programming and Debugging (UG908

) and LogiCORE IP

Integrated Bit Error Ratio Tester (IBERT) for 7 Series GTX Transceivers Product Guide for Vivado

Design Suite (PG132

).

Closing the IBERT Demonstration

To stop the IBERT demonstration:

1. Close the Vivado Design Suite application by selecting File > Exit.

2. Place the main power switch SW1 in the off position.

SuperClock-2 Frequency Table

Table 1-2 lists the addresses for the frequencies that are programmed into the SuperClock-2

read-only-memory (ROM).

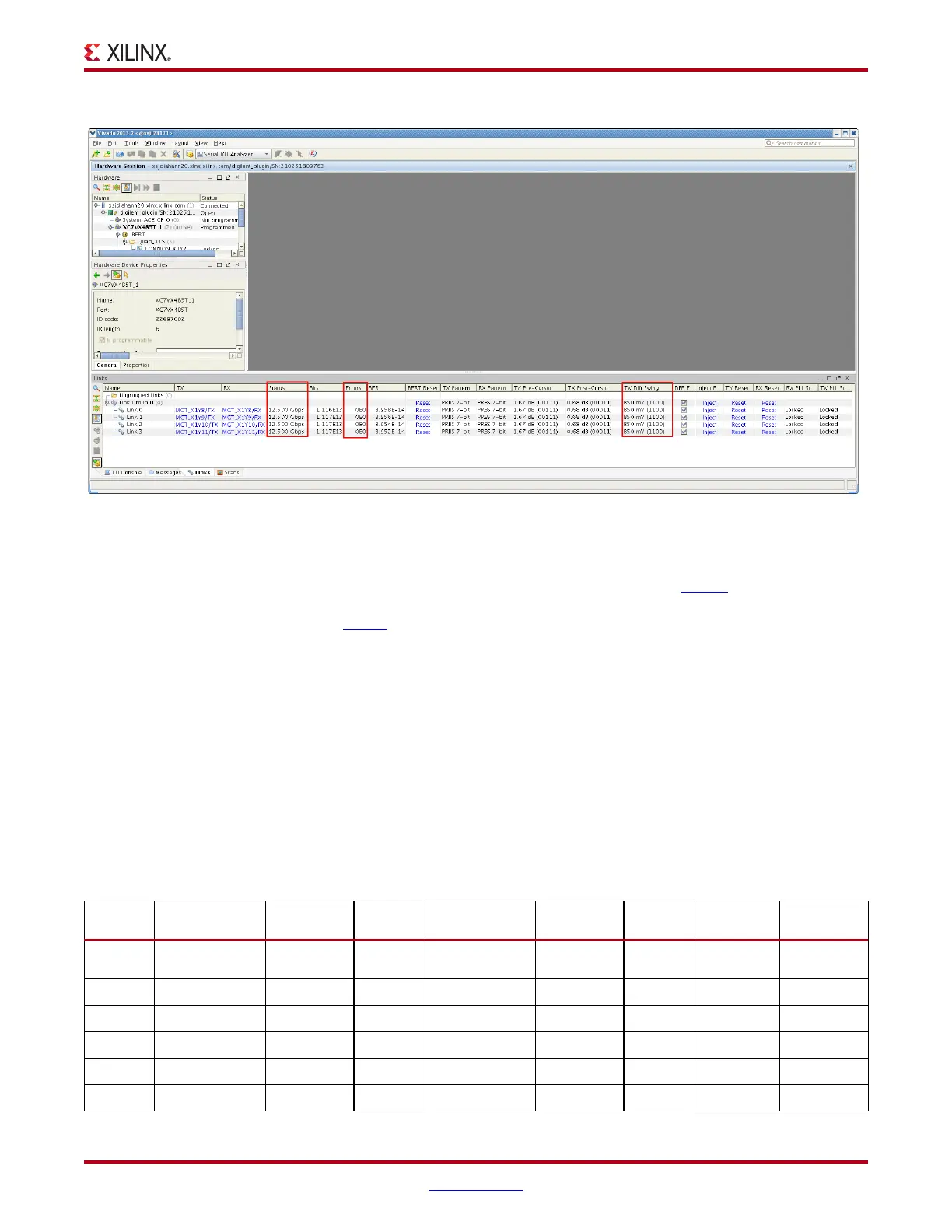

X-Ref Target - Figure 1-19

Figure 1-19: Serial I/O Analyzer Links

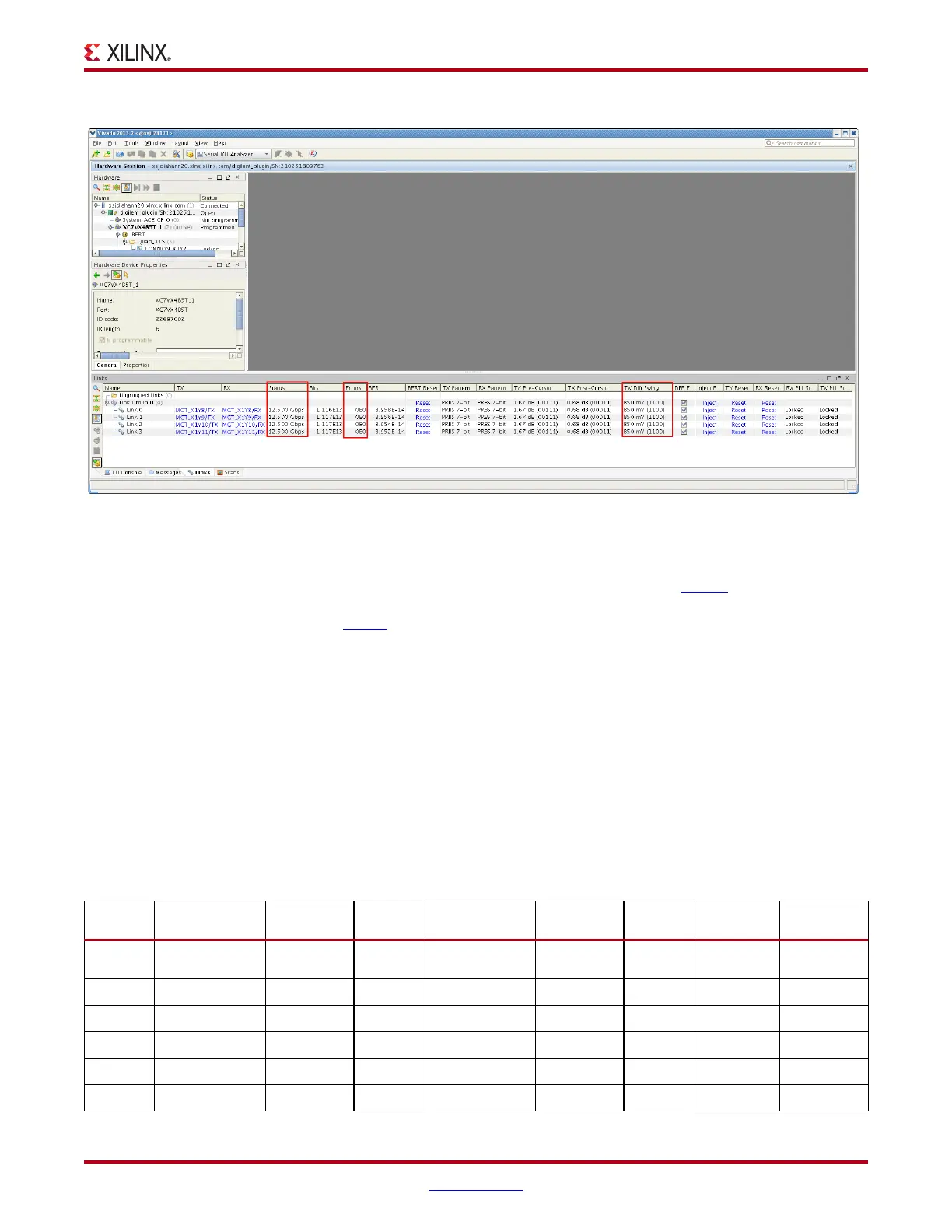

Table 1-2: Si570 and Si5368 Frequency Table

Address Protocol

Frequency

(MHz)

Address Protocol

Frequency

(MHz)

Address Protocol

Frequency

(MHz)

0

100GE/40GE/10

GE

161.130 30 OBSAI 307.200 60 XAUI 156.250

1 Aurora 81.250 31 OBSAI 614.400 61 XAUI 312.500

2 Aurora 162.500 32 OC-48 19.440 62 XAUI 625.000

3 Aurora 325.000 33 OC-48 77.760 63 Generic 66.667

4 Aurora 650.000 34 OC-48 155.520 64 Generic 133.333

5 CE111 173.370 35 OC-48 311.040 65 Generic 166.667

Loading...

Loading...