ASUS K8N-LR 4-19

MTRR Mapping [Continuous]

Sets the method used for programming CPU MTRRs when 4GB or more

memory is installed on the system. When set to Discrete, the BIOS leaves

the PCI hole below the 4GB boundary undescribed. Set to Continuous to

describe the PCI hole as non-cacheable.

Configuration options: [Continuous] [Discrete]

4.4.2 Chipset

The Chipset menu allows you to change the advanced chipset settings.

Select an item then press <Enter> to display the sub-menu.

NorthBridge Configuration

SouthBridge Configuration

Options for NB.

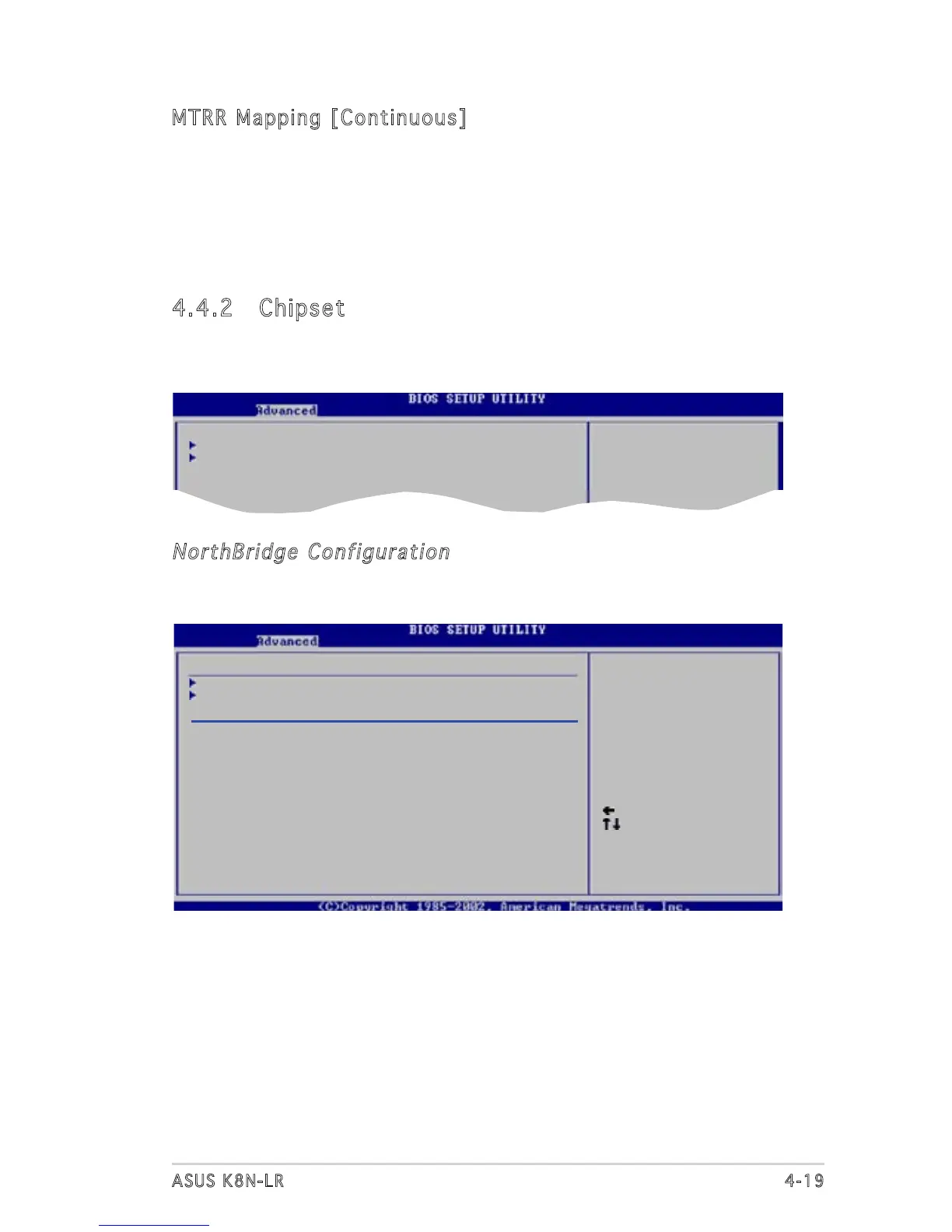

NorthBridge Configuration

The NorthBridge Configuration menu allows you to change the Northbridge

settings.

NorthBridge Chipset Configuration

Memory Configuration

ECC Configuration

Power Down Control [Auto]

Memory CLK : 200 MHz

CAS Latency (Tcl) : 3.0

RAS/CAS Delay (Trcd) : 3 CLK

Min Active RAS (Tras) : 8 CLK

Row Precharge Time (Trp) : 3 CLK

RAS/RAS Delay (Trrd) : 2 CLK

Row Cycle (Trc) : 11 CLK

Row Refresh Cycle (Trfc) : 14 CLK

Read Write Delay (Trwt) : 4 CLK

Read Preamble : 5.5 ns

Asynchronous Latency : 7 ns

Loading...

Loading...