2-15

2.4 CAMERA SYSTEM IC'S FUNCTION

2.4.1 Camera DSP (IC4301: JCY0120) function

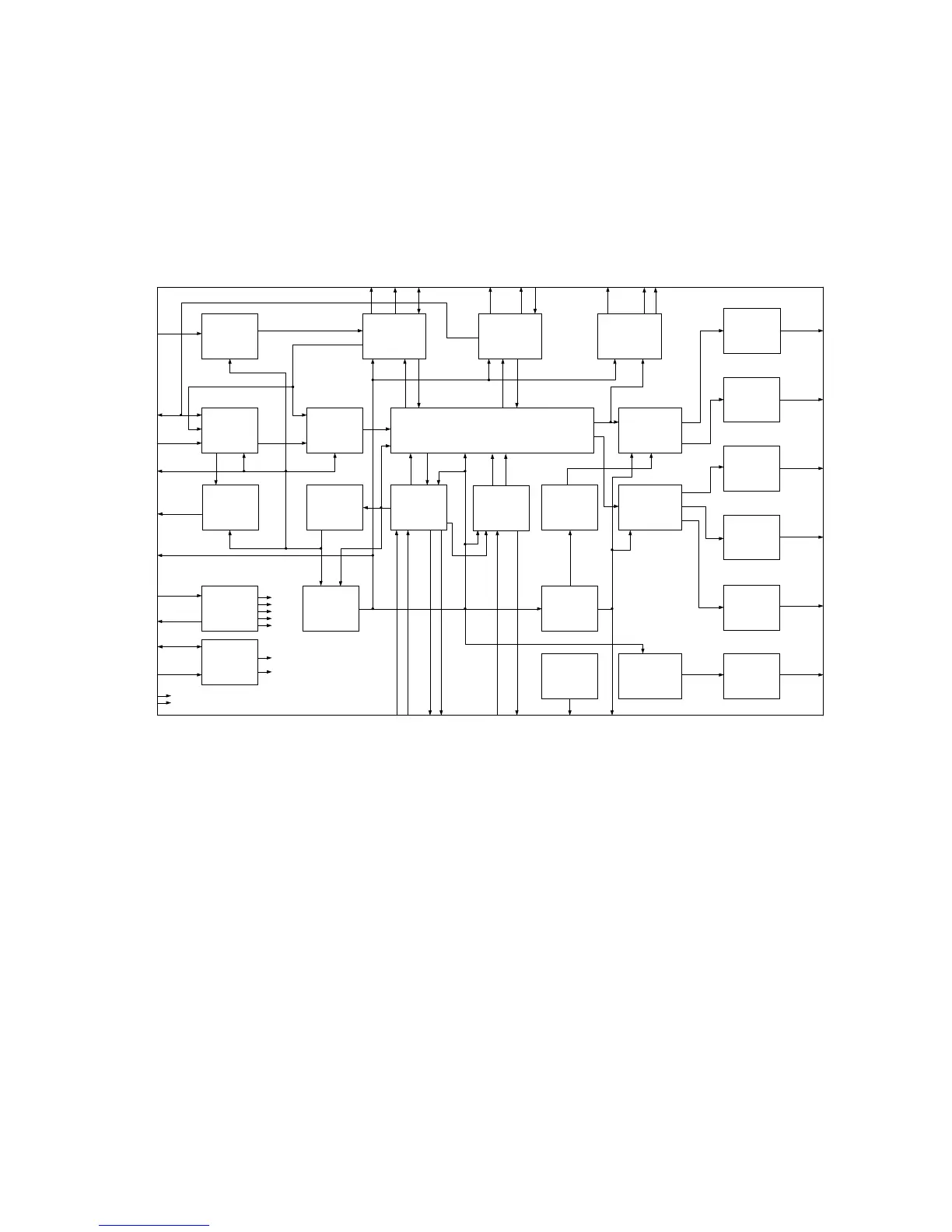

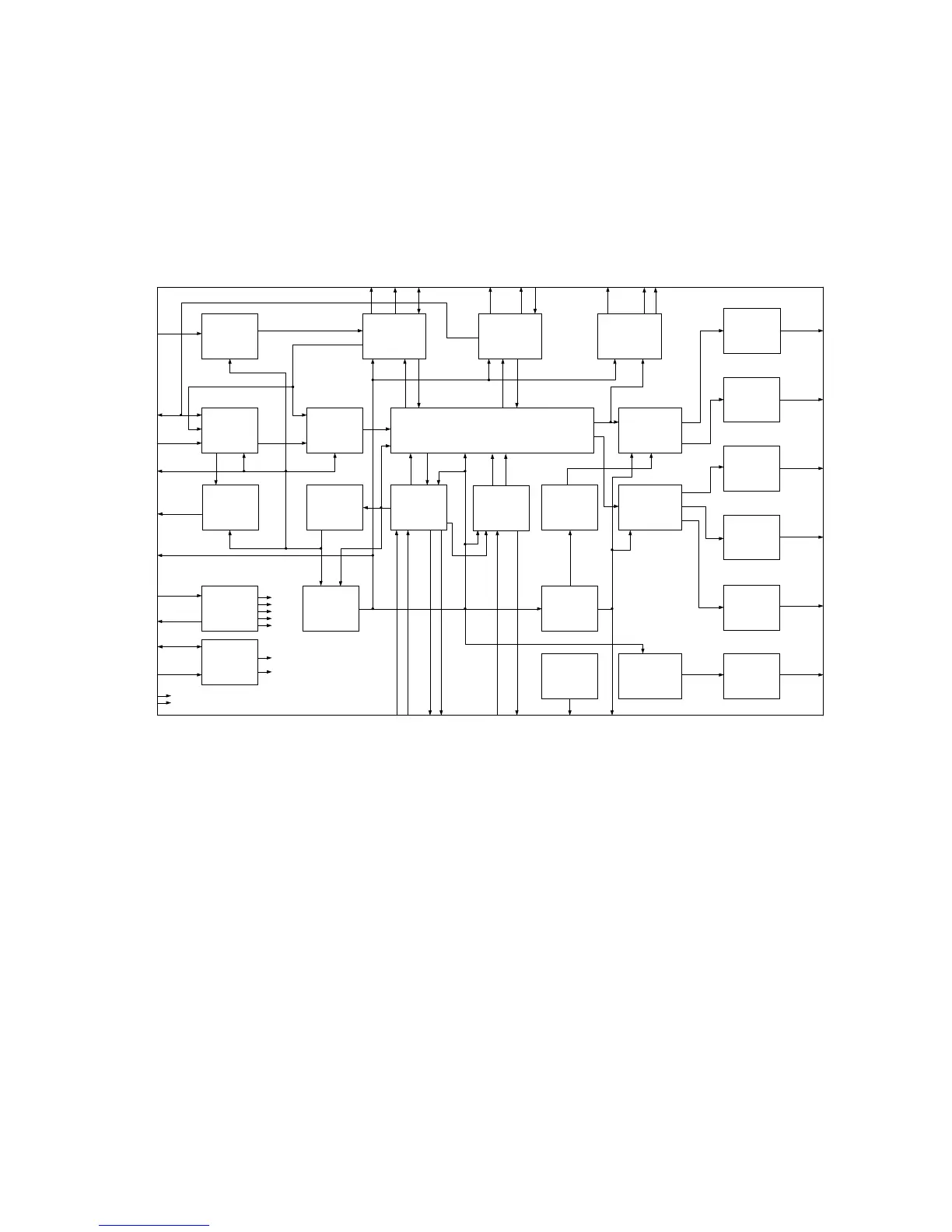

1. Camera DSP (IC4301: JCY0120) internal block diagram

CLK45

ADIN [9:0]

YO

CLR

SSG1

EIS/FMC

VRAM Contol

Vector Detect

ID

CLKYCA

CLK13

CLK13X

YOUT

SSG for TG/YCA

SSG2

CLK13

Main SSG

AUTO

CLKYCA

Auto operation

process

CLK18I

CLK13I

CLK27I

CLKGEN

Clock generate

TVSEL0

Y/C

CLKYCA

Y/C signal

process

IWD

CLK14

Frequency

converter

KIZU

White noise

compensation

SELECT

CLK13

ANA I/F

CLK13

Analog input

interface

NTSC/PAL

Color Encoder

CLKENC2

ENC

CLKENC1

CVF

CLK13

Interface for Color

Viewfer

KASHA

CLK13

Shutter sound

occurrence

D/A Converter

CLKENC1

YDAC

CO

D/A Converter

CLKENC2

CDAC

D/A Converter

CLK13

Y2DAC

Y2O

D/A Converter

CLK13

RYDAC

D/A Converter

CLK13

BYDAC

D/A Converter

KDAC

RYO

RYO

KO

BEND

PWM

AFBEND

AYO [3:0]

ACO [3:0]

COUT

Y2OUT

RYOUT

BYOUT

KOUT

CLKYCA

IRSI

HDYCA

VDYCA

FLDYCA

VBDAT

VBSTART

Test signal generator / Wipe / OSD mix

Hadamard NR / Mix / Signal select

CSYNC

HDANA

VDANA

CSYNC1

DYI [3:0]

DCI [3:0]

EOUT1 EOUT5 EOUT9

EOUT2 EOUT6 EOUT10

EOUT3 EOUT7 EOUT11

EOUT4 EOUT8 EOUT12

CLK27

INHA

INVA

ANACNT

FMY [7:0]

FMC [3:0]

TMY [7:0]

TMC [3:0]

IE1 FMRE1 FMWE1

IE2 FMRE2 FMWE2

OMT

MCLK RAD

FMWR WAD

RAE1 WAE1

RAE2 WAE2

DSC I/F

CLK13

DSC interface

FLDDSC

CLKDSC

HDDSC

VDDSC

CLKYCA

DSYO [7:0]

DSCO [7:0]

DSYI [7:0]

DSCI [7:0]

EDAC

12ch EVR DAC

ESSG

CLK13

SSG for Encoder

CBLK

CSYNC

BF

LSW

HRST4T

VRST4T

VBGEN

CLK13

VBID/WSS

Generator

YCIN

LHFO

ADYC

CLKYCA

ADKZ

HDTG

VDTG

SLEN

OSD I/F

CLK13

CLK13X

OSD Interface

DVC I/F

CLK13

DVC Interface

CLK27

DVSL SLDV

SLCV

FMSLSLFMDSSLSLDS

VBLK0

BLK10

BLK20

OSY_V OSY_1

OSR_V OSY_2

OSB_V

DYO [3:0]

DCO [3:0]

INH

INV

OUTH

OUTV

VR VBLK

VG BLK1

VB BLK2

VC1

VC2

HDOSD

VDOSD

CLKOSD

HDANA13

VDANA13

HDFMC

VDFMC

FLDFMC

OUTH13

OUTV13

CLKYCA

CLK13

CLK13X

CLKENC1

CLKENC2

RE DSTB

LWE HWE

CS RWSEL

ALE USEL0

USEL1

BUS [15:0]

CPU I/F

CPU Interface

CONTROL SINGNAL

DBI[15:0]

VDMDA

HDCPU VDCPU

FRP FLDCPU

Fig. 2-4-1 Camera DSP (IC4301: JCY0120) internal block diagram

Loading...

Loading...