Chapter 3 Register Map and Descriptions

PCI E Series RLPM 3-18

©

National Instruments Corporation

DAC FIFO Data Register

The DAC FIFO Data Register is used to load the desired data into the DAC data FIFO.

The DAC FIFO is 2 kwords deep on the PCI-MIO-16E-1, PCI-MIO-16XE-10, PCI-6031E,

and PCI-6071E. The DAC FIFO is 512 words deep on the PCI-MIO-16E-4. The DAC FIFO

is 0 words deep on the PCI-MIO-16XE-50. The empty, half-full, and full flags from the 2

kword and 512 word DAC data FIFO are available in a status register in the DAQ-STC. These

flags indicate when the FIFO is empty, half-full, or full, respectively. Only the full flag is

available on the boards with the 0 word deep DAC data virtual FIFO. Whenever the FIFO is

not full the host is free to write additional data.

Address: Base address + 1E (hex)

Type: Write-only

Word Size: 16-bit

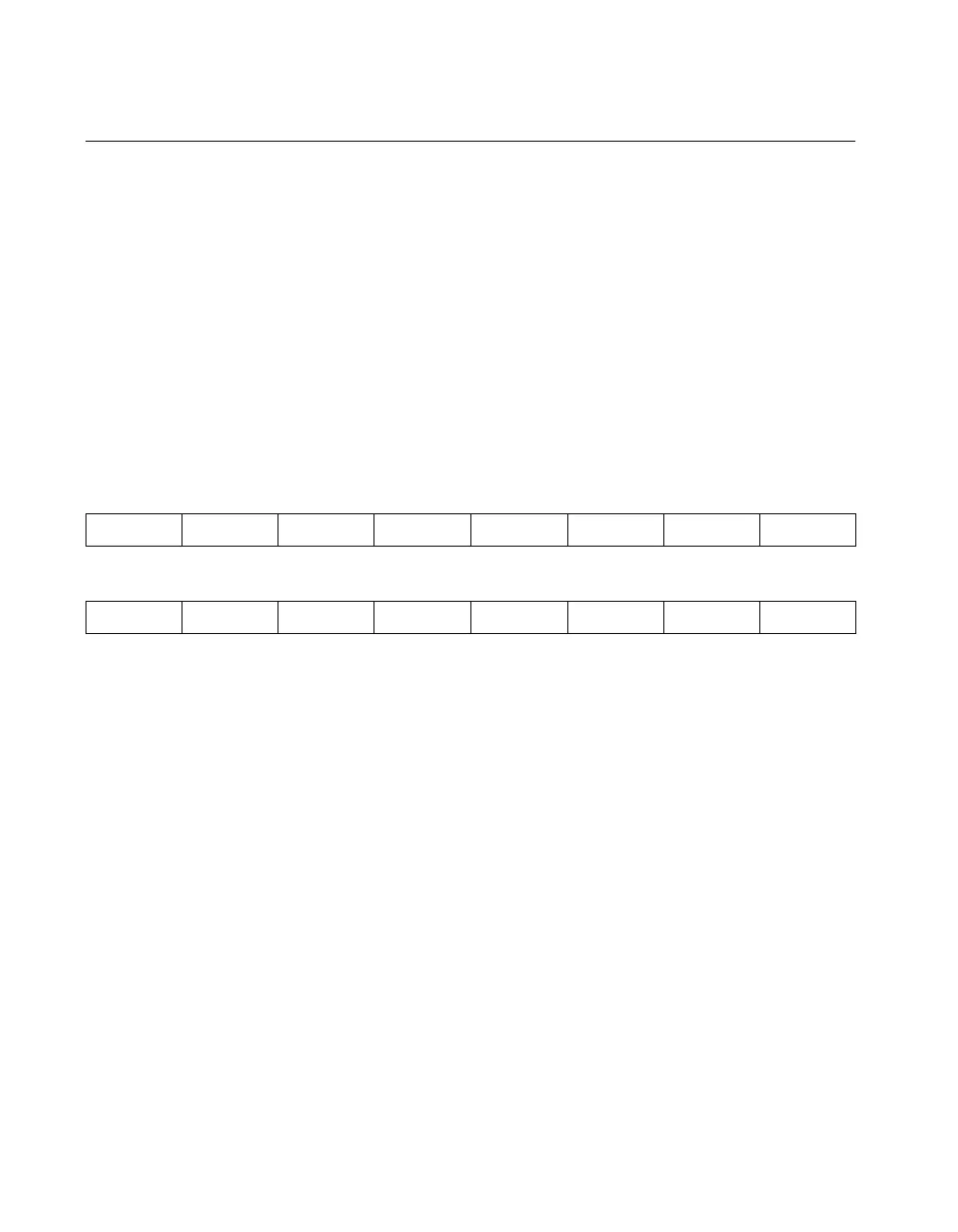

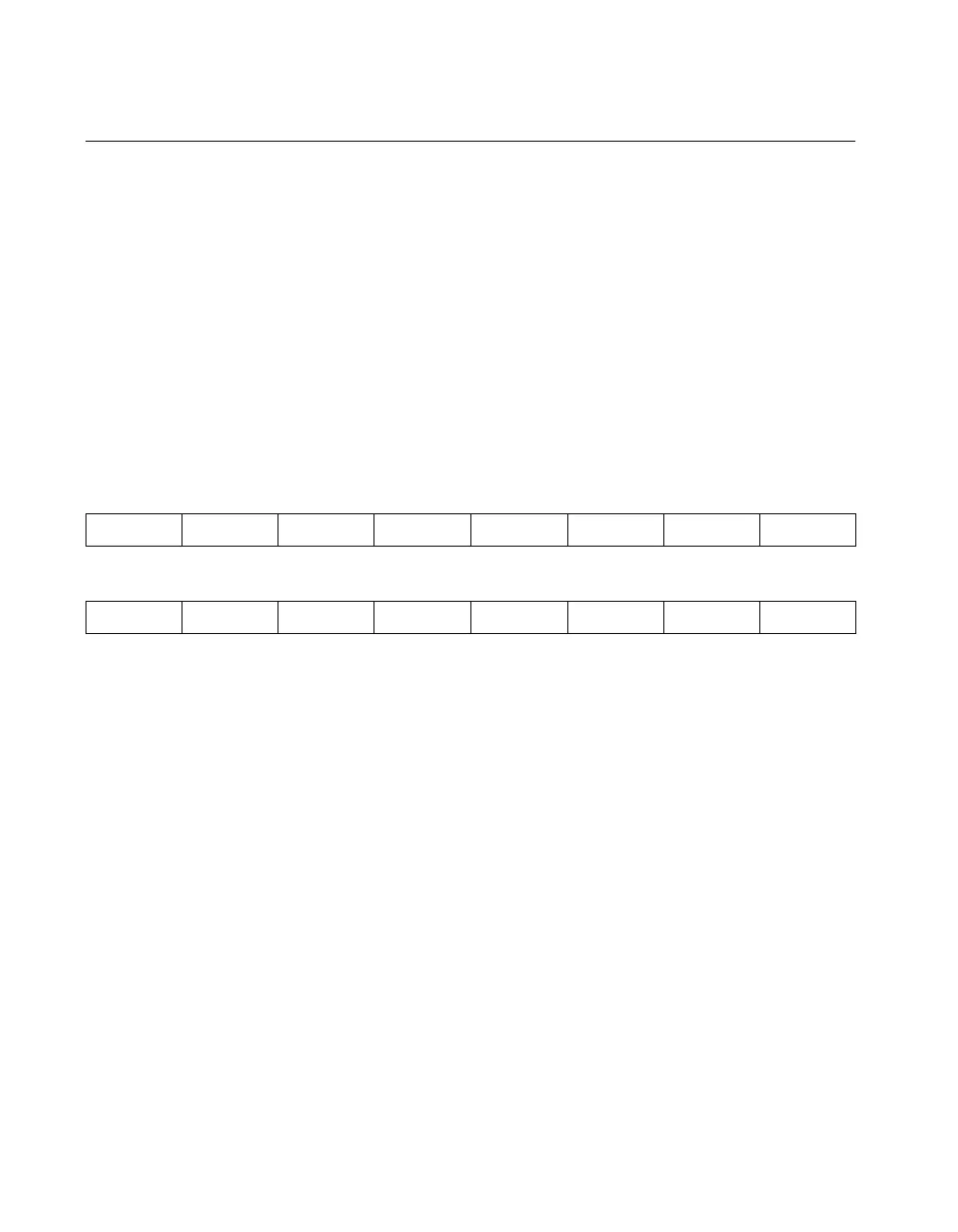

Bit Map:

Bit Name Description

15–0 D<15..0> Data bits 15 through 0—The data to be written to the DAC

data FIFO. This data is interpreted in straight binary form

when DAC is configured for unipolar operation. In

unipolar mode, the valid range is 0 to 65,536 for a 16-bit

DAC and 0 to 4,096 for a 12-bit DAC. When the DAC is

configured for bipolar operation, the data is interpreted in

two’s complement form. In bipolar mode, the valid range

is –32,768 to 32,767 for a 16-bit DAC and –2,048 to 2,047

for a 12-bit DAC.

15 14 13 12 11 10 9 8

D15 D14 D13 D12 D11 D10 D9 D8

7 6 5 4 3 2 1 0

D7 D6 D5 D4 D3 D2 D1 D0

Loading...

Loading...