in the subcategory “Multicore” to rzn1s_demo_board_eb.

5. Compile the project via “Project/Compile” or “Project/Rebuild all”.

6. Press the “Download and debug” button or Ctrl+D

This will cause IAR to open the slave workspace as an additional IAR workbench instance, build

the slave project and load both – the master and the slave project – to the board sharing the

debugger.

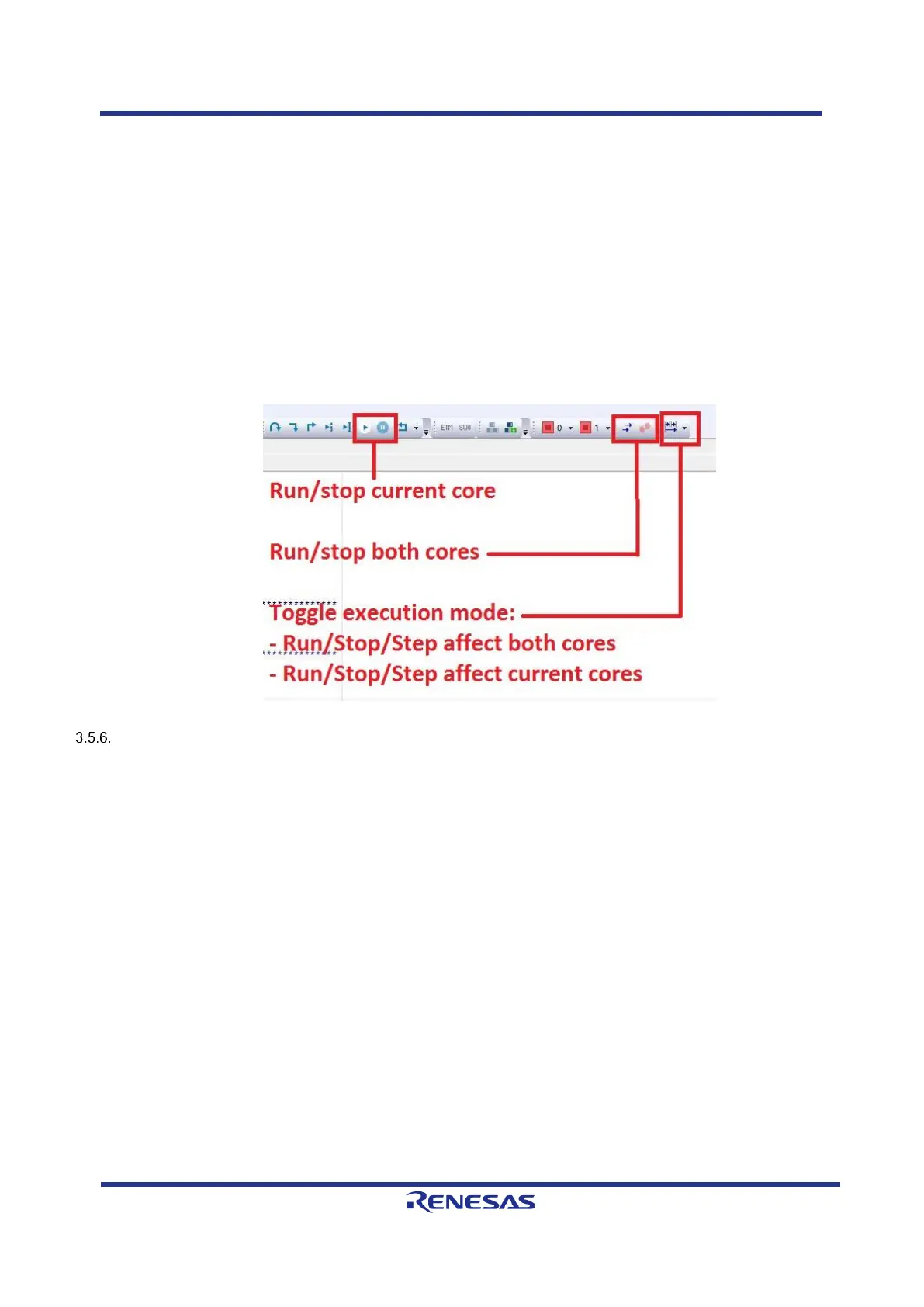

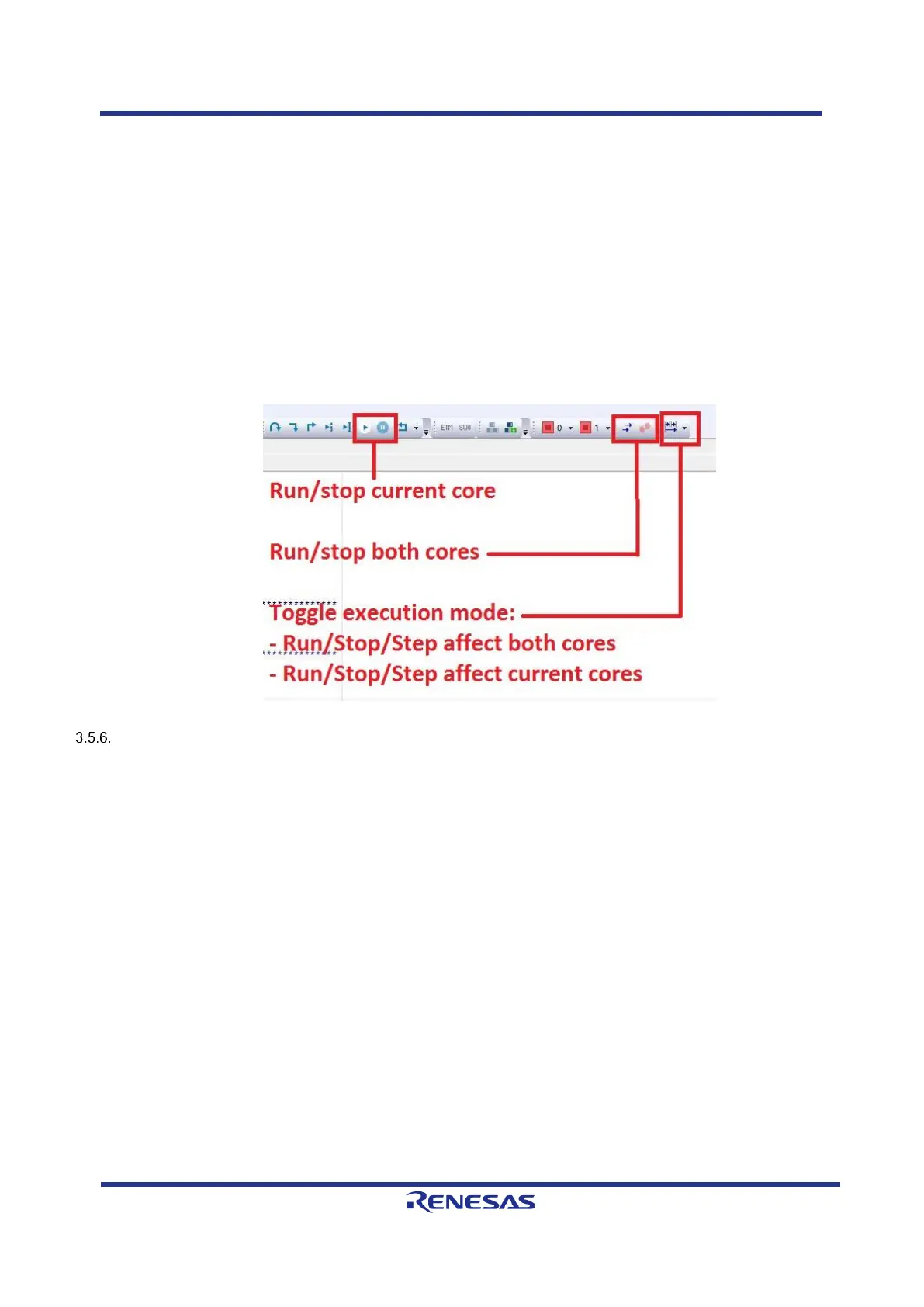

7. When the software from both instances is loaded to the board and the IDE switches in the

debug mode an additional dialog for multicore debugging is available giving the following

options:

- start all cores at once

- stop all cores at once

- toggle execution mode

Figure 3-7: Multicore Debug Interface

Core To Core variant – RZ/N1L (Communication Core)

The binary file for the CM3 core is located in the board type related IAR Embedded Workbench folder

goal\projects\goal_pnio_rpc\00_goal_rpc\ respectively

goal\projects\goal_pnio_rpc\00_goal_rpc_demo\.

Please refer section 3.5.2 for building and downloading the Core to Core variant on RZ/N1L. It is

handled the same as the standalone variant.

For mulit core projects, the RZ/N1L is used as communication core, while the e.g. Synergy S7GS-SK is

used as application core. Data exchanging is done by SPI. The boards are connected as followed.

Loading...

Loading...