Technical data of CPU 31xC

6.2 CPU 312C

CPU 31xC and CPU 31x, Technical Data

Manual, 01/2006 Edition, A5E00105475-06

6-3

6.2 6.2 CPU 312C

Technical data

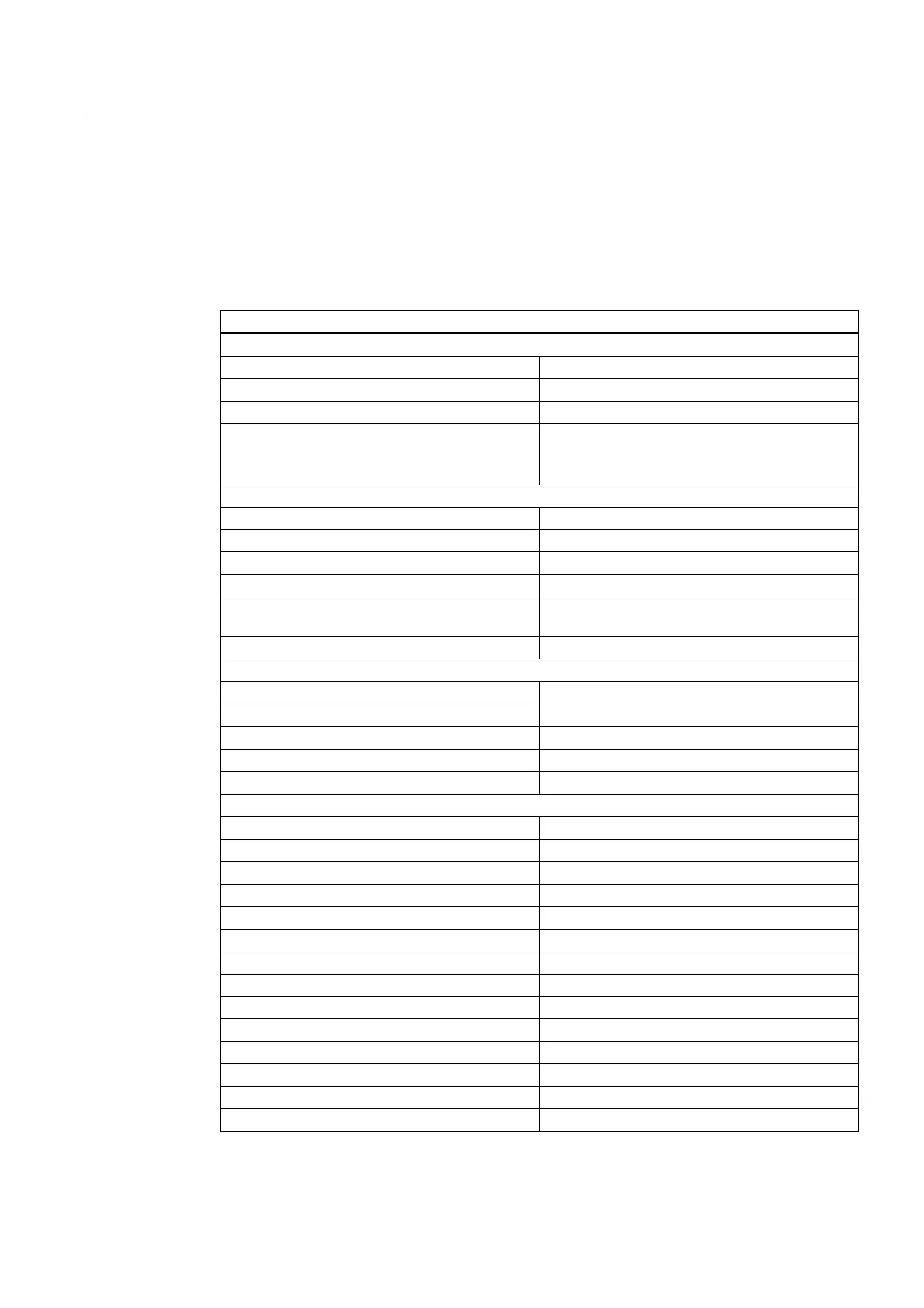

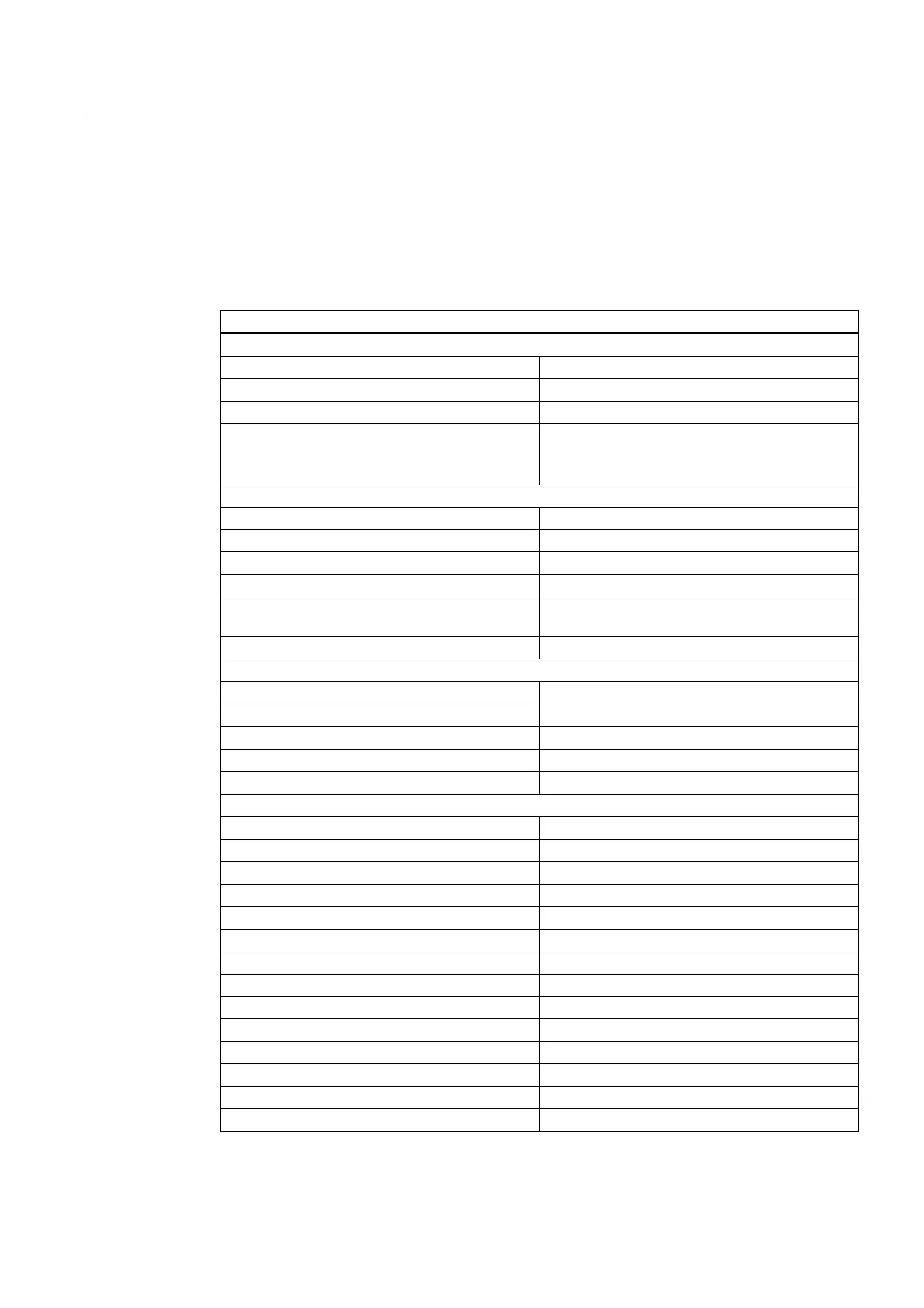

Table 6-3 Technical data of CPU 312C

Technical data

CPU and version

Order number 6ES7 312-5BD01-0AB0

• Hardware version

01

• Firmware version

V2.0

• Associated programming package

STEP 7 as of V 5.2 + SP 1

(please use previous CPU for STEP 7 V 5.1 + SP

3 or later)

Memory

RAM

• Integrated

16 KB

• Expandable

No

Load memory Plugged in with MMC (Max. 4 MB)

Data storage life on the MMC

(following final programming)

At least 10 years

Buffering Guaranteed by MMC (maintenance-free)

Execution times

Processing times of

• Bit operations

Min. 0.2 μs

• Word instructions

Min. 0.4 μs

• Fixed-point arithmetic

Min. 5 μs

• Floating-point arithmetic

Min. 6 μs

Timers/counters and their retentivity

S7 counters 128

• Retentive address areas

Configurable

• Default

from C0 to C7

• Counting range

0 to 999

IEC Counters Yes

• Type

SFB

• Number

unlimited (limited only by RAM size)

S7 timers 128

• Retentive address areas

Configurable

• Default

Not retentive

• Timer range

10 ms to 9990 s

IEC Timers Yes

• Type

SFB

• Number

unlimited (limited only by RAM size)

Loading...

Loading...