61

High-Speed Instructions

As discussed earlier, PLCs have a scan time. The scan time

depends on the size of the program, the number of I/Os, and

the amount of communication required. However, events may

occur in an application that require a response from the PLC

sooner than the scan cycle would normally permit. For these

applications high-speed instructions, such as those associated

with high-speed counters, can be used.

PLC Scan

R

e

a

d

I

n

p

u

t

s

E

x

e

c

u

t

e

P

r

o

g

r

a

m

D

i

a

g

n

o

s

t

i

c

s

&

C

o

m

m

u

n

i

c

a

t

i

o

n

U

p

d

a

t

e

O

u

t

p

u

t

s

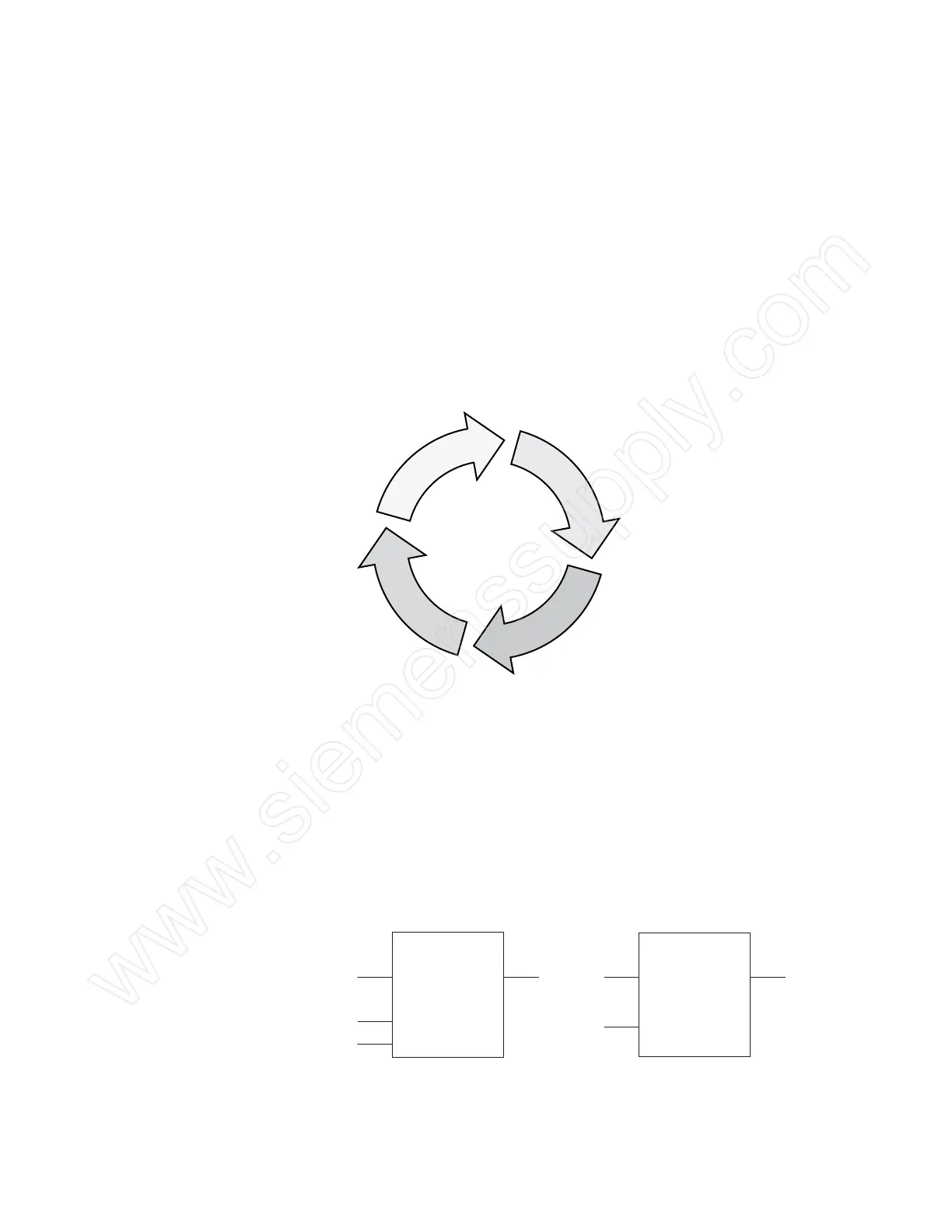

High-Speed Counters A high-speed counter is represented by two boxes in ladder

logic. One box is the High-Speed Counter Definition (HDEF)

instruction and the other box is the

High-Speed Counter

(HSC) instruction.

CPU 221 and CPU 222 support four high-speed counters

(HSC0, HSC3, HSC4, HSC5). CPU 224, CPU 224XP, CPU

224XPsi, and CPU 226 support six high-speed counters (HSC0,

HSC1, HSC2, HSC3, HSC4, HSC5).

High-Speed Counter Definition

HDEF

EN

HSC

MODE

ENO

High-Speed Counter

HSC

EN ENO

N

Loading...

Loading...