- 13 -

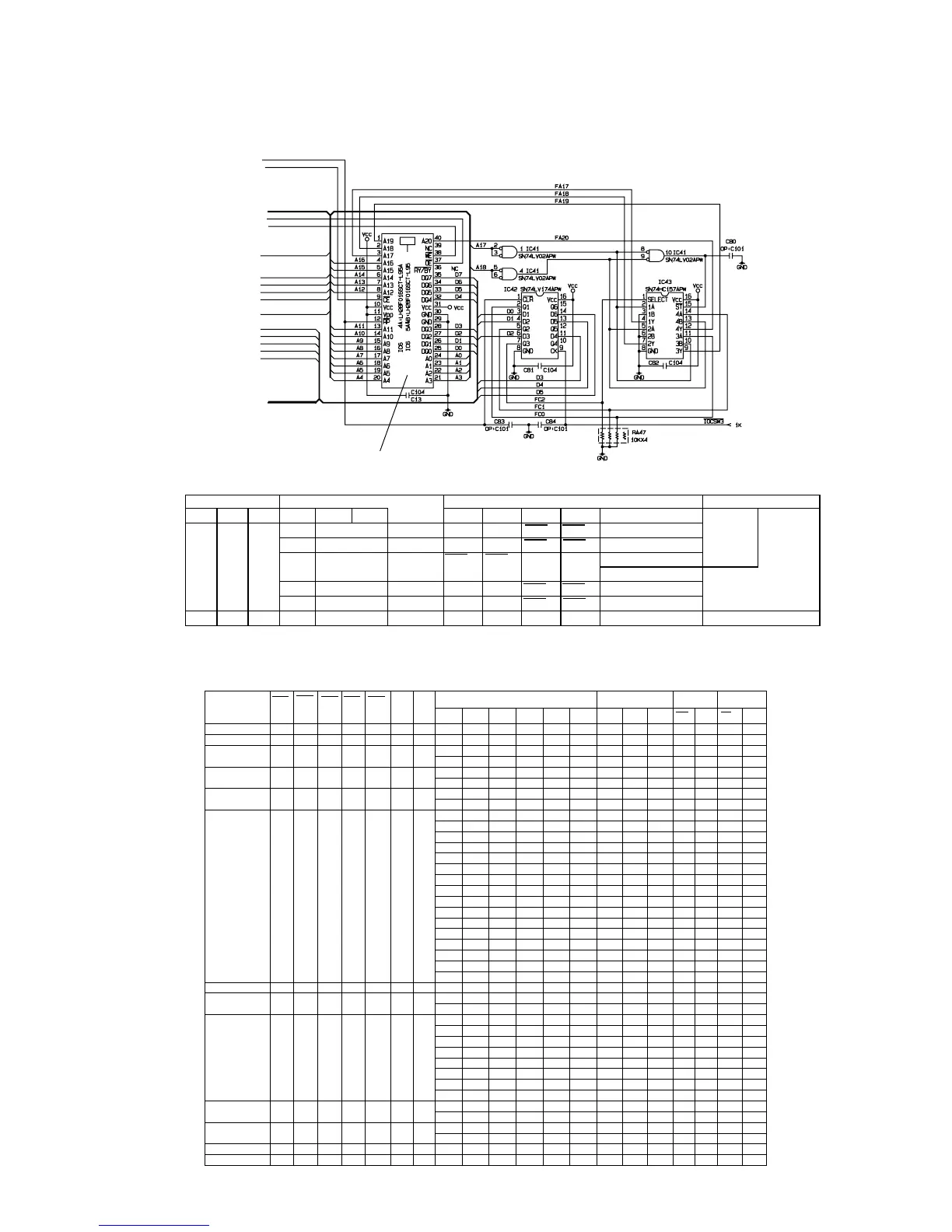

6-5. Flash ROM1 address circuit

The Flash ROM1 address signals FA17 to FA20 are made by the following circuit.

The Flash ROM1 (LH28F016SCT-L95, 16M bits) is used for the application program.

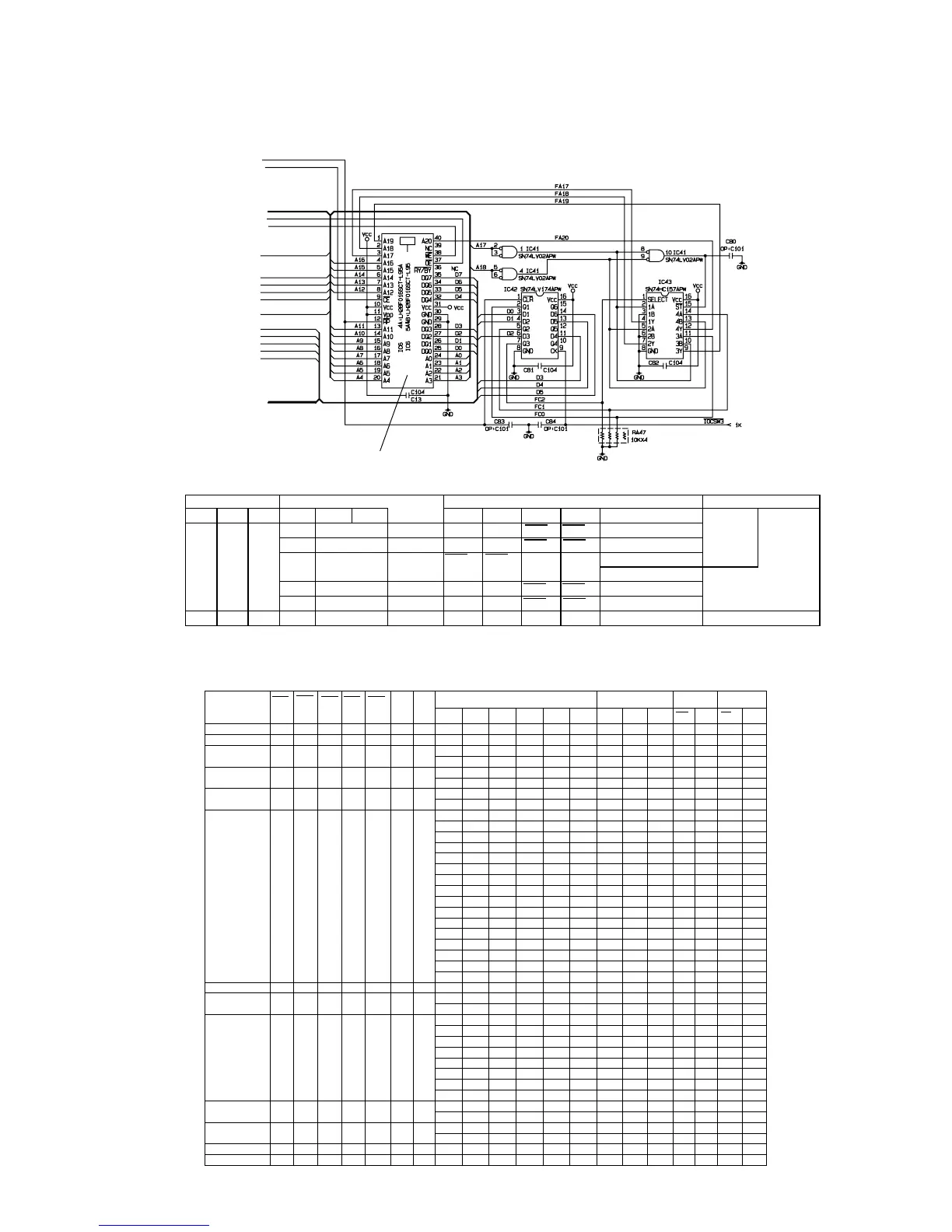

6-6. Memory map

The memory table is as follows:

RAM enable 2CS 3CS 4CS 8CS CCS A18 A19 RAM BANK Flash BANK RAM1 Flash1

No. RB0 RB1 RB2 RB3 RB4 FB0 FB1 FB2 CS A16 CS A18

H L HHHH LLCOMXXXXXXXXLLHX

H HLHHHLLCOMXXXXXXXXLHHX

H HHLHHHL 0L HL L XXXXHXHX

1HHL L XXXXHXHX

H HHLHHHL L L HL XXXXHXHX

HL HL X XXXHXHX

H HHLHHHL L HHL X XXXHXHX

HHHLXXXXHXHX

H HHLHHHL 2LLLHLXXXHXHX

3HL L HL XXXHXHX

4L HL HL XXXHXHX

5HHL HL XXXHXHX

6L L HHL XXXHXHX

7HL HHL XXXHXHX

8LHHHL XXXHXHX

9HHHHLXXXHXHX

10L L L HHXXXHXHX

11HL L HHXXXHXHX

12L HL HHXXXHXHX

13HHL HHXXXHXHX

14L L HHHXXXHXHX

15HL HHHXXXHXHX

16LHHHHXXXHXHX

17HHHHHXXXHXHX

L XXXXXXX XXXXXXXXHXXX

X HHLHHHL HLLLXLHLHXHX

HLLLXHHLHXHX

X HHLHHHL LLLLLLLLHXHX

HLLLLLLLHXHX

LLLLHLLLHXHX

HLLLHLLLHXHX

LLLLLHLLHXHX

HLLLLHLLHXHX

LLLLHHLLHXHX

HLLLHHLLHXHX

X HHLHHHL XLLLXLXHHXHX

XLLLXHXHHXHX

X HHHLH LH XXXXXLXHHXHX

XXXXXHXHHXHX

H HHHL H LH XXXXXXXLHXLA18

H HHHHL HH XXXXXXXXHXLA18

CPU address BANK port Flash memory address NOTE

A19 A18 A17 FC2 FC1 FC0 BANK FA20 FA19 FA18 FA17 Memory block No. 8M bank 16M bank

H L L L L L 0 L L A18 A17 02 to 07

L H L L H 1 L H A18 A17 0A to 0F

H L H X X 2 A18 A17 L L 08,09

10,11,18,19

L H L 3 H L A18 A17 12 to 17

L H H 4 H H A18 A17 1A to 1F

H H H X X X Common LLLL00,01 Common

Flash ROM1 (16M bits)

Loading...

Loading...