Cisco UCS C480 M5 Memory Guide

10

DIMM Memory Mirroring

DIMM Memory Mirroring

Memory mirroring is supported only on the DIMMs; DCPMMs do not support memory mirroring. When memory

mirroring is enabled, the memory subsystem simultaneously writes identical data to two adjacent channels.

If a memory read from one of the channels returns incorrect data due to an uncorrectable memory error,

the system automatically retrieves the data from the other channel. A transient or soft error in one channel

does not affect the mirrored data, and operation continues unless there is a simultaneous error in exactly

the same location on a DIMM and its mirrored DIMM. Memory mirroring reduces the amount of memory

available to the operating system by 50% because only one of the two populated channels provides data.

CPU/Memory Configuration With Memory Mirroring

There are two CPU modules, one in each CPU bay. The lower CPU module occupies Bay 1 and the upper CPU

module occupies Bay 2. CPU 1 and CPU2 are in Bay 1; CPU 3 and 4 are in Bay 2.

Select from 4, 6, 8, or 12 DIMMs per CPU (DIMMs for

all four CPUs must be configured identically). In

addition, the memory mirroring option (N01-MMIRROR) as shown in Table 1 on page 5 must be selected.

The DIMMs will be placed by the factory as shown in the

following tables.

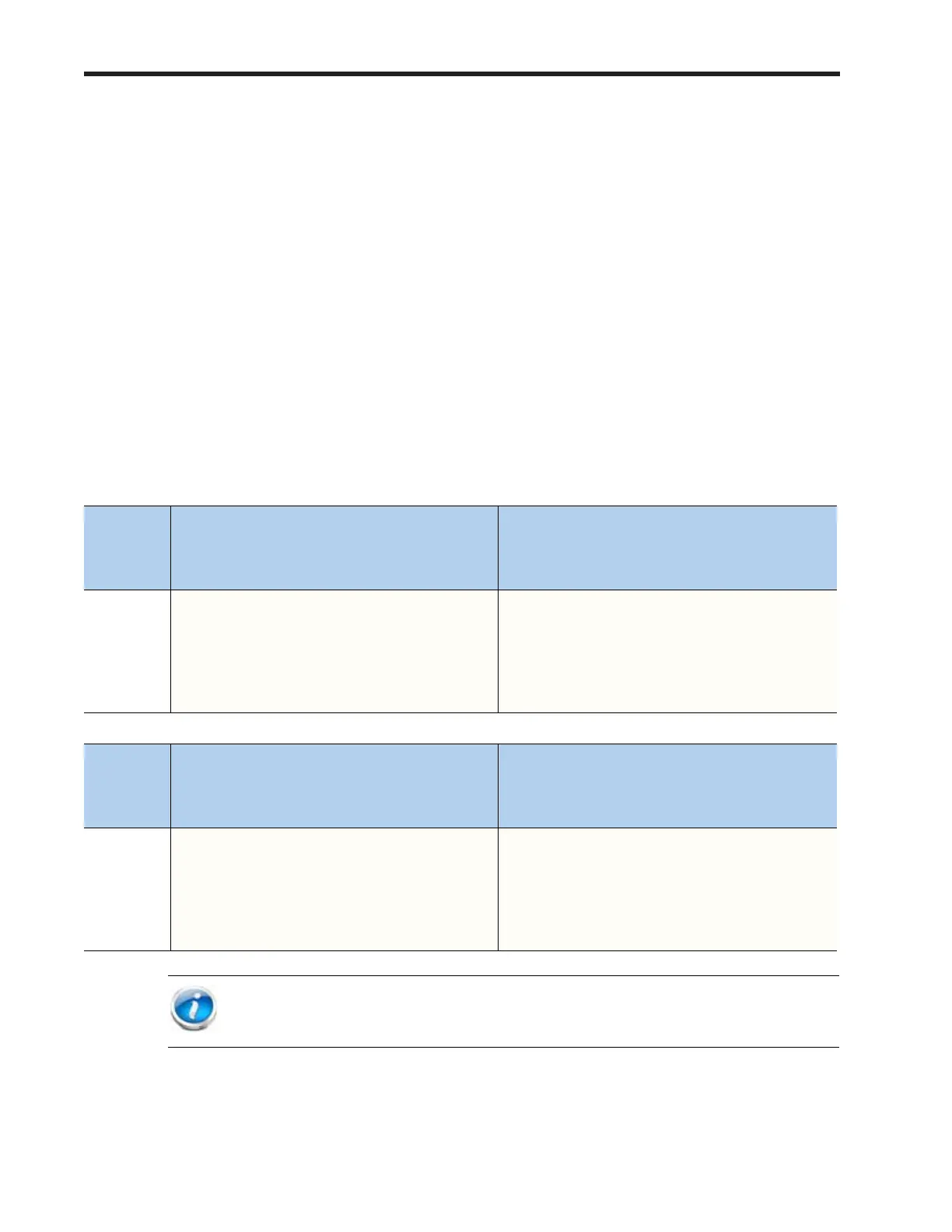

CPU 1 DIMM Placement in Channels

(for identical ranked DIMMs)

CPU 2 DIMM Placement in Channels

(for identical ranked DIMMs)

CPU 1 CPU 2

8 (A1,B1); (D1,E1) (G1, H1); (K1, L1)

12 (A1, B1, C1); (D1, E1, F1) (G1, H1, J1); (K1, L1, M1)

16 (A1, A2, B1, B2); (D1, D2, E1, E2) (G1, G2, H1, H2); (K1, K2, L1, L2)

24 (A1, A2, B1, B2, C1, C2); (D1, D2, E1, E2,

F1, F2)

(G1, G2, H1, H2, J1, J2); (K1, K2, L1, L2, M1,

M2)

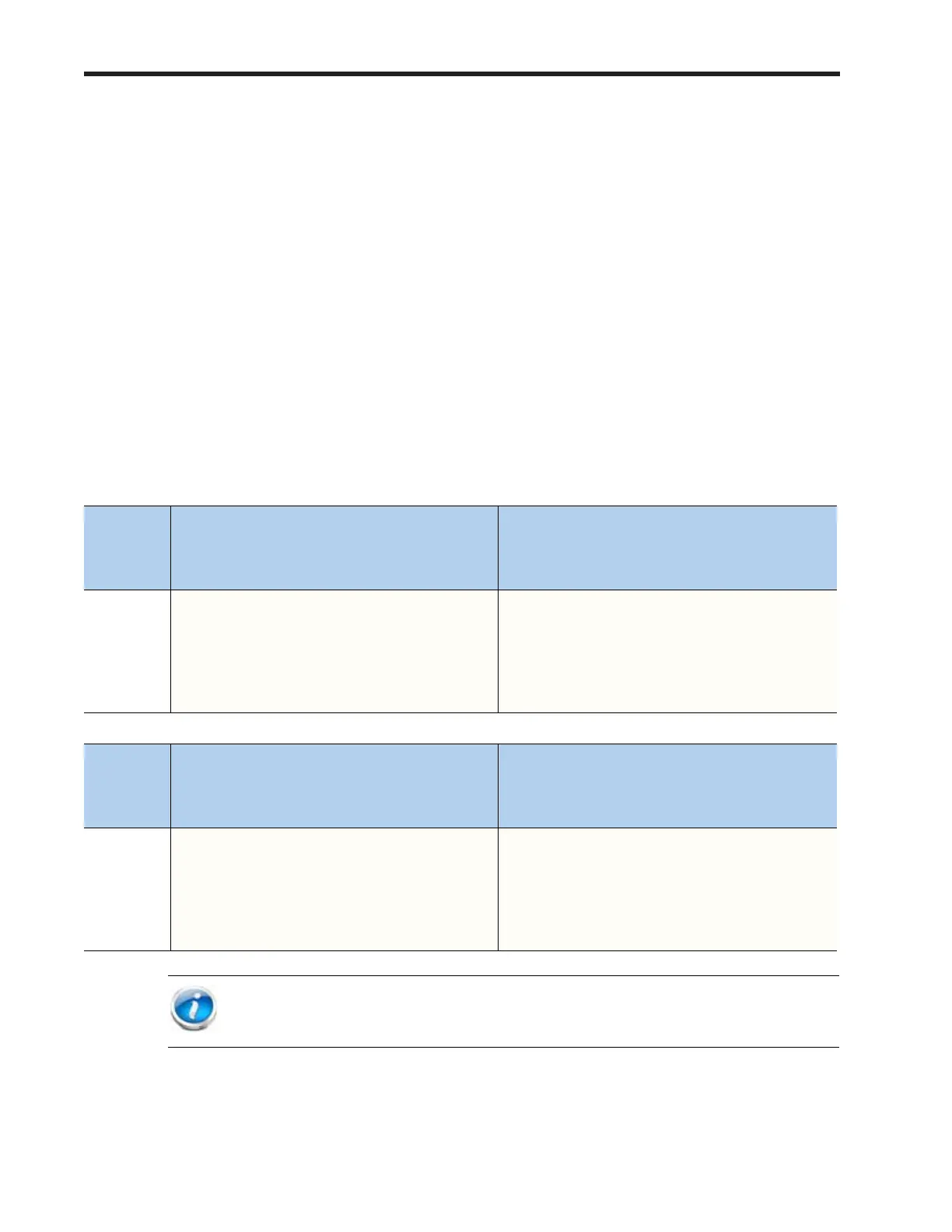

CPU 3 DIMM Placement in Channels

(for identical ranked DIMMs)

CPU 4 DIMM Placement in Channels

(for identical ranked DIMMs)

CPU 3 CPU 4

8 (A1,B1); (D1,E1) (G1, H1); (K1, L1)

12 (A1, B1, C1); (D1, E1, F1) (G1, H1, J1); (K1, L1, M1)

16 (A1, A2, B1, B2); (D1, D2, E1, E2) (G1, G2, H1, H2); (K1, K2, L1, L2)

24 (A1, A2, B1, B2, C1, C2); (D1, D2, E1, E2,

F1, F2)

(G1, G2, H1, H2, J1, J2); (K1, K2, L1, L2, M1,

M2)

NOTE: System performance is optimized when the DIMM type and quantity are equal

for both CPUs, and when all channels are filled equally across the CPUs in the server.

Loading...

Loading...