Cisco UCS C480 M5 Memory Guide

4

Memory Organization

Memory Organization

The standard memory features are:

— Clock speed: 2666 MHz or 2933 MHz depending on CPU type

— Ranks per DIMM: 1, 2, 4, or 8

— DIMM operational voltage: 1.2 V

— Registered ECC DDR4 DIMMS (RDIMMs), L

oad-reduced DIMMs (LRDIMMs),

through-silicon via DIMMs (TSV DIMMs), or Intel

®

Optane

TM

DC Persistent Memory

Modules (DCPMMs).

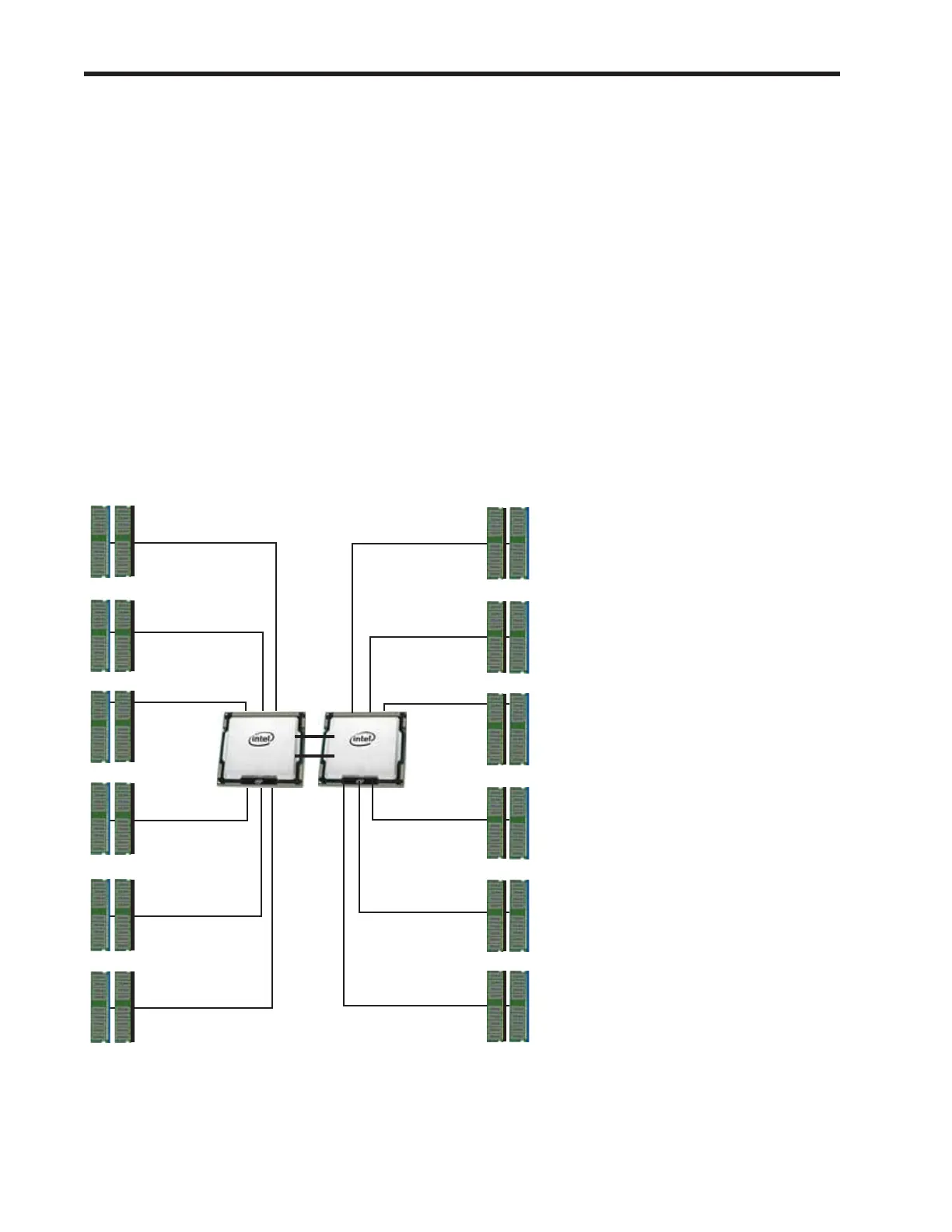

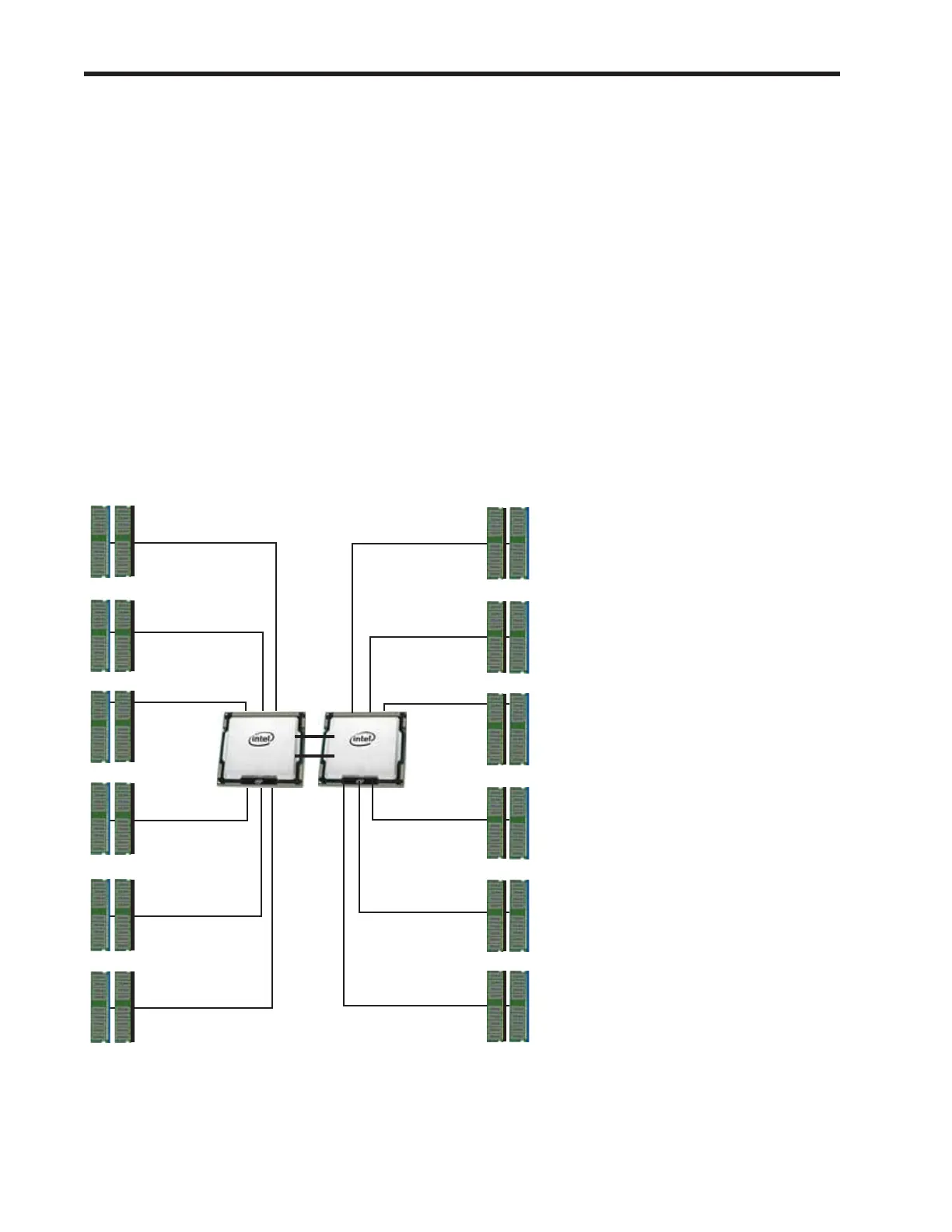

Memory is organized with six memory channels per CPU,

with up to two memory devices per

channel, as shown in Figure 2. CPU1 and CPU2 are in the lower bay; CPU3 and CPU 4 are in the

upper bay. CPU1 and CPU2 control up to 24 DIMMs and CPU3 and CPU4 also control up to 24

DIMMs, for a total of up to 48 DIMMs

total for the server.

Figure 2 C480 Memory Organization

CPU 2/

CPU4

24 DIMMS

6 memory channels per CPU,

up to 2 DIMMs per channel

A1 A2

B1 B2

E1 E2

Chan B

Chan C

Chan D

Chan A

Chan E

Chan F

Chan H

Chan J

Chan L

Chan M

F1 F2

CPU1/

CPU3

Slot 2

Slot 1

Slot 2

Slot 1

H2 H1

J2 J1

L2 L1

M2 M1

Chan G

G2 G1

Chan K

K2 K1

C1 C2

D1 D2

Loading...

Loading...