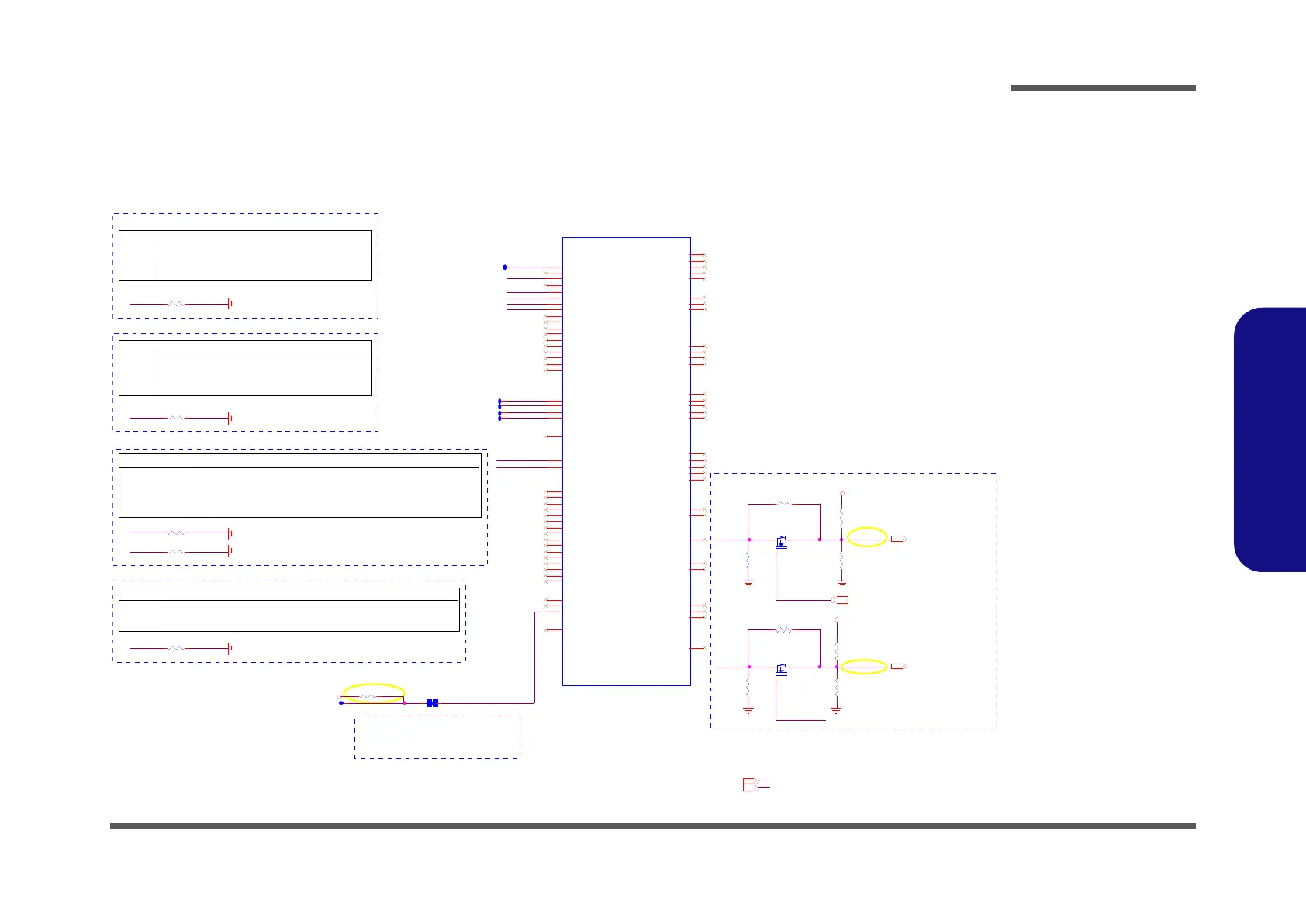

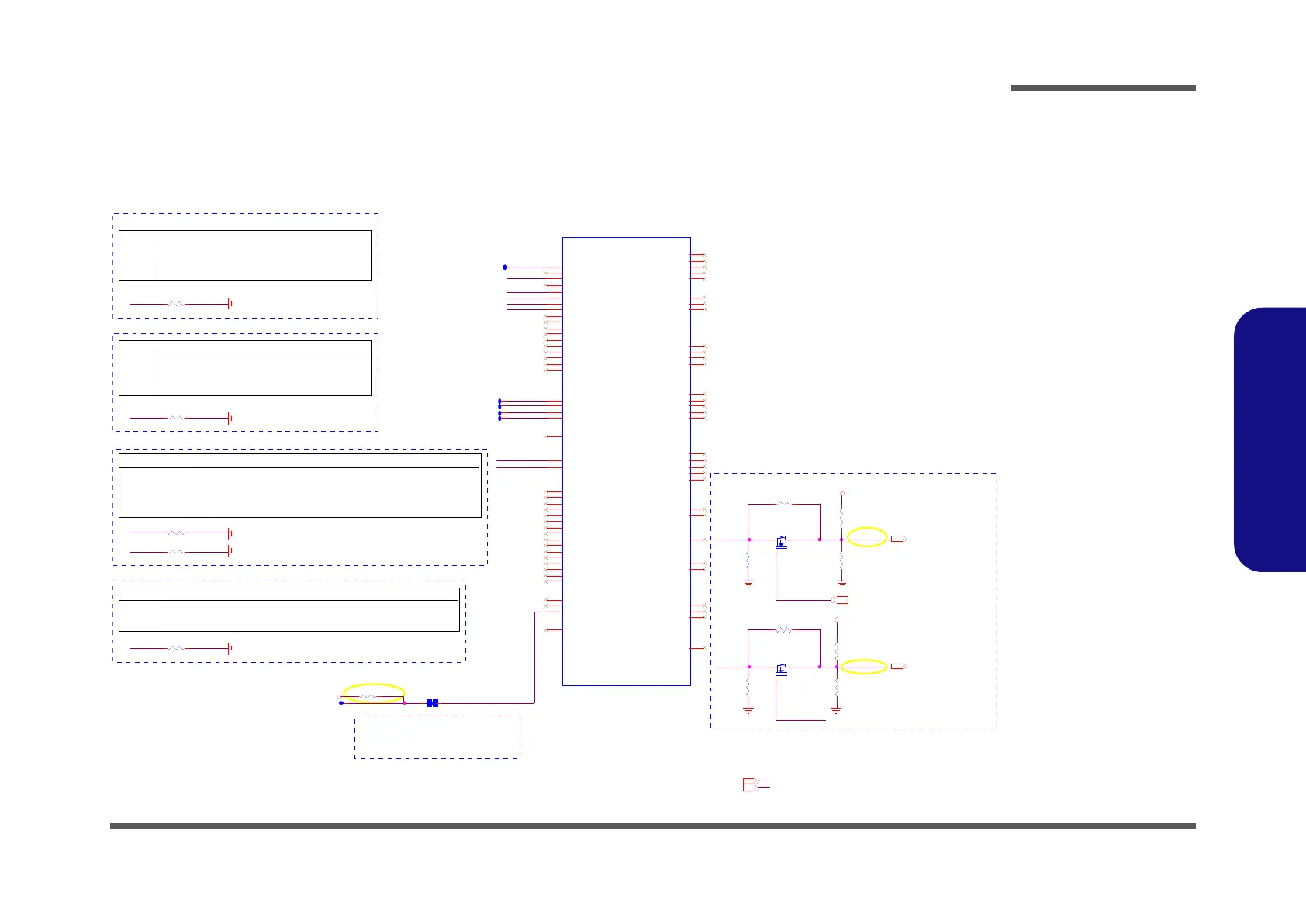

VR EF_CH_A_D IMM

R40 *0_04

MV REF_ DQ _DIM 0

R44 *0_04

MVREF_DQ_DIM1

Q7

*AO3402L

G

DS

R28

1K_1%_04

R4 9

*1 K _ 0 4

R29

1K_1%_04

Q6

*AO3402L

G

DS

R3 9

*1 K _ 0 4

R31

1K _ 1 % _ 04

R38

1K _ 1 % _ 04

D R A M R S T _ C N TR L [ 3, 14 ]

1.5V

1.5V

M VRE F _D Q_ D IMMA [9]

DRAMRST_CNTRL

DRAMRST_CNTRL

M VRE F _D Q_ D IMMB [10 ]

VR EF_CH_B_D IMM

RESERVED

U34E

PZ98827-364B- 01F

CFG [0 ]

AK28

CFG [1 ]

AK29

CFG [2 ]

AL26

CFG [3 ]

AL27

CFG [4 ]

AK26

CFG [5 ]

AL29

CFG [6 ]

AL30

CFG [7 ]

AM31

CFG [8 ]

AM32

CFG [9 ]

AM30

CFG [1 0]

AM28

CFG [1 1]

AM26

CFG [1 2]

AN28

CFG [1 3]

AN31

CFG [1 4]

AN26

CFG [1 5]

AM27

CFG [1 6]

AK31

CFG [1 7]

AN29

RSVD34

AM 33

RSVD35

AJ2 7

RSVD38

J16

RSVD42

AT34

RSVD39

H16

RSVD40

G16

RSVD41

AR 35

RSVD43

AT33

RSVD45

AR 34

RSVD56

AT2

RSVD57

AT1

RSVD58

AR 1

RSVD46

B34

RSVD47

A33

RSVD48

A34

RSVD49

B35

RSVD50

C35

RSVD51

AJ3 2

RSVD52

AK32

RSVD30

AE7

RSVD31

AK2

RSVD28

L7

RSVD29

AG 7

RSVD 27

J15

RSVD 16

C30

RSVD 15

D23

RSVD 17

A31

RSVD 18

B30

RSVD 20

D30

RSVD 19

B29

RSVD 22

A30

RSVD 21

B31

RSVD 23

C29

RSVD 24

J20

RSVD37

T8

RSVD 6

B4

RSVD 7

D1

RSVD 8

F25

RSVD 9

F24

RSVD 11

D24

RSVD 12

G2 5

RSVD 13

G2 4

RSVD 14

E23

RSVD32

W8

RSVD33

AT26

RSVD 25

B18

RSVD44

AP35

RSVD 10

F23

RSVD 5

AJ 26

VAXG_VAL_SENSE

AJ 31

VSSAXG_ VAL_SEN SE

AH31

VCC _ VAL _SE NSE

AJ 33

VSS_VAL_SENSE

AH33

KE Y

B1

VC C_DIE_ SEN SE

AH 27

VCC IO_SEL

A19

RSVD54

AN 35

RSVD55

AM 35

CFG 6

CFG 5

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG[6:5]

R 92 *1K_04

PCIE Port Bifurcation Straps

R 99 *1K_04

On CRB

H_SNB_IVB#_PWRCTRL = low, 1.0V

H_SNB_IVB#_PWRCTRL = high/NC, 1.05V

PEG DEFER TRAINING

1: (Default) PEG Train immediately following xxRESETB de assertion

0: PEG Wait for BIOS for training

CFG7

R 93 *1K_04

CFG 7

3.3V[ 2,3,11,13,14,15,17,18, 19,20,22,23,26,28,30,31,33,34,35]

10/29

CFG 2

CFG2

CFG 4

CFG Straps for Pro cessor

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

Display Port Presence Strap

1:(Default) Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG4

R 110 *1K_04

R 111 *1K_04

H_CPU _RSVD 1

H_CPU _RSVD 4

H_CPU _RSVD 3

H_CPU _RSVD 2

10 /2 9

CFG 7

CFG 4

CFG 2

CFG 6

CFG 0

CFG 5

10 /2 9

1.5V[3,6 ,9,10 ,20,26 ,2 8 ,31 ,33]

Sandy Bridge Processor 7/7

( RESERVED )

VR EF_CH _A_D IMM

VR EF_CH _B_D IMM

R391 * 10m il_04

3.3V

R 392 10K_04

H _SN B_IVB#_P WRC TR L

Loading...

Loading...