DMA

The microprocessor

is

supported by a set of high-function support

devices providing four channels of 20-bit direct-memory access

(DMA), three 16-bit timer/counter channels, and eight

prioritized interrupt levels.

Three of the four

DMA

channels are available on the

I/O

bus and

support high-speed data transfers between

I/O

devices and

memory without microprocessor intervention. The fourth

DMA

channel

is

programmed to refresh the system's dynamic memory.

This

is

done by programming a channel of the timer/counter

device to periodically request a dummy

DMA

transfer. This

action creates a memory-read cycle, which

is

available to refresh

dynamic memory

both

on

the system board and in the system

expansion slots.

DMA

data transfers take five clock cycles of

210ns,

or

1.05j.ts. (See

I/O

CH

RDY on page 1-22.) Refresh

cycles occur once every 72 clocks (approximately

15j.ts)

and

require four clocks or approximately

5.6%

of the bus bandwidth.

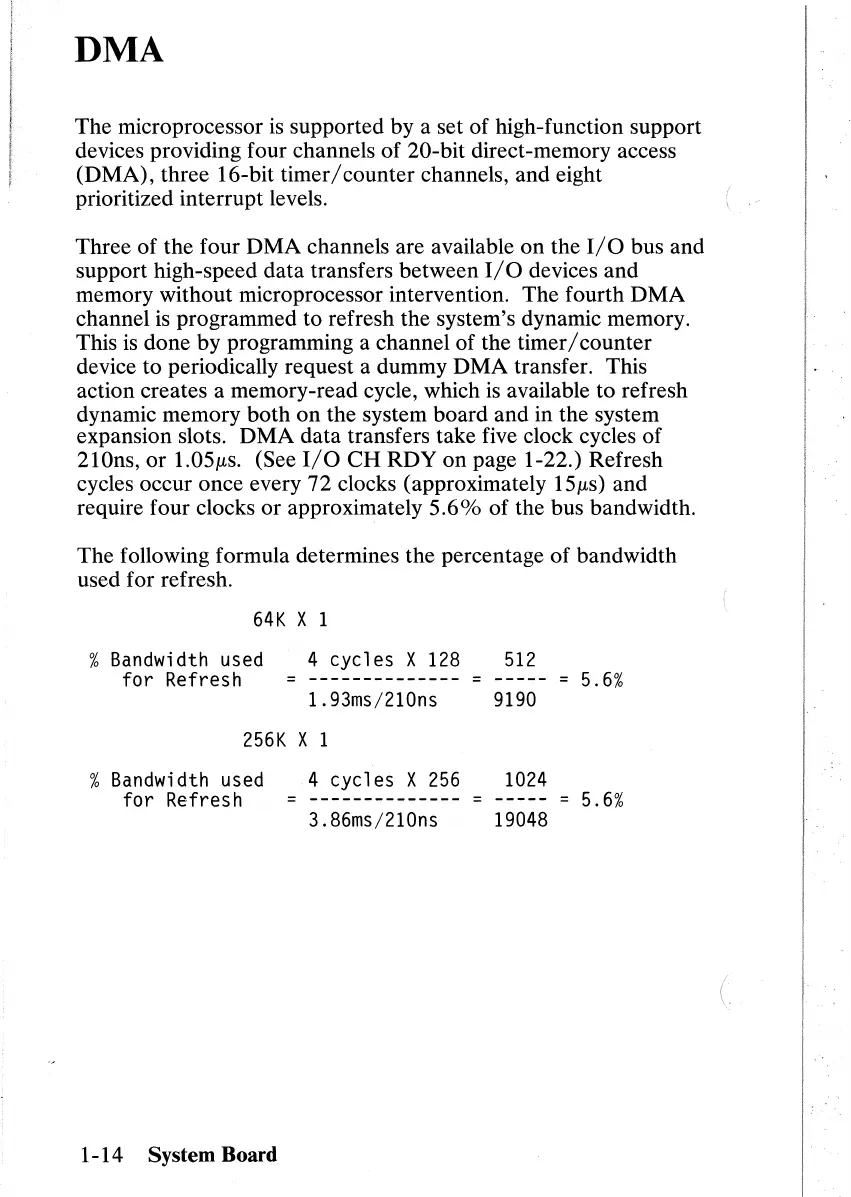

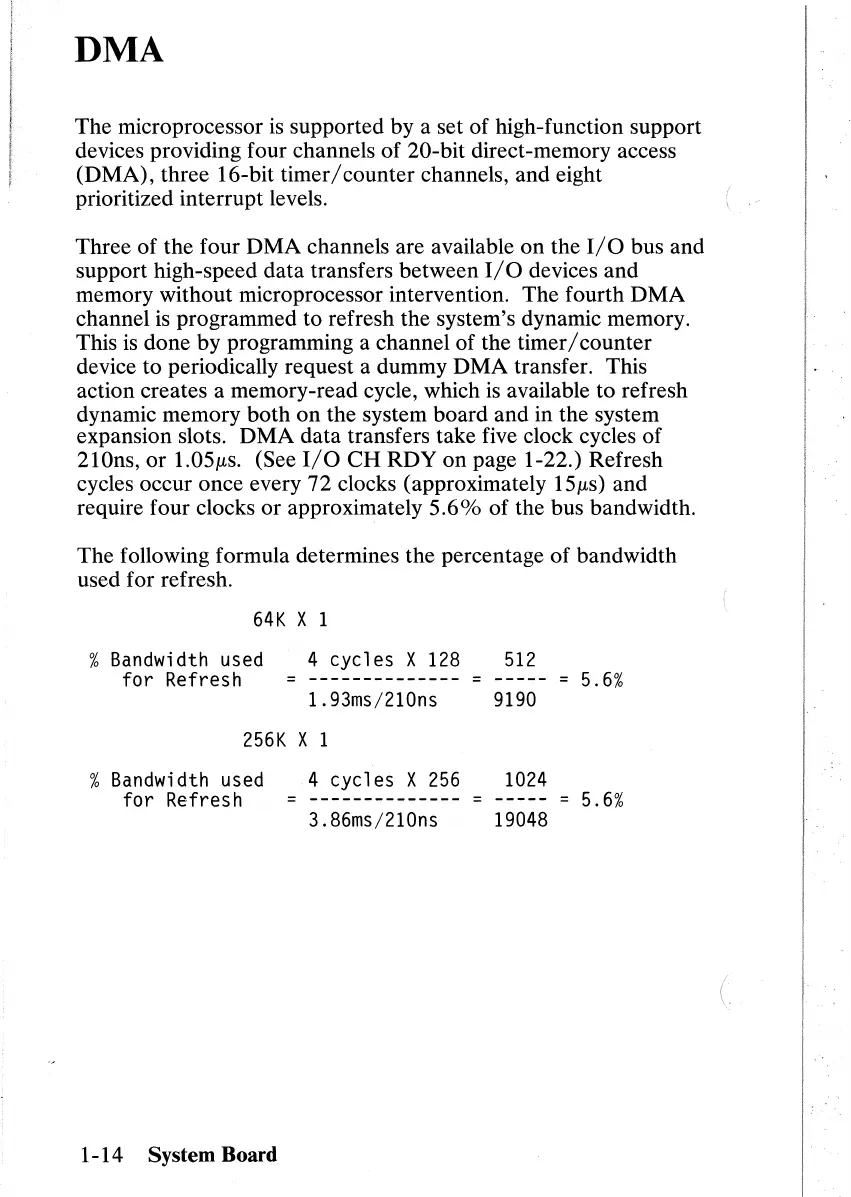

The following formula determines the percentage of bandwidth

used for refresh.

64K

X 1

%

Bandwidth used

4 cycles

X

128

512

for

Refresh

--------------

5.6%

1.93ms/210ns

9190

256K

X 1

%

Bandwidth used

4 cycles

X

256

1024

for Refresh

--------------

5.6%

3.86ms/210ns

19048

1-14 System Board

Loading...

Loading...