Functional Architecture Overview Intel® Server Board S2600CO Family TPS

20 Revision 1.4

Intel order number G42278-004

Processor Core Features:

Up to twelve execution cores

Each core supports two threads (Intel

®

Hyper-Threading Technology), up to 16 threads

per socket

46-bit physical addressing and 48-bit virtual addressing

1 GB large page support for server applications

A 32-KB instruction and 32-KB data first-level cache (L1) for each core

A 256-KB shared instruction/data mid-level (L2) cache for each core

Up to 20 MB last level cache (LLC): up to 2.5 MB per core instruction/data last level

cache (LLC), shared among all cores

Supported Technologies:

Intel

®

Virtualization Technology (Intel

®

VT)

Intel

®

Virtualization Technology for Directed I/O (Intel

®

VT-d)

Intel

®

Virtualization Technology Processor Extensions

Intel

®

Trusted Execution Technology (Intel

®

TXT)

Intel

®

64 Architecture

Intel

®

Streaming SIMD Extensions 4.1 (Intel

®

SSE4.1)

Intel

®

Streaming SIMD Extensions 4.2 (Intel

®

SSE4.2)

Intel

®

Advanced Vector Extensions (Intel

®

AVX)

Intel

®

Hyper-Threading Technology

Execute Disable Bit

Intel

®

Turbo Boost Technology

Intel

®

Intelligent Power Technology

Enhanced Intel

®

SpeedStep Technology

3.2.1 Intel

®

QuickPath Interconnect

The Intel

®

QuickPath Interconnect is a high speed, packetized, point-to-point interconnect used

in the processor. The narrow high-speed links stitch together processors in distributed shared

memory and integrated I/O platform architecture. It offers much higher bandwidth with low

latency. The Intel

®

QuickPath Interconnect has an

efficient

architecture

allowing more

interconnect performance to be achieved in real systems. It has a snoop protocol optimized for

low latency and high scalability, as well as packet and lane structures enabling quick

completions of transactions. Reliability, availability, and serviceability features (RAS) are built into

the architecture.

The physical connectivity of each interconnect link is made up of twenty differential signal pairs

plus a differential forwarded clock. Each port supports a link pair consisting of two uni-directional

links to complete the connection between two components. This supports traffic in both

directions simultaneously. To facilitate flexibility and longevity, the interconnect is defined as

having five layers: Physical, Link, Routing, Transport, and Protocol.

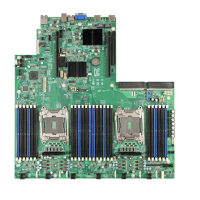

Loading...

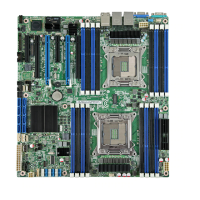

Loading...