34

Feb. 2014 FA-06

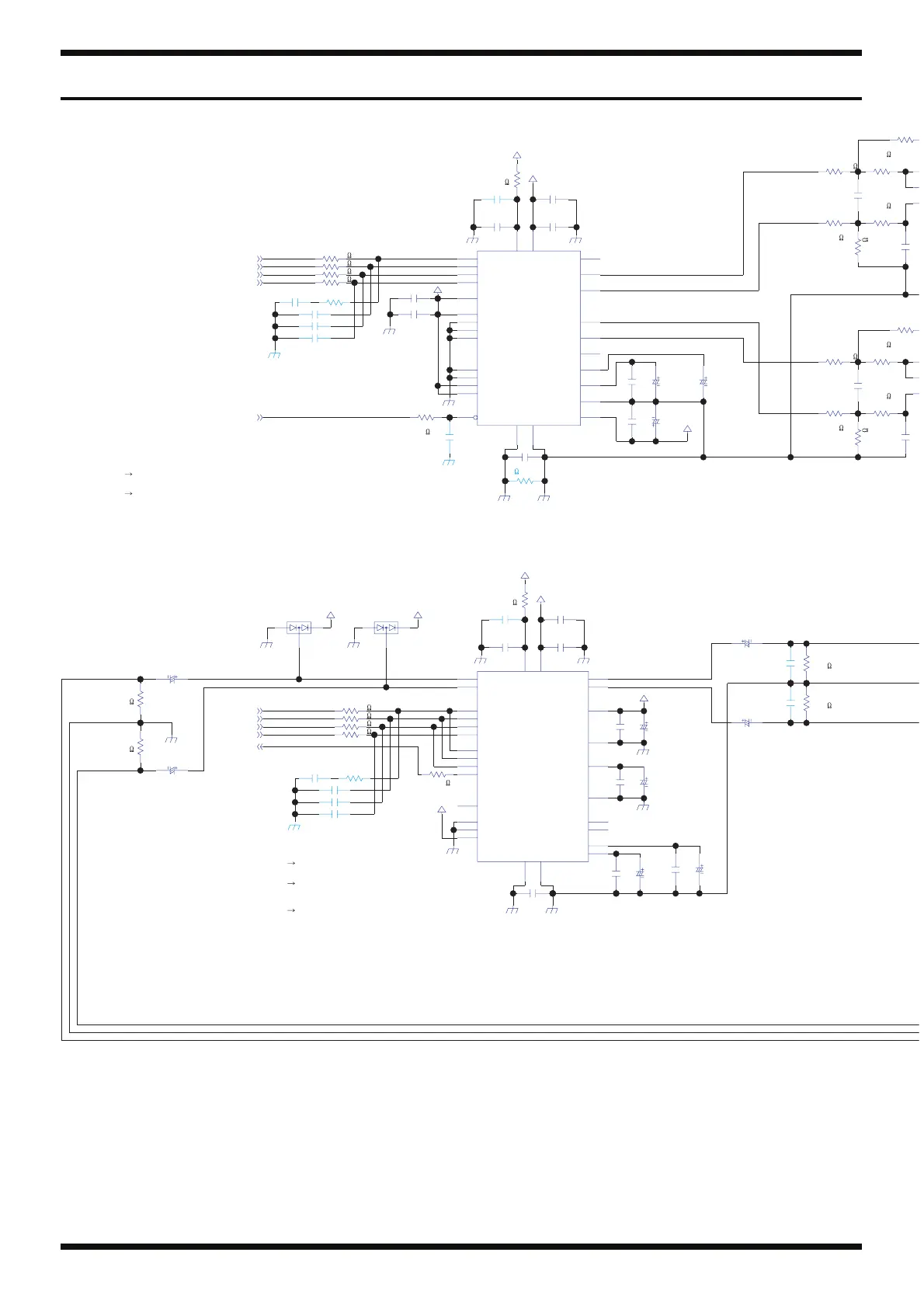

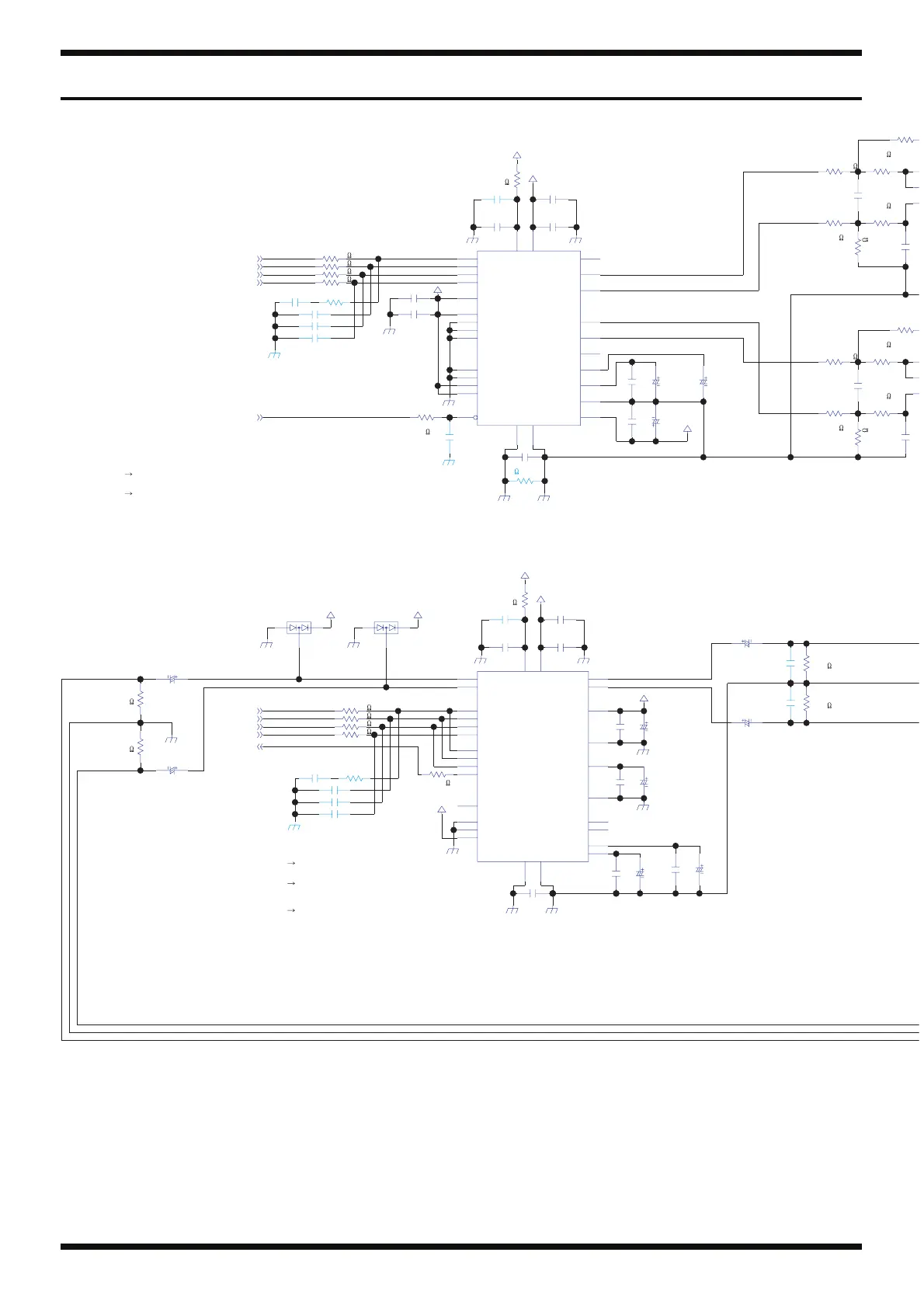

Circuit Diagram (Main Board: 4/7)

fig.d-main4.eps@L

C233

UnPop

C234 UnPop

C235 UnPop

C226

UnPop

R169

UnPop

C238 UnPop

R240

UnPop

C236

UnPop

C237 UnPop

C242 UnPop

C243 UnPop

C256

UnPop

C23

UnPop

10uF

C262

2012

10V

UnPop

10uF

C263

2012

10V

UnPop

10

R384

UnPop3216

1/4W

A+5V

A+5V

DACAGND

I2S-M-CLK

I2S-B-CLK

I2S-LR-CLK

I2S-SD2

DGND

XDAC-PD

I2S-SD0

I2S-M-CLK

I2S-SD1

I2S-B-CLK

I2S-LR-CLK

DGND

DGND

DGND

CODECAGND

A+5V

CODECAGND

D+3.3V

CODECAGND

A+5V

D+3.3V

D+3.3V

CODECAGND

A+5V

CODECAGNDCODECAGND

A+5V

DGND

DGND

DGND

DGND

D+3.3V

DGND

DGND DACAGND

CODECAGND

0.1uF

C217

0.1uF

C218

0.1uF

C222

0.1uF

C223

0.1uF

C224

0

R170

0

R171

0

R175

0

R176

CS4398-CZZR

IC14

7

VD

22

VA

17

VREF

16

REF_GND

15

FILT+

26

VQ

18

BMUTEC

20

AOUTB+

19

AOUTB-

24

AOUTA-

23

AOUTA+

25

AMUTEC

21

AGND

MCLK

6

8

DGND

DSD_SCLK

2

VLC

14

VLS

27

SDIN

3

LRCK

5

4

SCLK

_RST

13

M0(AD0/_CS)

12

M1(SDA/CDOUT)

11

M2(SCL/CCLK)

10

M3(AD1/CDIN)

9

DSD_B

1

DSD_A

28

WM8778SEDS/RV

IC15

19

VOUTR

18

VOUTL

26

AVDD

13

DVDD

23

VMIDADC

20

VMIDDAC

2

ZFLAGR

3

ZFLAGL

24

ADCREFGND

25

ADCREFP

21

DACREFN

22

DACREFP

5

DACMCLK

28

AINR

1

AINL

8

ADCBCLK

11

ADCLRC

9

ADCMCLK

6

DIN

4

DACBCLK

DACLRC

7

27

AGND

12

DGND

17

CL/IWL

16

DI/DEEMPH

15

CE/I2S

14

MODE

10

DOUT

0.0033uF

C227

ECHU1C332JX5

0.0033uF

C230

ECHU1C332JX5

100

R235

0

R239

0

R236

0R238

0

R237

33

R241

0.1uF

C245

0.1uF

C247

C248

10uF 16V

0.1uF

C249

C250

10uF 16V

0.1uF

C251

C252

10uF 16V

0.1uF

C253

C254

10uF 16V

0.1uF

C246

C260

10uF 16V

C261

10uF 16V

C288

10uF 16V

C289

10uF 16V

10uF

C255

2012

10V

10uF

C225

2012

10V

0

R284

1608

0

R285

1608

100k

R85

100k

R87

100k

R88

100k

R246

1SS362FV(TPL3)

D11

2

3

1

1SS362FV(TPL3)

D10

2

3

1

0.1uFC264

0.1uFC265

C220

47uF

16V

C219

22uF

16V

C221

10uF

16V

D (0.5%)

10k

R179

D (0.5%)

1

R197

D (0.5%)

10k

R203

D (0.5%)

1

R202

D (0.5%)

5.6k

R193

D (0.5%)

5.6k

R198

D (0.5%)

5.6k

R226

D (0.5%)

5.6k

R201

D (0.5%)

1.2k

R194

D (0.5%)

1.2k

R195

D (0.5%)

1.2k

R200

D (0.5%)

1.2k

R199

3

2

5

6

39

C

E

39

C

E

1000pF

C244

[M1,M0]

[ 0, 0] : Left-Justified, up to 24-bit data

[ 0, 1] : I2S, up to 24-bit data

[ 1, 0] : Right-Justified, 16-bit Data

[ 1, 1] : Right-Justified, 24-bit Data

[M3,M2]

[ 0, 0] : Single-Speed without De-Emphasis (32 to 50 kHz sample rates)

[ 0, 1] : Single-Speed with 44.1 kHz De-Emphasis

[ 1, 0] : Double-Speed (50 to 100 kHz sample rates)

[ 1, 1] : Quad-Speed (100 to 200 kHz sample rates)

CE/I2S

0:Right Justified

1:I2S

DI/DEEMPH

0:De-emphasis disabled

1:De-emphasis enable

CL/WL

0:20bit(RJ),16bit(I2S)

1:24bit

Loading...

Loading...