5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

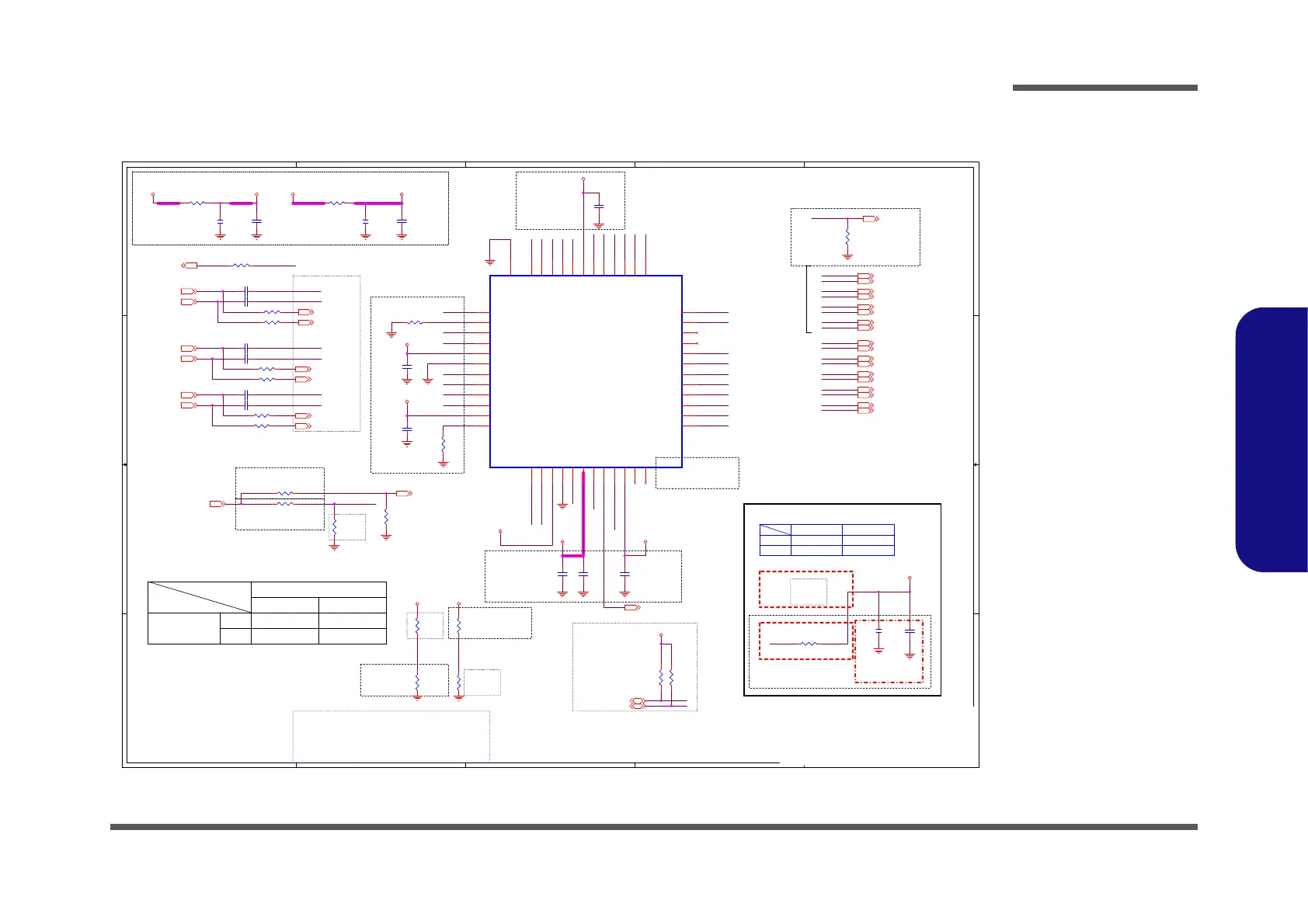

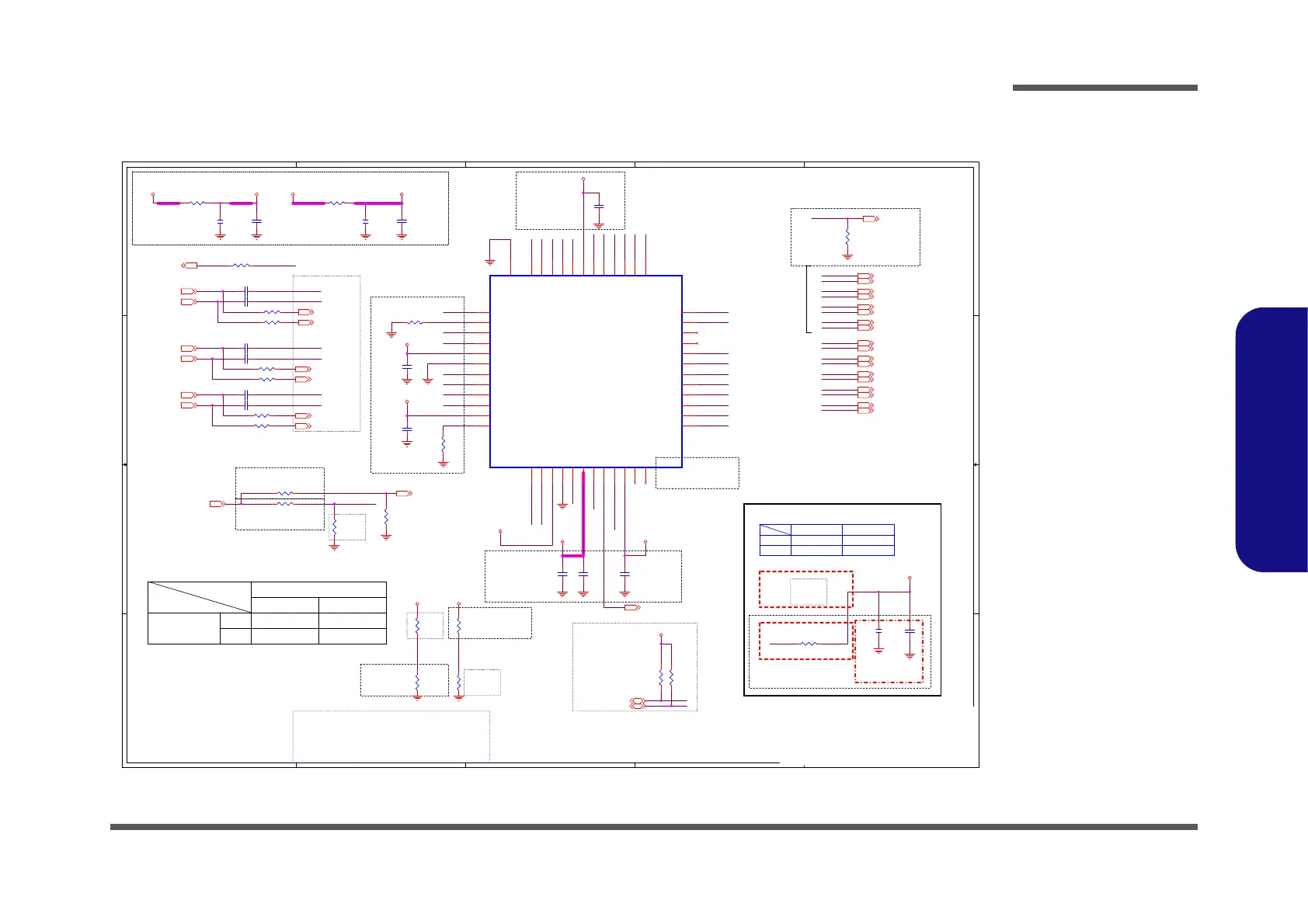

LVDS

ᶲ

ẞ

LVDS

ᶲ

ẞ

LVDS

ᶲ

ẞ

follow common design,Ivy0420

follow common design,Ivy0420

follow common design,Ivy0420

follow common design,Ivy0420

LVDS

ᶲ

ẞ

EDP

ᶲ

ẞ

6-03-02136-031

40mils 40mils

Single link

LVDS

1

Power

MODE_CFG1(PIN48)

SWR MODE

Dual Mode Regulator Configuration

MODE_CFG0(PIN47)

10

Note:

0

3- Slave address should configure as 0xA8

2- EEPROM device should be 2-byte addressing device

1- EEPROM with a size 8K-Byte

: PIN47 4.7K pull high, PIN48 4.7K pull high

: PIN47 4.7K pull high, PIN48 4.7K pull low

: PIN47 4.7K pull low, PIN48 4.7K pull high

EEPROM MODE

Mode Configure Table(Power On Latch)

LDO MODE

EP Mode

ROM ONLY Mode

RTD2136 Supports three operation mode for system design.

ConnectNC

NCConnect

ROM ONLY MODE

Reserved 4.7K resistor pull up/low for mode selection

EEPROM Mode

EP MODE

0 Olm(R)2.2-uH(L)

LDO

SWR

Cap closed to PIN17

X

1. Cap should be closed to chip

6-19-41001-019

暞

ẞ

㔠

:33pcs

80mils 80mils

LVDS

ᶲ

ẞ

PIN48PIN47

LVDS

ᶲ

ẞ

LVDS

ᶲ

ẞ

80mils

LVDS

ᶲ

ẞ

LVDS

ᶲ

ẞ

LVDS

ᶲ

ẞ

冯

LVDS CONNECTOR 2

㑯

1

Modify,7/10 Max

Add follow

ℙ䓐

,7/10 Max

Del L1,7/26 Tim

BRIGHTNESS_EC_PS

LVDS-L0N

LVDS-LCLKP

LVDS-LCLKN

LVDS-L2P

LVDS-L2N

LVDS-L1P

LVDS-L1N

P_DDC_DATA

P_DDC_CLK

PANEL_PWM

LVDS-U0P

LVDS-U0N

LVDS-UCLKP

LVDS-UCLKN

LVDS-U2P

LVDS-U2N

LVDS-U1P

LVDS-U1N

LVDS-L0P

DRX0p

DRX1n

DRX1p

DAUXp

DAUXn

TEST_MODE

HPD

MODE_CFG0

MODE_CFG1

DRX0n

PIN17 ENBLT

P_DDC_DATA

P_DDC_CLK

LVDS-LCLKN

LVDS-LCLKP

LVDS-L0N

LVDS-UCLKN

LVDS-UCLKP

LVDS-U2P

LVDS-U2N

LVDS-U1P

LVDS-U1N

LVDS-U0P

LVDS-U0N

PIN17

PANEL_PWM

LVDS-L2N

LVDS-L2P

LVDS-L1P

LVDS-L1N

LVDS-L0PLVDS-L0P

ENBLT

BRIGHTNESS_EC_PS

SMD_EDP_DAT

SMC_EDP_CLK

DP_REXT

DAUXn

DAUXp

DRX0p

DRX0n

DRX1p

DRX1n

HPD

MODE_CFG0

MODE_CFG1

3.3VS3.3VS DVCC33AVCC33

AVCC33

DVCC33 DVCC33

VCCK_V12

VCCK_V12

VCCK_V12

VCCK_V12

3.3VS 3.3VS

3.3VS

LVDS-LCLKP 15

LVDS-U2N 15

LVDS-LCLKN 15

LVDS-U2P 15

LVDS-U1N 15

LVDS-L2N 15

LVDS-U1P 15

LVDS-L2P 15

LVDS-L0N 15

LVDS-L1P 15

LVDS-L0P 15

LVDS-U0P 15

LVDS-UCLKP 15

LVDS-L1N 15

ENBLT 15

LVDS-U0N 15

LVDS-UCLKN 15

P_DDC_CLK 15

P_DDC_DATA 15

PANEL_PWM 15

EDP_BRIGHTNESS25

LVDS_PLVDD_EN 15

EDP_AUXP3

EDP_TXN_03

EDP_TXN_13

EDP_TXP_13

EDP_TXP_03

EDP_AUXN3

EDP_HPD3,15

DP_AUX# 15

DP_AUX 15

DP_TXP0 15

DP_TXN0 15

DP_TXP1 15

DP_TXN1 15

SMC_EDP_CLK22

SMD_EDP_DAT22

Title

Size Document Number Rev

Date: Sheet

of

6-71-N24G0-D02

1.0

[14] RTD2136N (EDP to LVDS)

A3

14

41Monday, January 22, 2018

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number Rev

Date: Sheet

of

6-71-N24G0-D02

1.0

[14] RTD2136N (EDP to LVDS)

A3

14

41Monday, January 22, 2018

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Size Document Number Rev

Date: Sheet

of

6-71-N24G0-D02

1.0

[14] RTD2136N (EDP to LVDS)

A3

14

41Monday, January 22, 2018

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

R39 0_04LVDS

R38

*4.7K_04

R46 0_06LVDS

C3

4.7u_6.3V_X5R_06

LVDS

RTD2136N

U4

RTD2136N-CG

LVDS

DP_HPD

1

TEST_MODE

2

AUX_CH_N

3

AUX_CH_P

4

DP_V33

5

DP_GND

6

LANE0_P

7

LANE0_N

8

LANE1_P

9

LANE1_N

10

DP_V12

11

DP_REXT

12

CIICSCL

13

CIICSDA

14

SWR_VCCK/LDO_VCCK

15

GND

16

SWR_LX/LDO_FB

17

SWR_VDD/LDO_VDD

18

PWMOUT

19

PANEL_VCC

20

PWMIN

21

PVCC

22

TXE3+

23

TXE3-

24

TXOC-

36

TXOC+

35

TXO3-

34

TXO3+

33

TXE0-

32

TXE0+

31

TXE1-

30

TXE1+

29

TXE2-

28

TXE2+

27

TXEC-

26

TXEC+

25

MODE_CFG1

48

MODE_CFG0

47

MIICSCL

46

MIICSDA

45

BL_EN

44

VCCK

43

TXO0-

42

TXO0+

41

TXO1-

40

TXO1+

39

TXO2-

38

TXO2+

37

EPAD_GND

49

C19

0.1u_10V_X7R_04

LVDS

R21

10K_04

LVDS

R48

4.7K_04

LVDS

C15

0.1u_10V_X7R_04

LVDS

R326 0_04EDP

R16 0_04LVDS

C2

0.1u_10V_X7R_04

LVDS

R17 0_04EDP

C23 0.1u_10V_X7R_04LVDS

C14

2.2u_6.3V_X5R_04

LVDS

C22 0.1u_10V_X7R_04LVDS

C24 0.1u_10V_X7R_04LVDS

R325 0_04EDP

C11

0.1u_10V_X7R_04

LVDS

R30 100K_04LVDS

C13

0.1u_10V_X7R_04

LVDS

C12

0.1u_10V_X7R_04

LVDS

R47

12K_1%_04

LVDS

R37

4.7K_04

LVDS

C27 0.1u_10V_X7R_04LVDS

C18

2.2u_6.3V_X5R_04

LVDS

R29

*4.7K_04

R24 0_06

LVDS

R328 0_04EDP

C10

2.2u_6.3V_X5R_04

LVDS

R323 0_04EDP

R324 0_04EDP

C26 0.1u_10V_X7R_04LVDS

C9

0.1u_10V_X7R_04

LVDS

R28

4.7K_04

LVDS

R42 0_06LVDS

R49

4.7K_04

LVDS

C8

0.1u_10V_X7R_04

LVDS

C25 0.1u_10V_X7R_04LVDS

R327 0_04EDP

R18

10K_04

LVDS

R15

*100K_04

LVDS

Loading...

Loading...