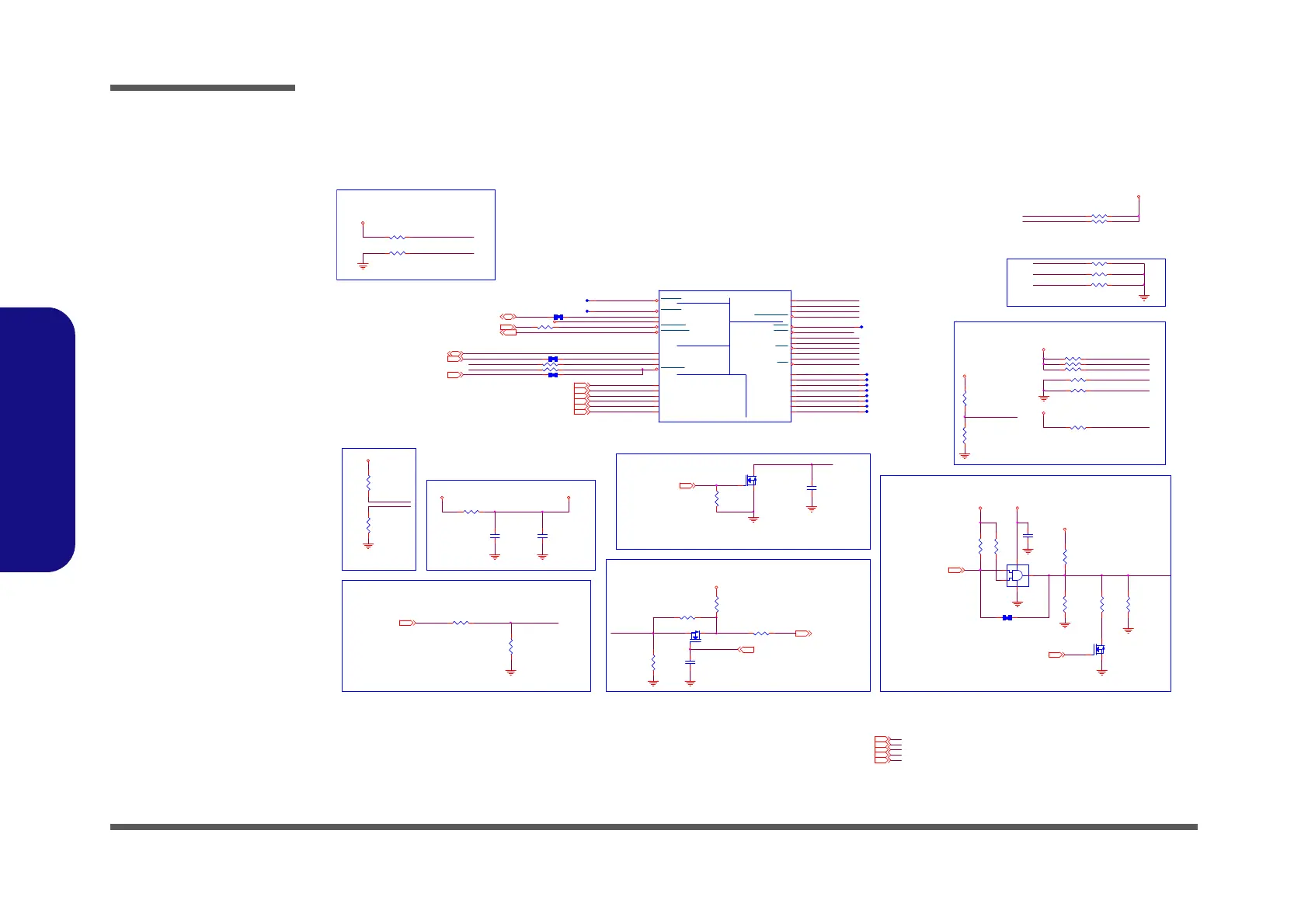

SM_RCOMP_1

SM_RCOMP_0

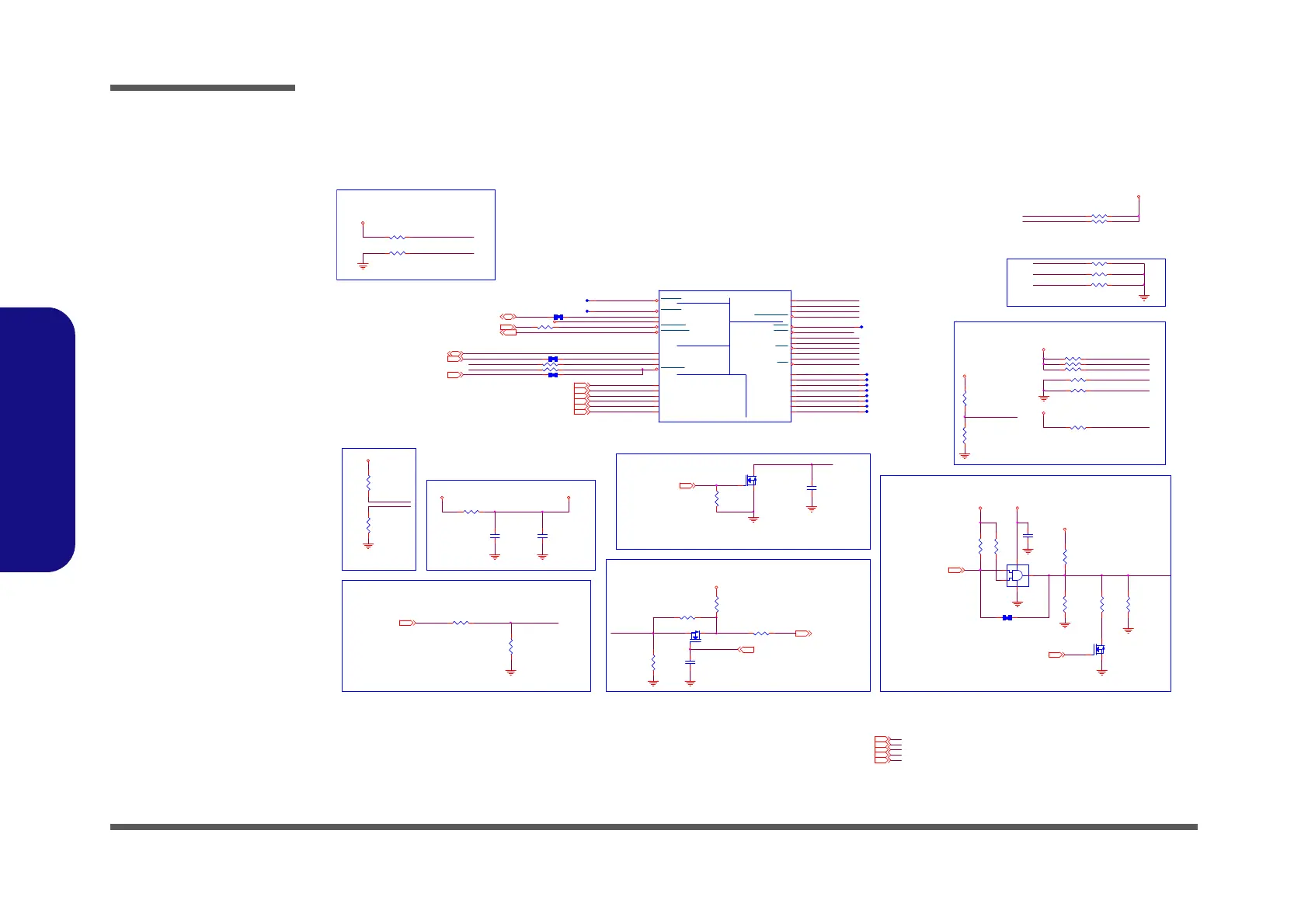

Q18

MTN7002ZHS3

G

DS

SM_RCOMP_2

3.3V3.3V

1.05V_LAN_M

3.3VS

VCCST1.05V_LAN_M

VCCIO_OUT

1.05V_LAN_M

1.05V_LAN_M5,26,27,38,41,42

VCCIO_OUT

VCCST

PLT_RST#23,30

3.3V2,12,17,20,24,25,27,28,29,31,33,35,37,38,40,42

H_PROCHOT_EC36

DDR3_DRAMRST# 9,10

DRAMRST_CNTRL 4,21

3.3VS6,9,10,11,12,19,20,21,22, 23,24,26,27,28,29,30,31, 32,33,34,35,36,37,41

H_PECI24,36

VCCIO_OUT5,6

H_CPUPWRGD24

H_PM_SYNC22

H _TH R MTRI P_ R_ N24

CLK_EXP_N28

CLK_EXP_P28

PCH_CK_DP_P28

PCH_CK_DP_N28

H_THRMTRIP_R_N

SUSB34,37,40

PM_DRAM_PWRGD22

PCH_SSC_N28

CPU_RST_N24

PCH_SSC_P28

H_PROCHOT#41

R374*75_04

CPU_RST_N

V_VDDQ_DIMM

H_CPUPWRGD_RH_CPUPWRGD

CAD Note: Capacitor need to be placed

close to buffer output pin

H_PROCHOT#_D

R50

1.82K_1%_04

Delete, ¥u¯d¤ÀÀ£¡I

PMSY S_PW RGD _BUF

XDP_BPM3

XDP_BPM5

XDP_BPM6

XDP_BPM7

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM4

BUF_CPU_RST#

R391

*1K_1%_04

V_VDDQ_DIMM

XDP_T MS

XDP_TRST#

XDP_T CL K

R377

100K_04

R380 *0_04

BUF_CPU_RST#

R381 *10mil_short

Haswell rPGA EDS

JTAG

CLOCKTHERMA L

MIS C

DDR3

PWR

2 OF 9

U26B

THERMTRIP

AM35

SM_DRAMPWROK

AC10

PLTRSTIN

AT26

SKTOCC

AP32

CATERR

AN32

PECI

AR27

PROCHOT

AM30

DPLL_REF_CLKN

G28

DPLL_REF_CLKP

H28

SSC_DPLL_REF_CLKN

F27

SSC_DPLL_REF_CLKP

E27

BCLKN

D26

BCLKP

E26

SM_RCOMP_0

AP3

SM_RCOMP_1

AR3

SM_RCOMP_2

AP2

SM_DRAMRST

AN3

PRDY

AR29

PREQ

AT29

TCK

AM34

TMS

AN33

TRST

AM33

TDI

AM31

TDO

AL33

DBR

AP33

BPM_N_0

AR30

BPM_N_1

AN31

BPM_N_2

AN29

BPM_N_3

AP31

BPM_N_4

AP30

BPM_N_5

AN28

BPM_N_6

AP29

BPM_N_7

AP28

PWRGOOD

AL34

PM_SYNC

AT28

FC

AK31

R52

3.32K_1%_04

R386 100_1%_04

R376 *2K_1%_04

R387 100_1%_04

PCH_SSC_N

PCH_SSC_P

H_THRMTRIP_R_N

R58

*200_04

SSC CLOCK TERMINATION

STUFF R4R15 & R4R12

ONLY WHEN SSC CLOCK

NOT USED

C104

*22u_6.3V_X5R_08

R36951_04

R37051_04

C103

*22u_6.3V_X5R_08

PCH_SSC_N

If PROCHOT# is not used,

then it must be terminated

with a 56-£[ +-5% pull-up

resistor to 1.05VS_VTT .

R365

51_04

S3 circuit:- DRAM PWR GOOD lCIRCUIT

R38362_04

CPUDRAMRST#

R388 75_1%_04

XD P _ TD O _R

R36310K_04

1.05V_LAN_M

XD P_TMS

H_CATERR#

XD P_TD I_ R

XD P_PR EQ#

R442 *51_04

R448 *51_04

R454 *51_04

R366

*100_04

PMSY S_PW RGD _BUF VDDPWRGOOD_R

H_CPUPWRGD_R

Processor Pullups/Pull downs

TRACE WIDTH 10MIL, LENGTH <500MILS

H_PROCHOT#

R54

*100K_04

XDP_T DO _R

XDP_T DI _R

R24

*10K_04

R25

*10K_04

V_VDDQ_DIMM4,5,9,10,40

PCH_SSC_P

XDP_TRST#

XDP_DBR_R

PU/PD for JTAG signals

XD P_TC LK

R368*100_04

R53 *10mil_short

R49 130_1%_04

CPU_RST_N_R

H_PECI_ISO

R65 *0_04

R399

1K_04

R385 1K_04

R373

4.99K_1%_04

H_PROCHOT#

R51

*39_04

Haswell Processor 2/7 ( CLK,MISC,JTAG )

XDP_PRDY#

XDP_PREQ#

Buffered reset to CPU

SKTOCC#

CPUDRAMRST#

S3 circuit:- DRAM_RST# to memory

should be high during S3

R55

*100K_04

Q2

*MTN7002ZHS3

G

DS

Q15

MTN700 2ZHS3

G

DS

U3

*MC74VHC1G08DFT1G

1

2

5

4

3

C565

0.047u_10V_X7R_04

R379 *10mil_short

C102

*0.1u_16V_Y5V_04

C107

47p_50V_NPO_04

XDP_DBR_R

R392 *0_04

DDR3 Compensation Signals

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

R364 *10mil_short

R397 1K_04

R382 56_1%_04

Loading...

Loading...