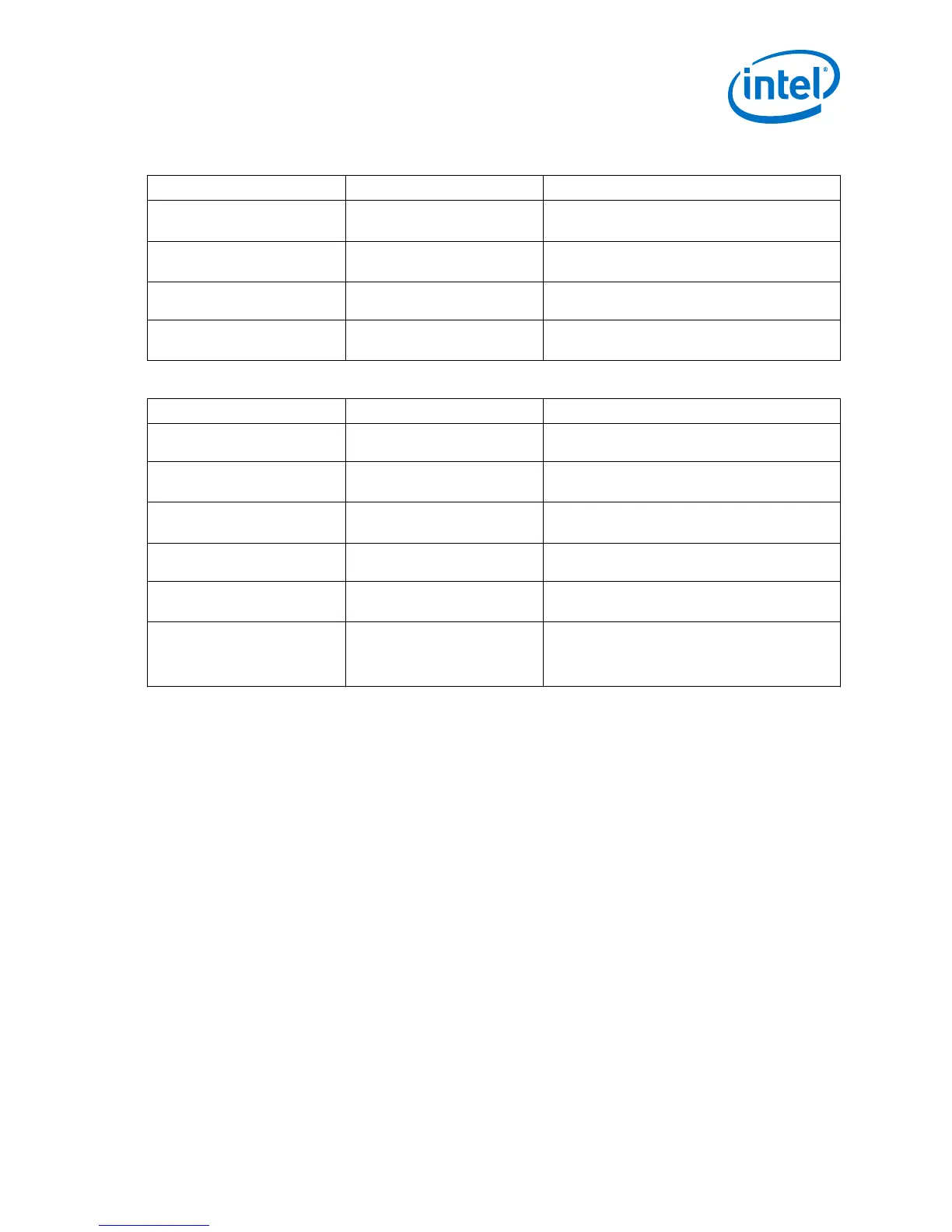

Table 21. HDMI RX Top Parameters

Parameter Value Description

SUPPORT_DEEP_COLOR • 0: No deep color

• 1: Deep color

Determines if the core can encode deep color

formats.

SUPPORT_AUXILIARY • 0: No AUX

• 1: AUX

Determines if the auxiliary channel encoding is

included.

SYMBOLS_PER_CLOCK 2 Supports only 2 symbols per clock for Intel Arria

10 devices.

SUPPORT_AUDIO • 0: No audio

• 1: Audio

Determines if the core can encode audio.

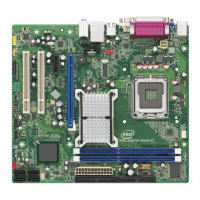

Table 22. HDMI TX Top Parameters

Parameter Value Description

USE_FPLL 1 Supports FPLL as TX PLL only for Intel Arria 10

devices. Always set this parameter to 1.

SUPPORT_DEEP_COLOR • 0: No deep color

• 1: Deep color

Determines if the core can encode deep color

formats.

SUPPORT_AUXILIARY • 0: No AUX

• 1: AUX

Determines if the auxiliary channel encoding is

included.

SYMBOLS_PER_CLOCK 2 Supports only 2 symbols per clock for Intel Arria

10 devices.

SUPPORT_AUDIO • 0: No audio

• 1: Audio

Determines if the core can encode audio.

POLARITY_INVERSION • 0: Invert polarity

• 1: Do not invert polarity

Set this parameter to 1 to invert the value of each

bit of the input data. Setting this parameter to 1

assigns 4'b1111 to the tx_polinv port of the TX

transceiver.

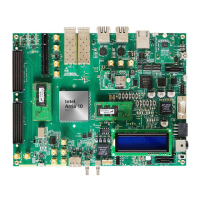

2.7 Hardware Setup

The Intel FPGA HDMI design example is HDMI 2.0 capable and performs a loop-

through demonstration for a standard HDMI video stream.

To run the hardware test, connect an HDMI-enabled device—such as a graphics card

with HDMI interface—to the Transceiver Native PHY RX block, and the HDMI sink

input.

1. The HDMI sink decodes the port into a standard video stream and sends it to the

clock recovery core.

2. The HDMI RX core decodes the video, auxiliary, and audio data to be looped back

in parallel to the HDMI TX core through the DCFIFO.

3. The HDMI source port of the FMC daughter card transmits the image to a monitor.

Note: If you use another Intel FPGA development board, you must change the device

assignments and the pin assignments. The transceiver analog setting is tested for the

Intel Arria 10 FPGA development kit and Bitec HDMI 2.0 daughter card. You may

modify the settings for your own board.

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

37

Loading...

Loading...