Mobile Intel

®

945GM Express Chipset

Development Kit User’s Manual 55

Hardware Reference

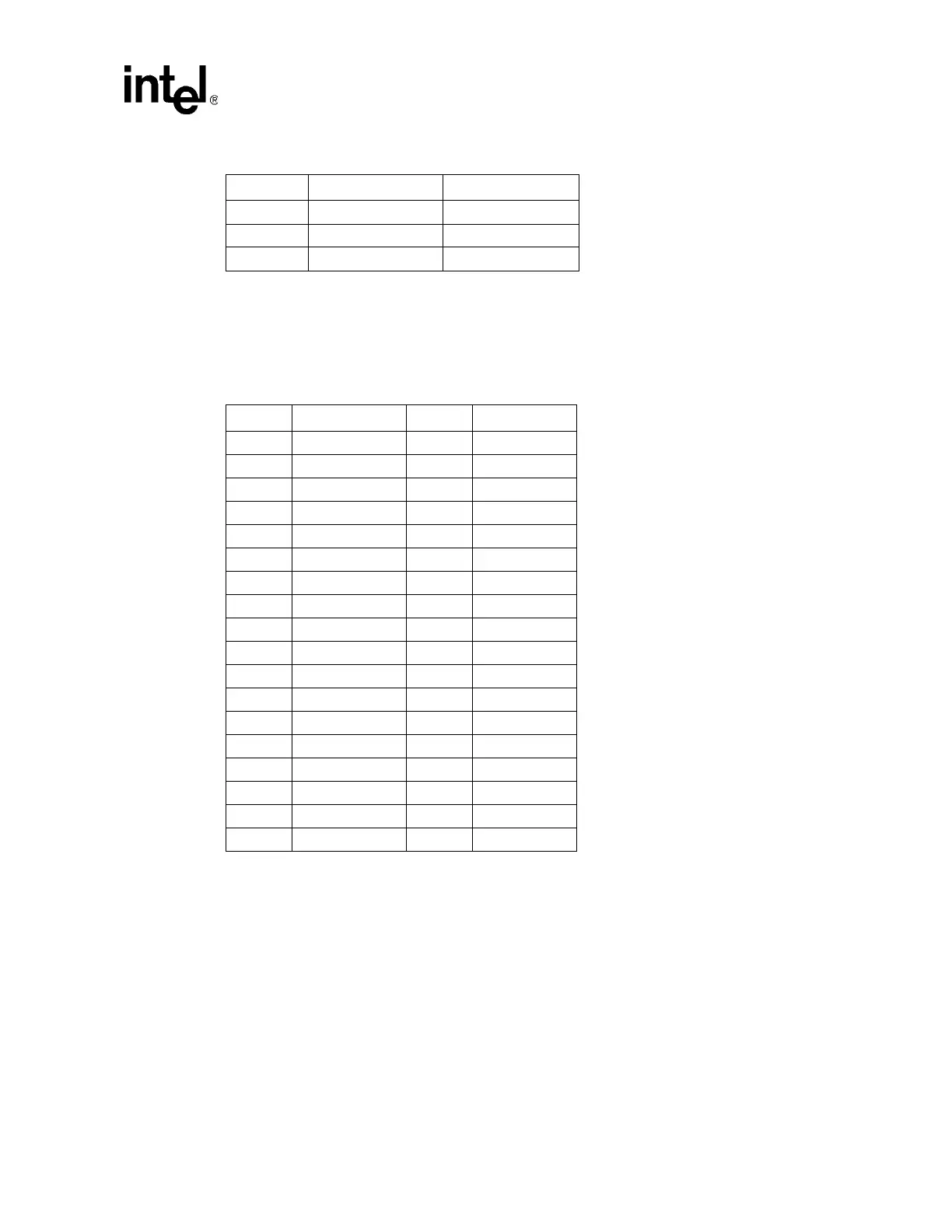

4.6.2.4 PCI Express* (x1)

The two PCI Express* x1 connectors allow the use of any industry standard PCI Express* device.

The pin configuration of the connectors is given below.

80 SDVO_TVClkIn+ GND

81 SDVO_TVClkIn- N/C

82 GND Reserved

Table 13. MEC Slot (J6C1) (Sheet 4 of 4)

Pin Number A B

Table 14. PCI Express* (x1) Pinout (J7C1, J8C1)

Pin Description Pin Description

A1 PRSNT1# B1 +12 V

A2 +12 V B2 +12 V

A3 +12 V B3 RSVD

A4 GND B4 GND

A5 (JTAG) TCK B5 SMCLK

A6 (JTAG) TDI B6 SMDAT

A7 (JTAG) TDO B7 GND

A8 (JTAG) TMS B8 +3.3 V

A9 +3.3 V B9 (JTAG) TRST#

A10 +3.3 V B10 +3.3 VAUX

A11 PERST# B11 WAKE#

A12 GND B12 RSVD

A13 REFCLK+ B13 GND

A14 REFCLK- B14 LANE 0 (T+)

A15 GND B15 LANE 0 (T-)

A16 LANE 0 (R+) B16 GND

A17 LANE 0 (R-) B17 PRSNT2*

A18 GND B18 GND

Loading...

Loading...