A HARDWARE REFERENCE

3-11

3.9 Z8536 COUNTER I/O UNIT (CIO)

The Z8536 device performs several functions on the Cyclone EP. The device provides three 16-bit

counter/timers that may be used to generate interrupts or count events. The CIO generates interrupts on

the processor’s XINT6

signal. The CIO also contains three parallel ports which are used for on-board

control and status such as reading and writing the on-board and Squall Module EEPROMs, and to read

the board’s configuration. The following subsections outline the Cyclone EP’s specific usage of the

CIO. For detailed programming instructions, refer to the Zilog Z8536 Technical Manual.

3.9.1 Counter/Timers

Three 16-bit counter/timers can be used to generate interrupts on the processor's XINT6

signal.

Counters 1 and 2 can be linked internally to provide a 32-bit counter for longer timing sequences. The

CIO is clocked with a 4.000 MHz (±0.01%) clock. Internally, this signal is divided by 2, which actually

clocks the counters with a 2.000 MHz clock. Example code for using the counter/timers may be found

in the MON960 Board Test (bt) code.

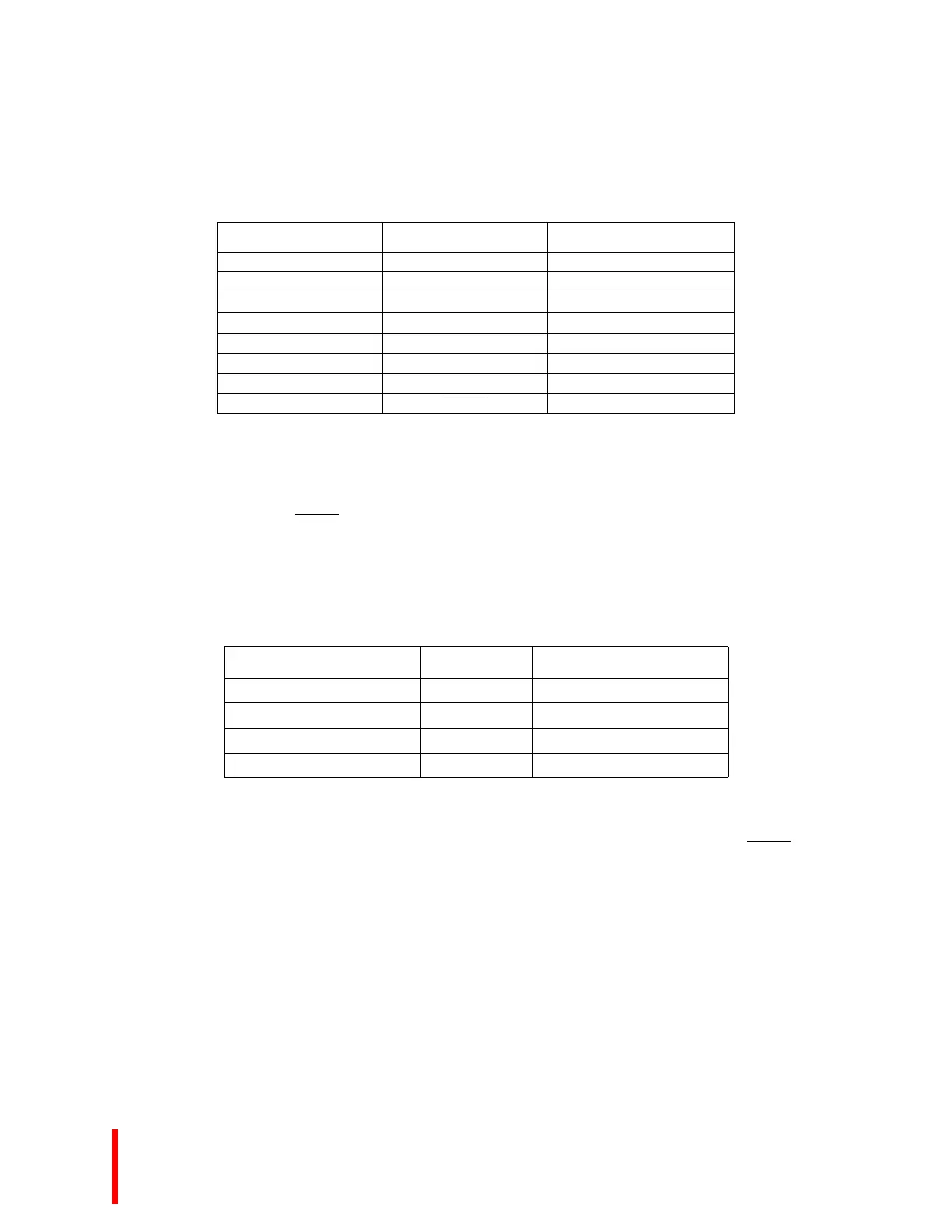

Table 3-13. Parallel Port Control Register Bit Assignments

Bit Signal Mnemonic Signal Name

7 not used —

6 not used —

5 not used —

4 BUSY_CTRL Busy Control

3 PINTEN Enable Interrupt

2 PPOUT Paper Out

1 PPSEL Select Out

0 PPERR

Error Output

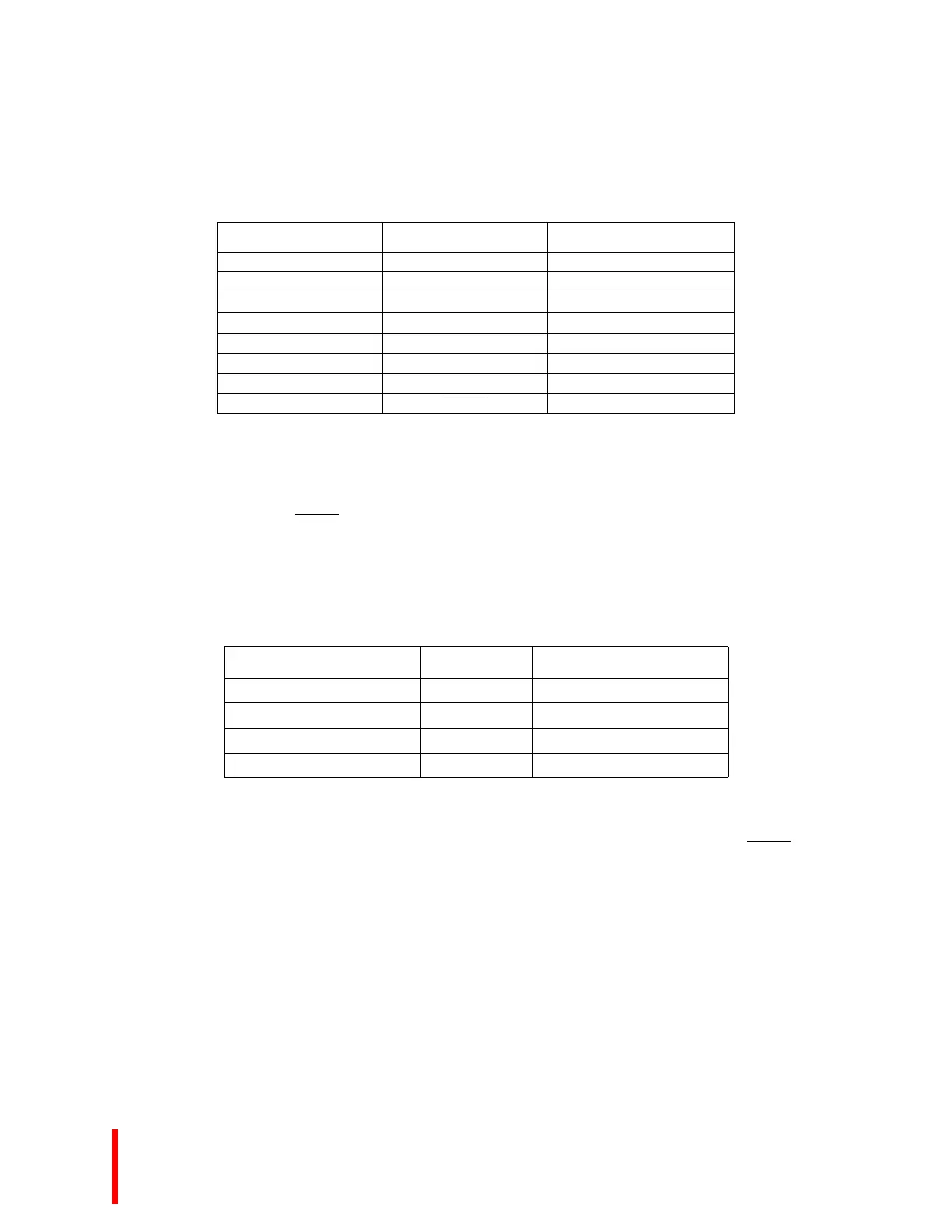

Table 3-14. CIO Register Address

Register Address Description

Port C Data B004 0000H User LEDs

Port B Data B004 0004H EEPROM Clock & Data

Port A Data B004 0008H Control Bits

CIO Control Register B004 000CH CIO Configuration & Control

Loading...

Loading...