Table of Contents Intel® Server Board S2600CW Family TPS

Revision 2.4

Table of Contents

1. Introduction ........................................................................................................................................ 1

1.1 Chapter Outline .................................................................................................................................... 1

1.2 Server Board Use Disclaimer .......................................................................................................... 2

2. Intel® Server Board S2600CW Overview ...................................................................................... 3

2.1 Intel® Server Board S2600CW Feature Set .............................................................................. 3

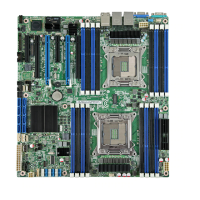

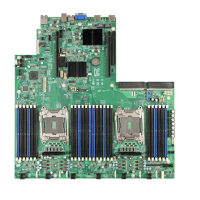

2.2 Server Board Layout .......................................................................................................................... 5

2.2.1 Server Board Connector and Component Layout ................................................................. 7

2.2.2 Server Board Mechanical Drawings ............................................................................................. 8

2.2.3 Server Board Rear I/O Layout ..................................................................................................... 14

3. Intel® Server Board S2600CW Functional Architecture ......................................................... 15

3.1 Processor Support ........................................................................................................................... 16

3.1.1 Processor Socket Assembly ........................................................................................................ 16

3.1.2 Processor Population Rules ......................................................................................................... 17

3.2 Processor Functions Overview ................................................................................................... 20

3.2.1 Intel® Virtualization Technology (Intel® VT) for Intel® 64 and IA-32 Intel®

Architecture (Intel® VT-x) ................................................................................................................................. 21

3.2.2 Intel® Virtualization Technology for Directed I/O (Intel® VT-d) .................................... 21

3.2.3 Intel® Trusted Execution Technology for Servers (Intel® TXT) ...................................... 22

3.2.4 Execute Disable ................................................................................................................................. 22

3.2.5 Advanced Encryption Standard (AES) ..................................................................................... 22

3.2.6 Intel® Hyper-Threading Technology ........................................................................................ 22

3.2.7 Intel® Turbo Boost Technology .................................................................................................. 22

3.2.8 Enhanced Intel SpeedStep® Technology ............................................................................... 23

3.2.9 Intel® Advanced Vector Extensions 2 (Intel® AVX2) ........................................................... 23

3.2.10 Intel® Node Manager 3.0 ............................................................................................................... 23

3.2.11 Intel® Secure Key .............................................................................................................................. 24

3.2.12 Intel® OS Guard ................................................................................................................................. 24

3.2.13 Trusted Platform Module (TPM) ................................................................................................ 24

3.3 Integrated Memory Controller (IMC) and Memory Subsystem ..................................... 24

3.3.1 Supported Memory ......................................................................................................................... 25

3.3.2 Memory Population Rules ............................................................................................................ 26

3.3.3 Effects of Memory Configuration on Memory Sizing ........................................................ 28

3.3.4 Publishing System Memory ......................................................................................................... 29

3.3.5 RAS Features ...................................................................................................................................... 29

3.3.6 Memory Initialization ...................................................................................................................... 30

Loading...

Loading...