6 - 93 6 - 93

MELSEC-Q/QnA

6 BASIC INSTRUCTIONS

High Performance

QnA Q4AR

Basic

QCPU

PLC CPU

Process CPU

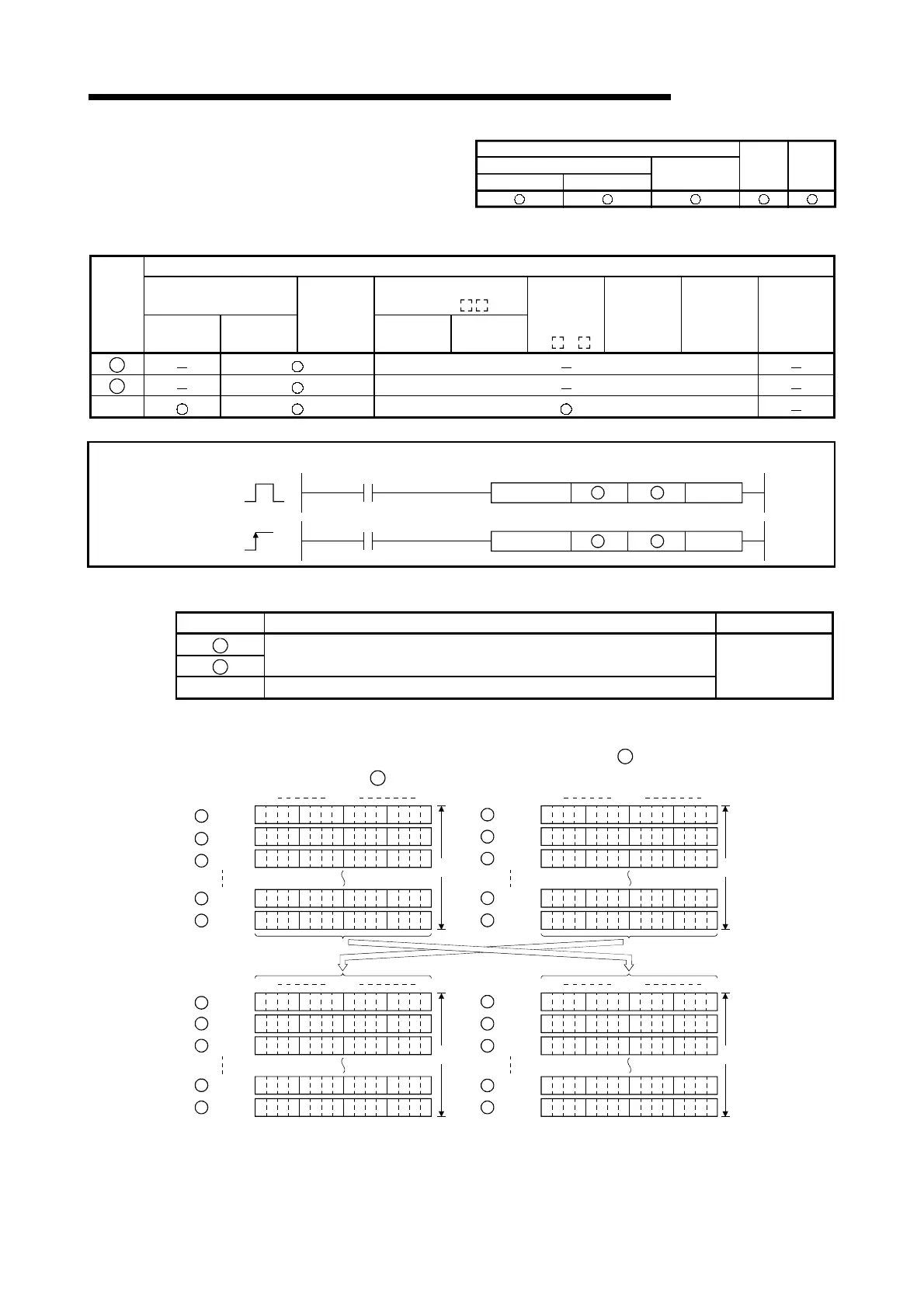

6.4.8 Block 16-bit data exchanges (BXCH, BXCHP)

Usable Devices

Internal Devices

(System, User)

MELSECNET/10(H)

Direct J

\

Set

Data

Bit Word

File

Register

Bit Word

Special

Function

Module

U

\G

Index

Register

Zn

Constant

K, H

Other

D1

D2

n

[Instruction Symbol] [Execution Condition]

Command

Command

BXCHP

BXCH

n

n

BXCHP

BXCH

D1 D2

D1 D2

[Set Data]

Set Data Meaning Data Type

D1

D2

Head number of device storing data to be exchanged

n

Number of exchanges

BIN 16 bits

[Functions]

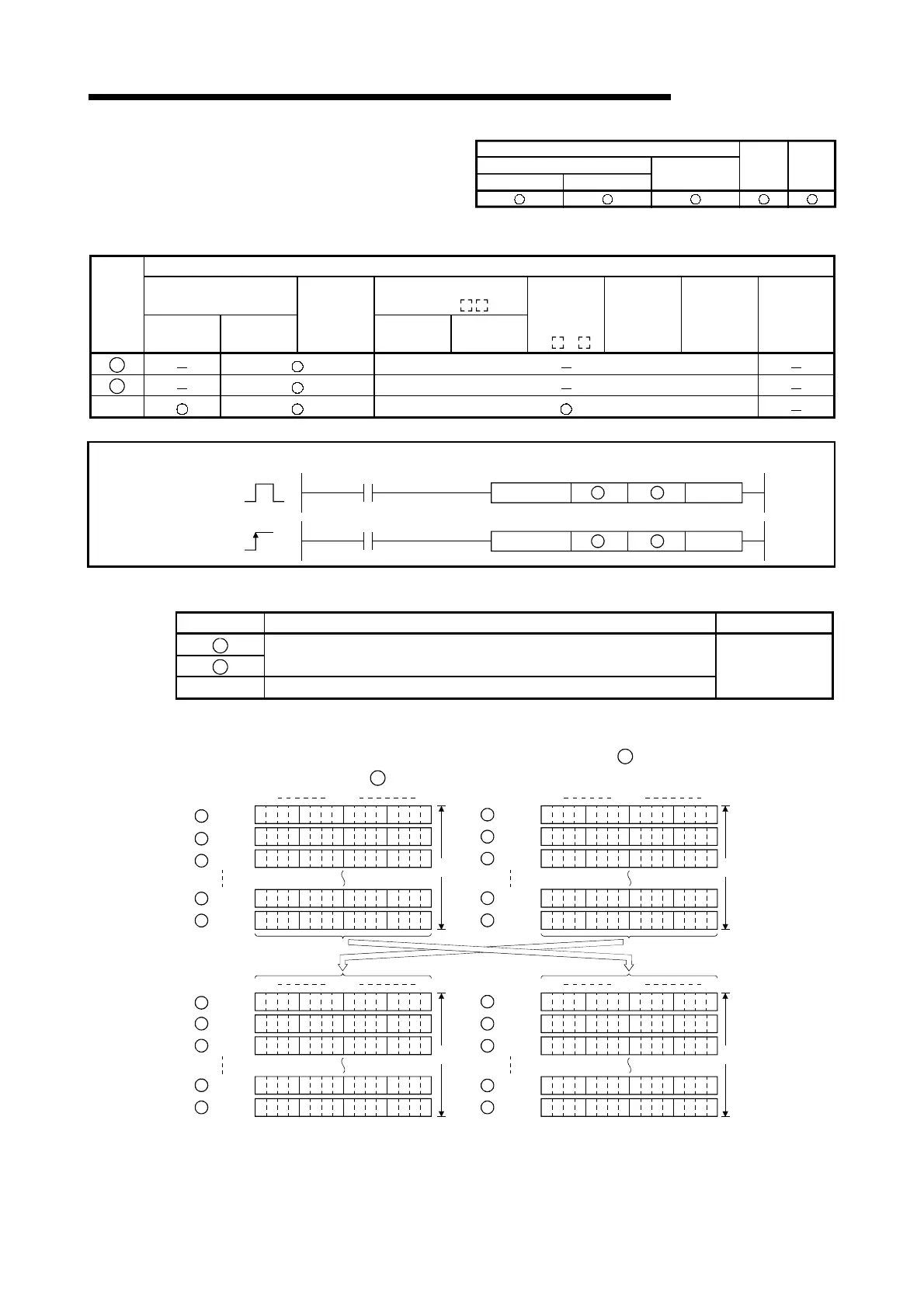

(1) Exchanges 16-bit data n-points from device designated by

D1

and 16-bit data n-points from

device designated by

D2

.

1 1 1 1 1 1 1 1

0 0 0 000 0 0

0 0 0 0 0 0 0 0 1 1 1 111 1 1

1 0 1 0 1 0 1 0 1 0 1 010 1 0

0 1 0 1 0 1 0 1 0 1 0 101 0 1

n

0000111111110000

+1

+(n-1)

+2

+(n-2)

1 1 0 0 0 0 1 1 1 1 0 000 1 1

1 1 1 1 1 1 1 1 0 0 0 000 0 0

1 1 1 1 1 1 1 1 1 1 1 111 1 1

0 0 0 0 0 0 0 0 1 1 1 111 1 1

b7 b0b15 b8

0011001111001100

1 1 1 1 1 1 1 1 0 0 0 000 0 0

0 0 0 0 0 0 0 0 1 1 1 111 1 1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0000111111110000

1 1 0 0 0 0 1 1 1 1 0 000 1 1

1 1 1 1 1 1 1 1 0 0 0 000 0 0

1 1 1 1 1 1 1 1 1 1 1 111 1 1

0 0 0 0 0 0 0 0

1 1 1 111 1 1

0011001111001100

D1

D2

D1

D1

D1

D1

+1

+(n-1)

+2

+(n-2)

D1

D1

D1

D1

D1

+1

+(n-1)

+2

+(n-2)

D2

D2

D2

D2

b7 b0b15 b8

n

b7 b0b15 b8b7 b0b15 b8

D2

+1

+(n-1)

+2

+(n-2)

D2

D2

D2

D2

nn

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...