2 - 5 2 - 5

MELSEC-Q/QnA

2 INSTRUCTION TABLES

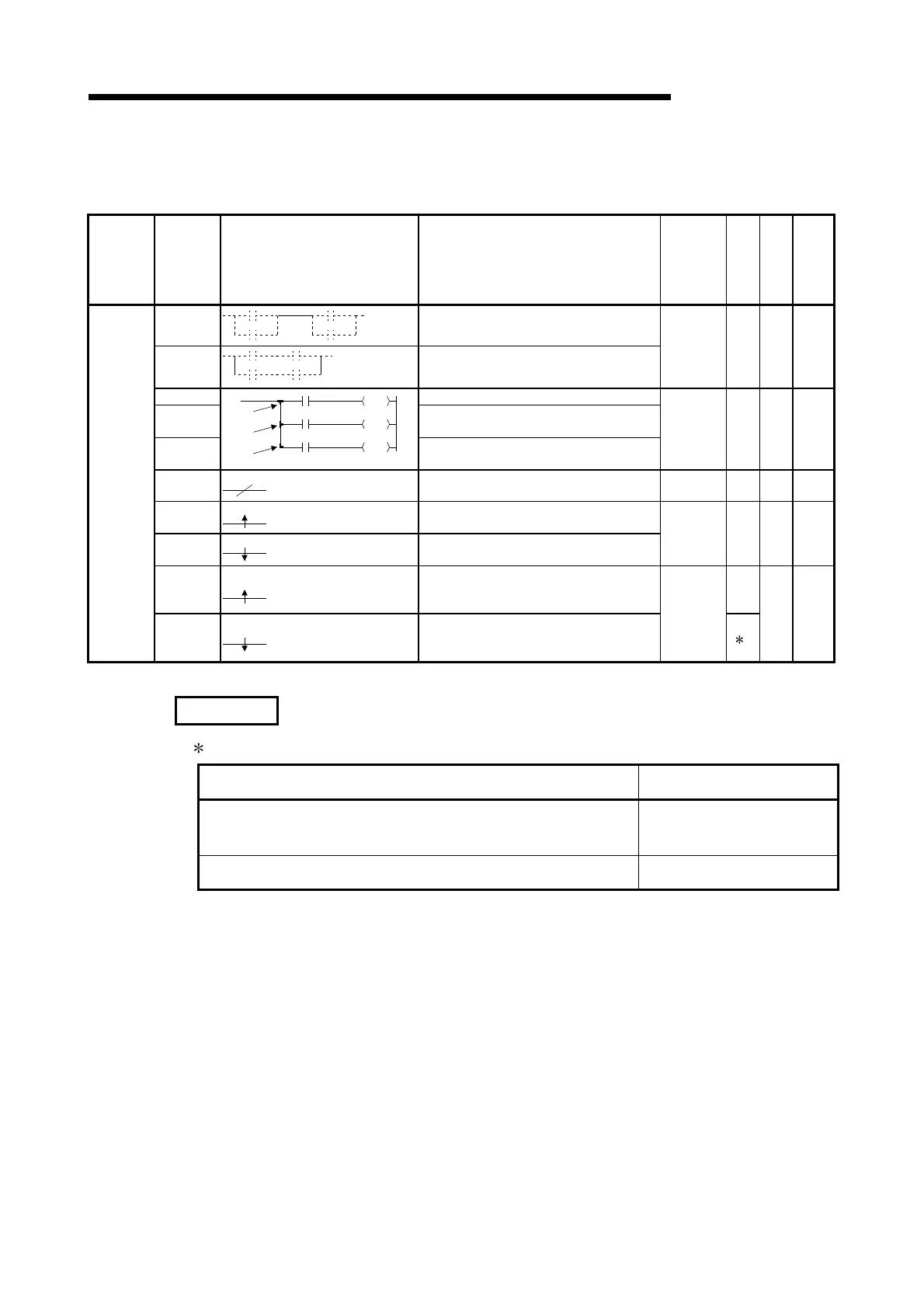

2.3.2 Connection instructions

Table 2.4 Connection Instructions

Category

Instruction

Symbols

Symbol Processing Details

Execution

Condition

Number of

Basic Steps

Subset

See for

Description

ANB

ANB

• AND between logical blocks (Series

connection between logical blocks)

ORB

ORB

• OR between logical blocks

(Series connection between logical blocks)

15-7

MPS • Memory storage of operation results

MRD

• Read of operation results stored with MPS

instruction

MPP

MPS

MRD

MPP

• Read and reset of operation results stored

with MPS instruction

15-9

INV • Inversion of operation result 1 5-13

MEP

• Conversion of operation result to leading

edge pulse

MEF

• Conversion of operation result to trailing

edge pulse

15-14

EGP

Vn

• Conversion of operation result to leading

edge pulse

(Stored at Vn)

1

Connection

EGF

Vn

• Conversion of operation result to trailing

edge pulse

(Stored at Vn)

1

5-16

REMARKS

1:The number of steps may vary depending on the type of CPU module being used.

Component Number of basic steps

High Performance model QCPU

Process CPU

QnACPU

1

Basic model QCPU 2

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...