5 - 24 5 - 24

MELSEC-Q/QnA

5 SEQUENCE INSTRUCTIONS

High Performance

QnA Q4AR

Basic

QCPU

PLC CPU

Process CPU

5.3.3 Counters (OUT C)

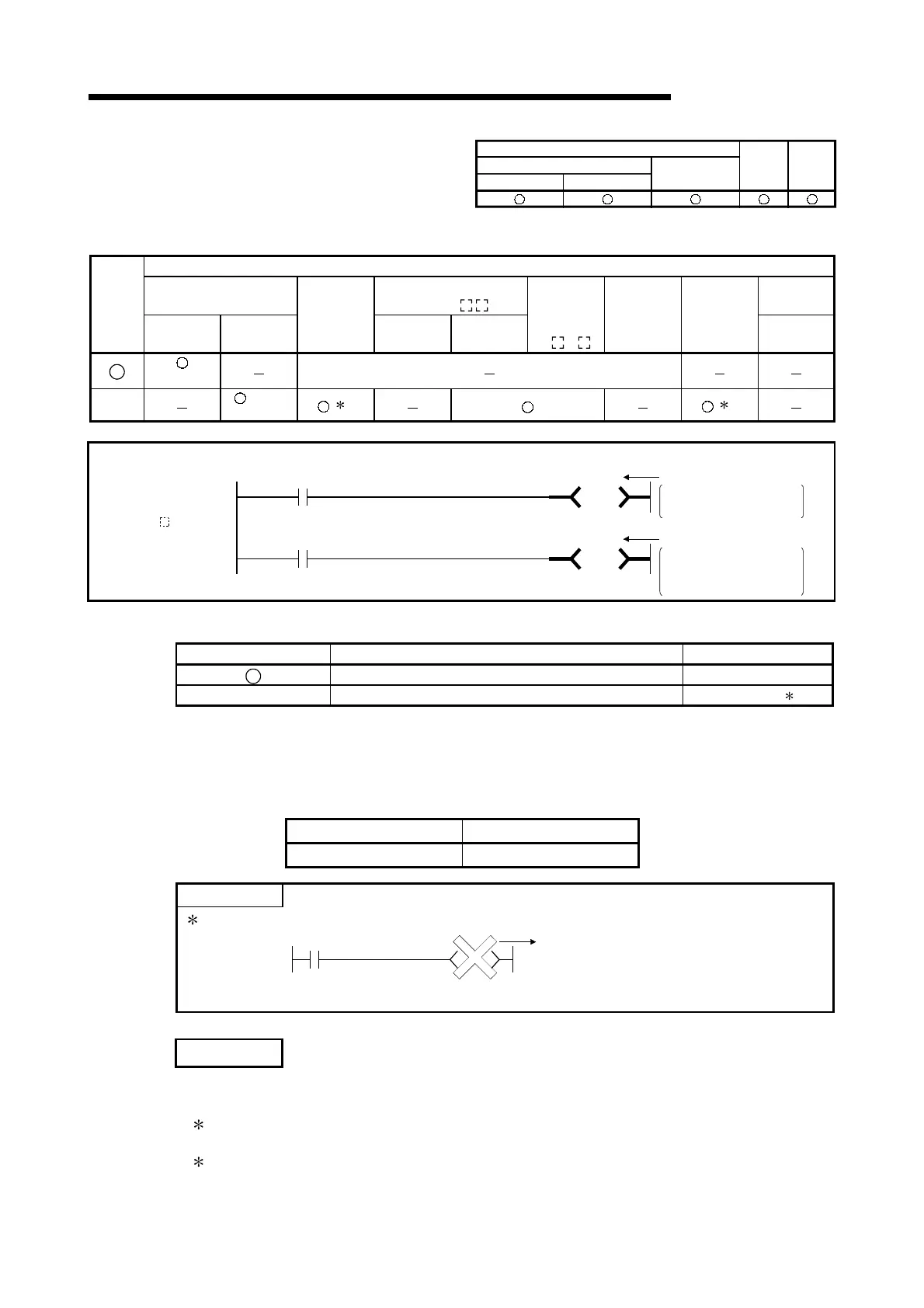

Usable Devices

Internal Devices

(System, User)

MELSECNET/10(H)

Direct J

\

Other

Set

Data

Bit Word

File

Register

Bit Word

Special

Function

Module

U

\G

Index

Register

Zn

Constant

K

U

D

(Only C)

Set

value

(Other

than T,C)

3 1

[Instruction Symbol] [Execution Condition]

C0

Set value

Settings from 1 to 32767

are valid

K50

C1

Set value

Contents of data register

settings from 1 to 32767

are valid

D10

OUT C

[Set Data]

Set Data Meaning Data Type

D

Counter number Bit

Set value Counter set value BIN 16 bits 2

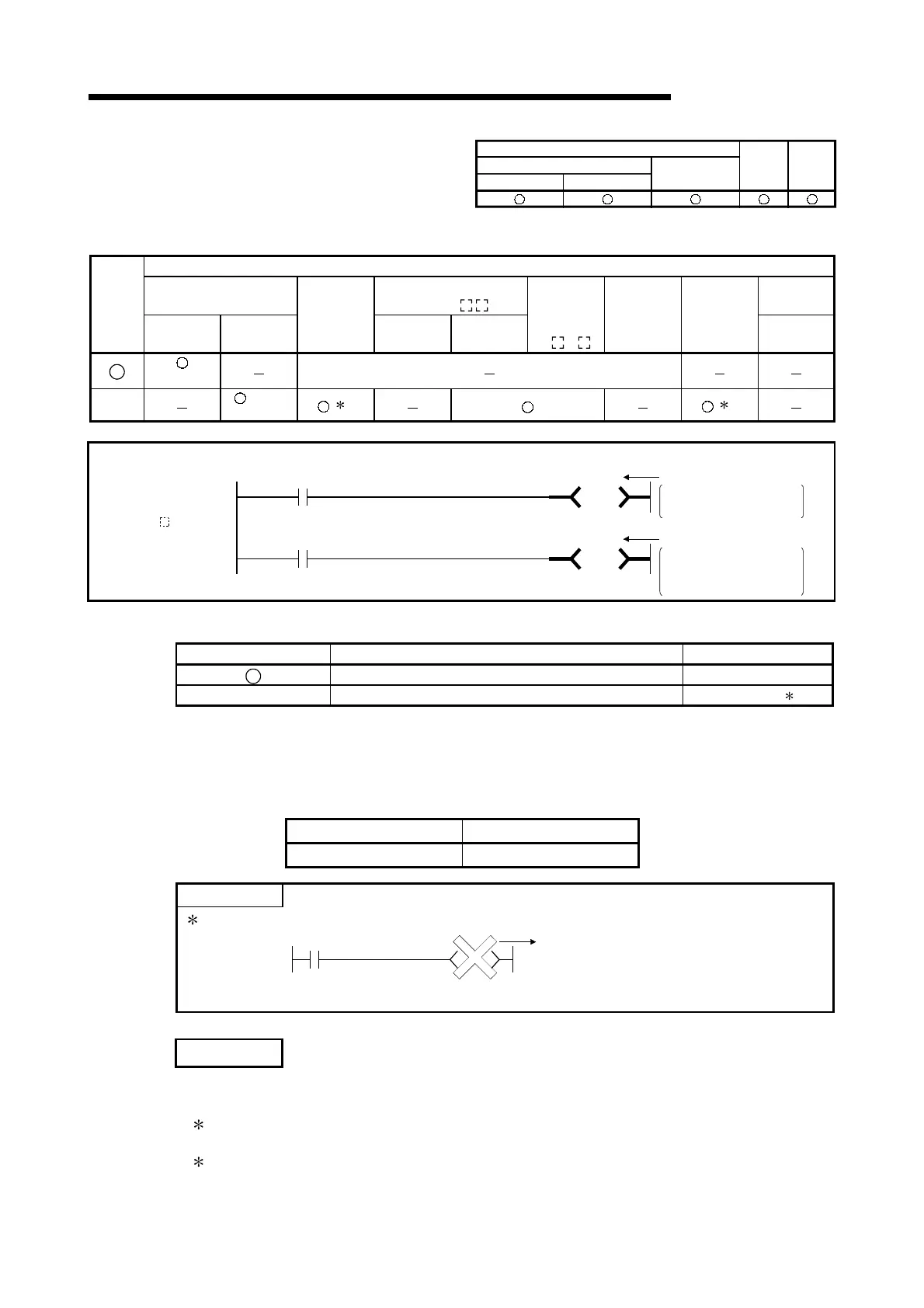

[Functions]

(1) When the operation results up to the OUT instruction change from OFF to ON, 1 is added to

the present value (count value) and the count up status (present value = set value), and the

contacts respond as follows:

A contact Continuity

B contact Non-continuity

POINT

2: Counter value cannot be set by indirect designation.

@ D0

C0

Indirect designation not possible

See Section 3.4 for further information on indirect designations.

REMARKS

Refer to the User's Manual (Functions Explanation, Programming Fundamentals) of the used

CPU module or QnACPU Programming Manual (Fundamentals) for counter counting methods.

1: Counter value can be set only with a decimal constant (K).

A hexadecimal constant (H) or a real number cannot be used for the counter value setting.

3: The file register cannot be used in the Q00JCPU.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...