19

3C00 - 3FFF

Video RAM

4000 - 7FFF

RAM (16K) End of one 32K Bank

8000 - FFFF

RAM (32K) Second 32K Bank

Memory Map III

0000 - 7FFF

RAM (32K) End of One 32K Bank

8000 - F3FF

RAM (29K) Second 32K Bank

F400 - F7FF

Keyboard

F800 - FEFF

Video RAM

Memory Map IV

0000 - 7FFF

RAM (32K) One 32K Bank

8000 - FFFF

RAM (32K) Second 32K Bank

(See Figure 3-2 for 128K Maps)

3.1.5 ROM

The Model 4 Microcomputer contains 14K of Read

Only Memory (ROM), which is divided into an 8K

ROM (U68), a 4K ROM (U69), and a 2K ROM (U70).

ROMs used have three-state outputs which are

disabled if the ROMs are deselected. As a result,

ROM data outputs are connected directly to the CPU

data bus and do not use data buffer U71, which is

disabled during a ROM access.

ROMs are Model III compatible and contain a BASIC

operating system, as well as a floppy disk boot

routine. The enable inputs to the ROMs are provided

by the address decoding section, and are present

only in the Model III mode of Operation.

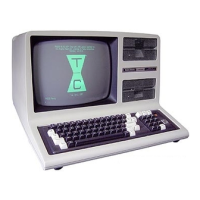

3.1.6 RAM

Three configurations of Random Access Memory are

available on the Model 4:16K, 64K, and 128K. The

16K option uses 4116 type, 16K by 1 dynamic RAMs,

which require three supply voltages (+12 volts, +5

volts, and -5 volts). The 64K and 128K options use

6665 type, 64K by 1 dynamic RAMs, which require

only a single supply voltage (+5 volts). The proper

voltage for each option is provided by jumpers.

Dynamic RAMs require multiplexed incoming address

lines. This is accomplished by ICs U63 and U76.

Output data from RAMs is buffered by U64. With the

128K option, there are two rows of the 64K by 1 RAM

ICs. The proper row is selected by the CAS signal

from PAL U72.

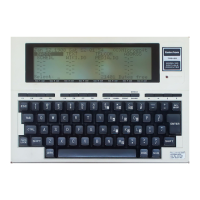

3.1.7 Keyboard

The Model 4 Keyboard is a 70-key sculptured

keyboard, scanned by the microprocessor. Each key

is identified by its column and row position. Columns

are defined by address lines AO - A7, which are

buffered by open-collector drivers U29 and U30. Data

lines DO - D7 define the rows and are buffered by

CMOS buffers U44 and U45. Row inputs to the

buffers are pulled up by resistor pack RP 1, unless a

key in the current column being scanned is

depressed. Then, the row for that key goes low.

3.1.8 Video

The heart of the video display circuitry in the Model 4

is the 68045 Cathode Ray Tube Controller. The

CRTC allows two screen formats: 64 by 16 and 80 by

24. Since the 80 by 24 screen requires 1,920 screen

memory locations, a 2K by 8 static RAM is used for

the Video RAM. The 64 by 16 mode has a two-page

screen display and a bit in the options register for

determining which page is active for the CPU. Offset

the start address of the CRTC to gain access to the

second page in the 64 by 16 mode.

Addresses to the video RAM are provided by the

68045 when refreshing the screen and by the CPU

when updating the data. These two sets of addresses

are multiplexed by U33, U34, and U35. Data between

the CPU and Video RAM is latched by U6 for a write,

and buffered by U7 for a read operation.

During screen refresh, the data outputs of the Video

RAM (ASCII character codes) are latched by U8 and

become the addresses for the character generator

ROM (U23). In cases of low resolution graphics, a

dual 1 of 4 data selector (U9) is the cell generator,

with additional buffering from U10

The shift register U1 inputs are the latched data

outputs of the character or cell generator. The shift

clock input comes from the PAL U4, and is 10.1376

MHz for the 64 by 16 mode and 12.672 MHz for 80

by 24 operation. The serial output from the shift

register later becomes actual video dot information.

Special timing in the video circuit is handled by hex

latch U2. This includes blanking (originating from

CRTC) and shift register loading (originating from

U4). Additional video control and timing functions,

such as sync buffering, inversion selection, dot clock

chopping, and graphics disable of normal video, are

handled by miscellaneous gates in U12, U13, U14,

U22, U24, and U26.

Loading...

Loading...