RL78/G13 Clock Generator (Clock Switching) CC-RL

R01AN2831EJ0100 Rev. 1.00 Page 11 of 51

May 28, 2015

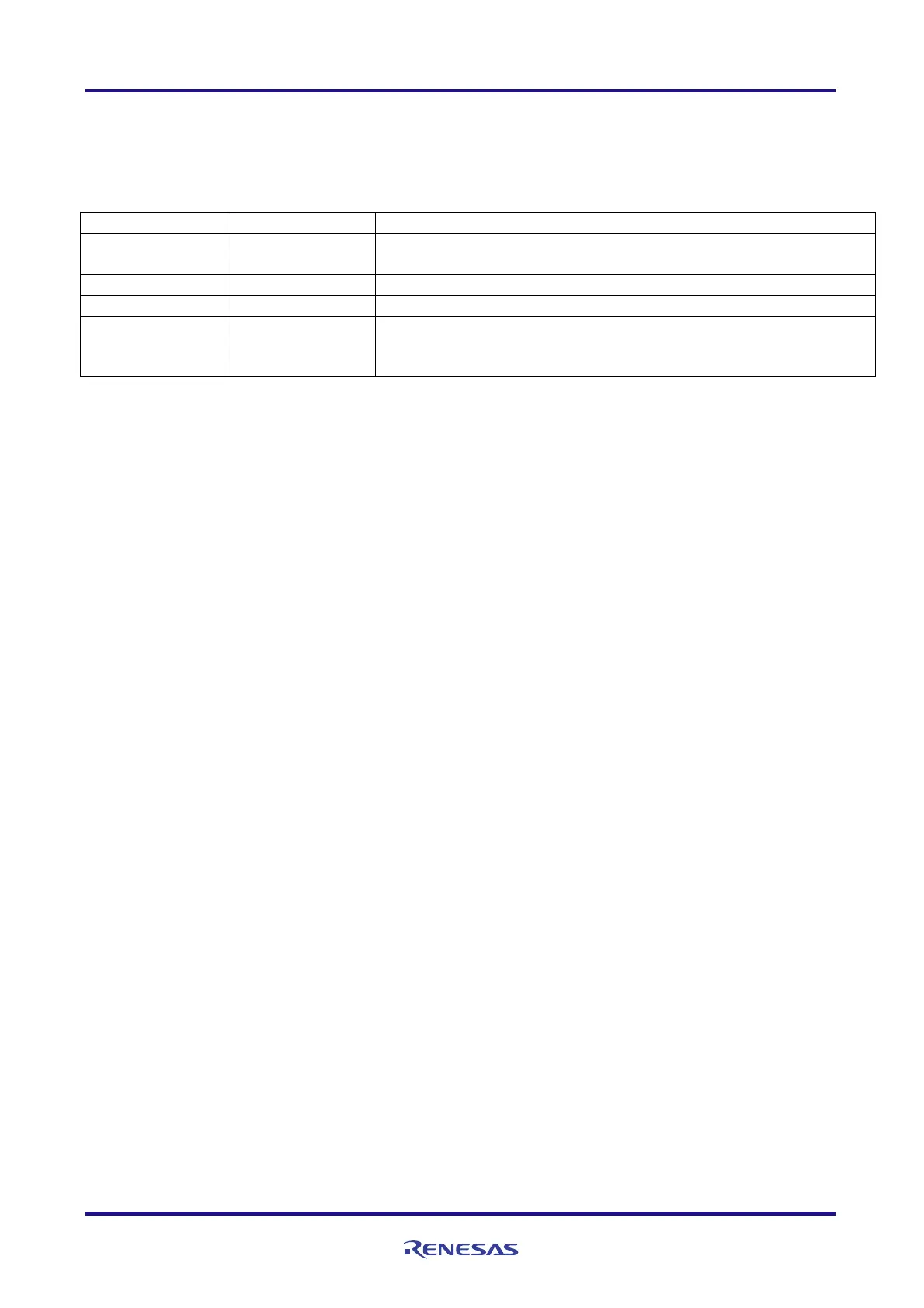

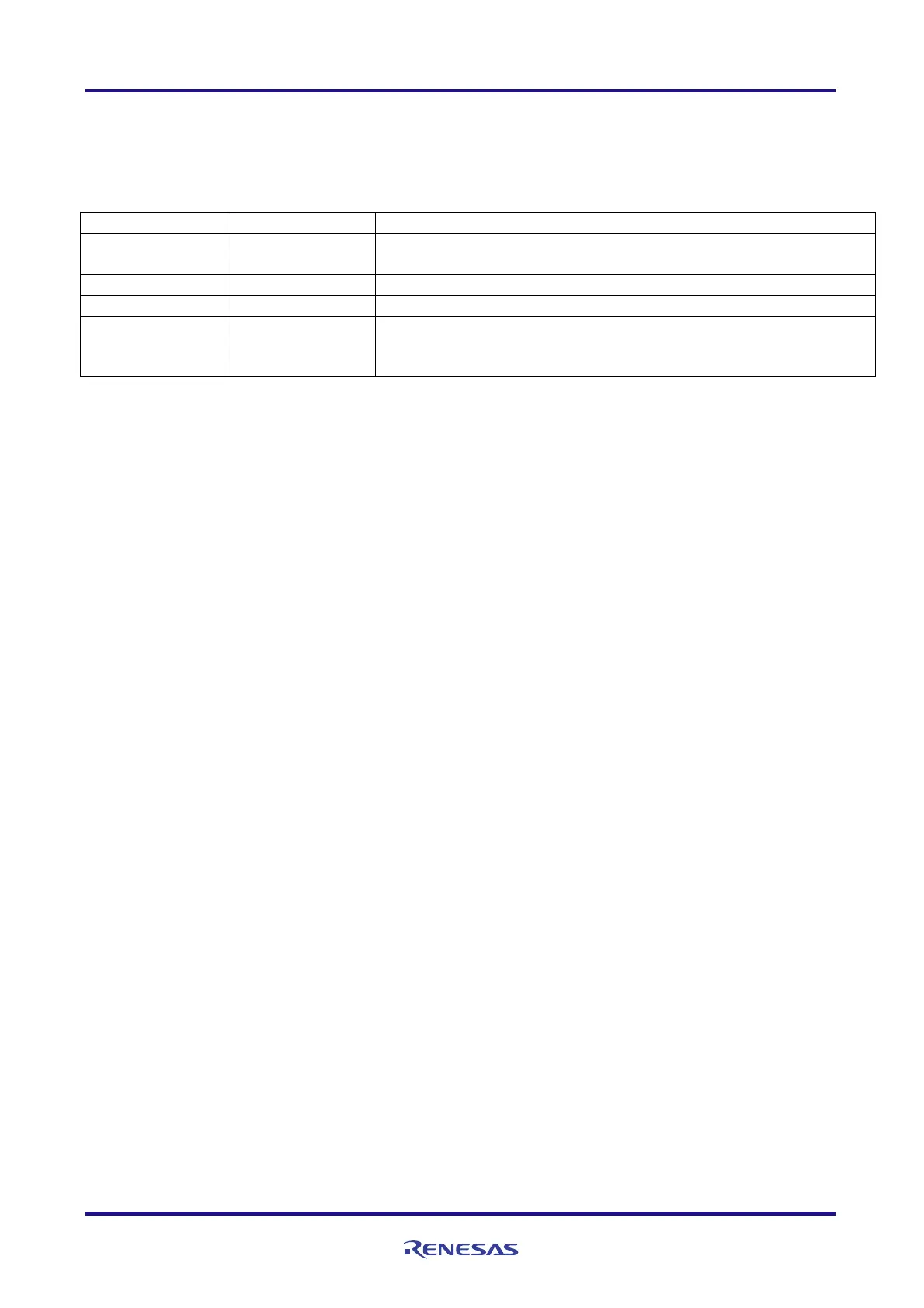

5.3 List of Option Byte Settings

Table 5.2 summarizes the settings of the option bytes.

Table 5.2 Option Byte Settings

Address Value Description

000C0H/010C0H 11101111B Disables the watchdog timer.

(Stops counting after the release from the reset status.)

000C1H/010C1H 01111111B LVD reset mode, 2.81 V (2.76 V to 2.87 V)

000C2H/010C2H 11101000B HS mode HOCO: 32 MHz

000C3H/010C3H 10000100B Enables the on-chip debugger.

Erases the data in the flash memory when on-chip debugging security ID

authentication fails.

Loading...

Loading...