A

1

2

3

4

5

6

7

8

9

10

BCDEFGH I JK

L MN

61

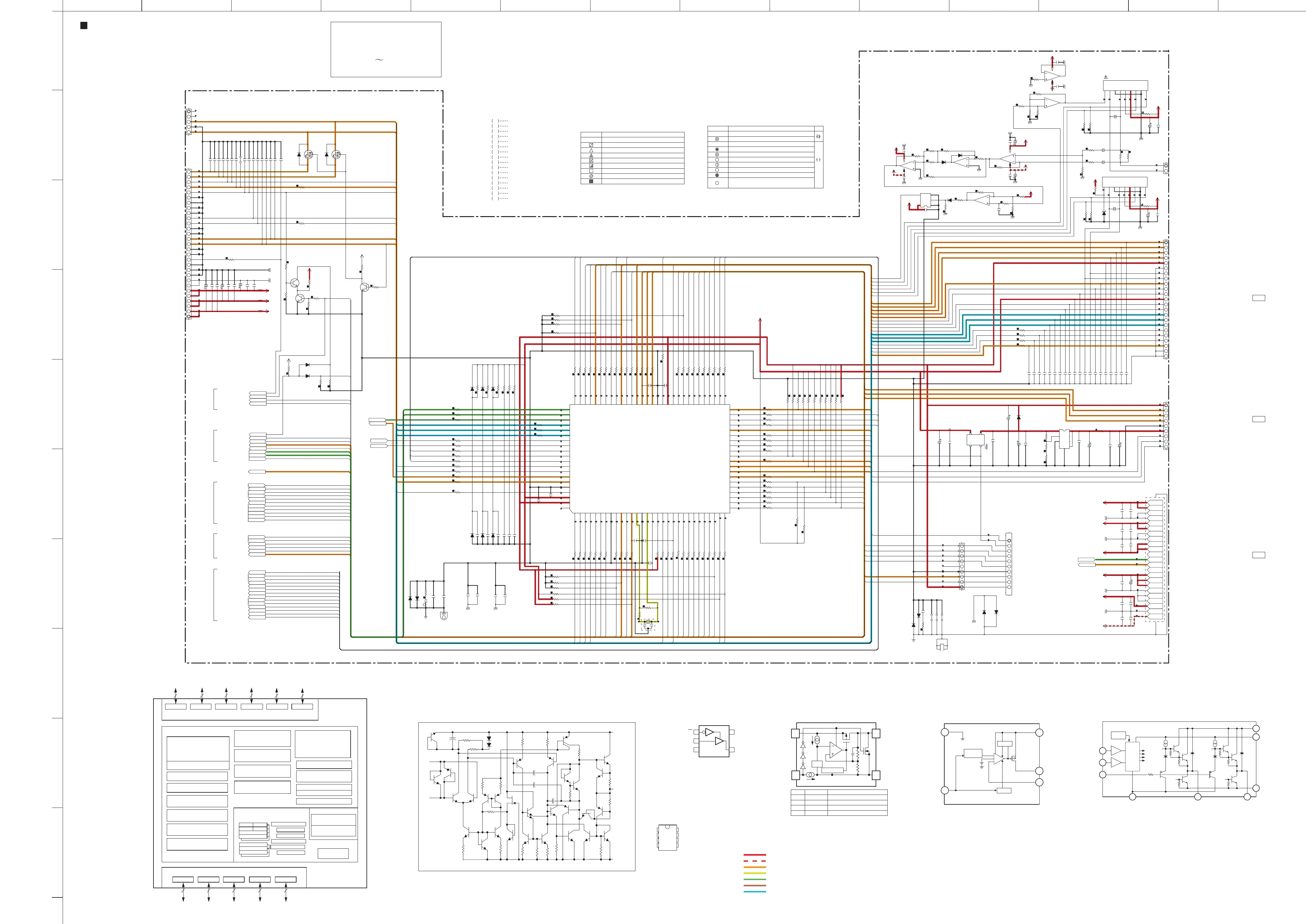

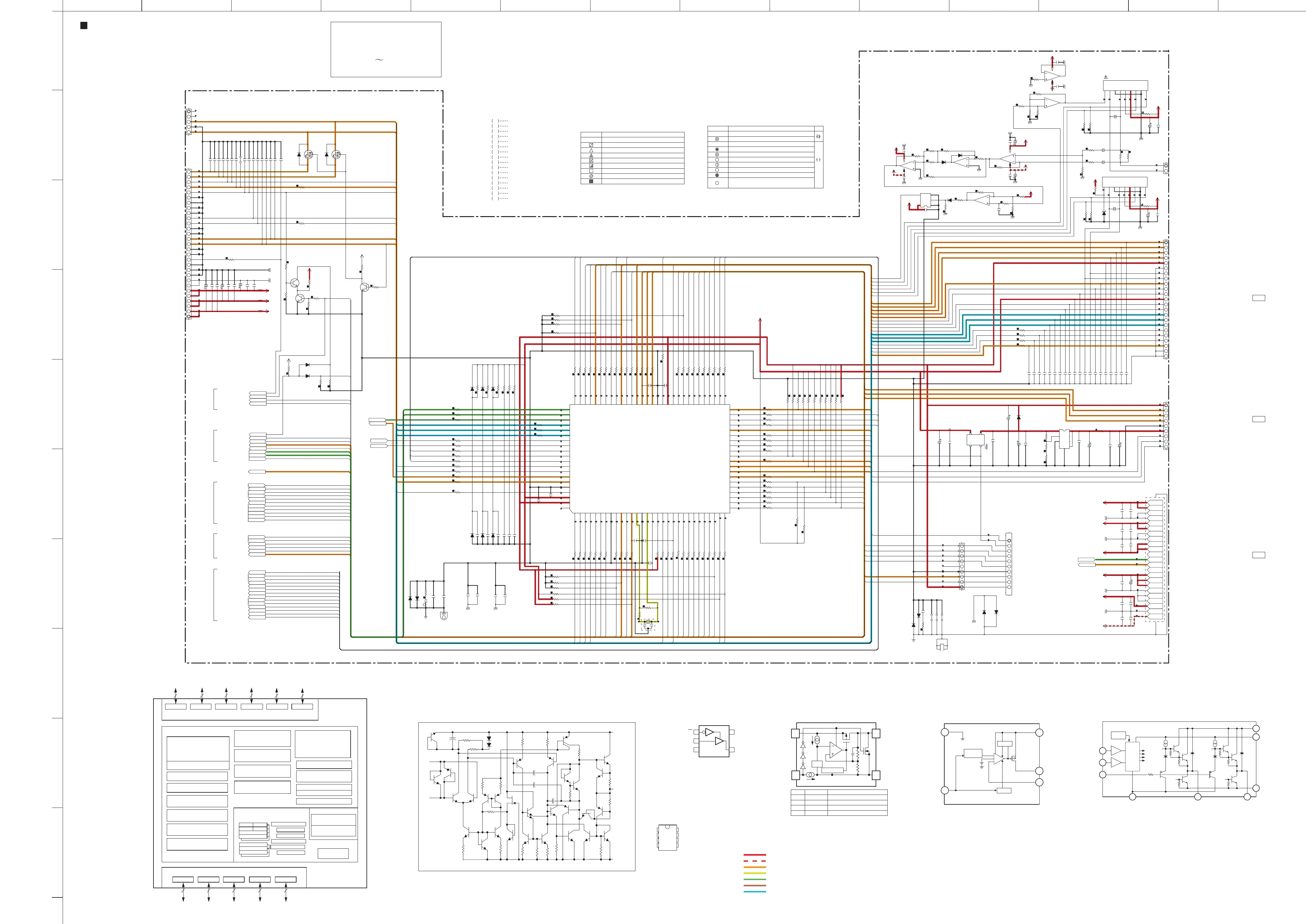

DIGITAL 1/3

CD-S2100

SCHEMATIC DIAGRAMS

★ All voltages are measured with a 10MΩ/V DC electronic voltmeter.

★ Components having special characteristics are marked

⚠

and must be replaced

with parts having specifications equal to those originally installed.

★ Schematic diagram is subject to change without notice.

●電圧は、内部抵抗 10MΩの電圧計で測定したものです。

●⚠印のある部品は、安全性確保部品を示しています。部品の交換が必要な場合、

パーツリストに記載されている部品を使用してください。

●本回路図は標準回路図です。改良のため予告なく変更することがあります。

3.3

3.3

8.2

4.0

7.0

4.9

3.3

5.0

12.0

-12.1

1.7

RESISTOR

REMARKS

NO MARK

PARTS NAME

CARBON

CARBON

METAL

METAL

METAL

FIRE

CEMENT

SEMI

FILM RESISTOR

FILM RESISTOR

OXIDE FILM RESISTOR

FILM RESISTOR

PLATE RESISTOR

PROOF CARBON FILM RESISTOR

MOLDED RESISTOR

VARIABLE RESISTOR

(P=5)

(P=10)

CHIP RESISTOR

NOTICE

U.S.A

G

CANADA

EUROPE

L

CHINA

AUSTRALIA

SINGAPORE

KOREA

GENERAL

U

C

T

A

K

R

JAPAN

(model)

B BRITISH

J

SOUTH EUROPEE

V TAIWAN

F RUSSIAN

P LATIN AMERICA

S BRAZIL

H THAI

REMARKS

CAPACITOR

PARTS NAME

NO

NO

MARK

MARK

ELECTROLYTIC CAPACITOR

CERAMIC CAPACITOR

POLYESTER FILM CAPACITOR

POLYSTYRENE FILM CAPACITOR

MICA CAPACITOR

POLYPROPYLENE FILM CAPACITOR

SEMICONDUCTIVE CERAMIC CAPACITOR

P

TANTALUM CAPACITOR

TUBULAR

S

CAPACITORCERAMIC

FILMSULFIDEPOLYPHENYLENE

CAPACITOR

BP

BP

BP

P

BP

WR_CK

REM

DIR_N_INT

SSP2_N_DSPSTOP

SSP2_YISO_MUTE

WR_MOSI

WR_MISO

SSP2_DSD_PCM

SSP2_USB_RDY

CNVSS

WR_BUSY

CD_YOVI

CD_YIVO

FL_EX_CLK

CLAMP_SW

DIR_MOSI

DIR_MISO

DIR_SCK

DIR_N_CS

KEY0

KEY1

KEY2

FL_EX_CLK

FL_EX_MOSI

PWR_RY

ACPWR_DET

LED_PWR

SSP2_PON

DIR_N_RST

CD_PWR

PULSE_DET

MTR_CTL_DA

TRAY_MTR2

FL_EX_MOSI

FL_N_CS

FL_N_RST

FL_N_CS

FL_N_RST

DAC_N_RST

DAC_SDA

DAC_SCL

PRVR

PRVL

CD_YOVI

CD_SPDIF_RQ

CLAMP_MTR1

CLAMP_MTR2

TRAY_MTR1

DIR_N_RST

DIR_N_CS

DIR_SCK

DIR_MOSI

DIR_MISO

DIR_N_INT

CD_MUTE

RY_AUDIO

ACPWR_DET

N_RST

PWR_RY

UNCLAMP_SW

CLAMP_SW

TRAY_SW

TRCLOSE_SW

TROPEN_SW

N_RST

CD_RST

DPWR_ON

SW_CD_OTHER

SSP2_N_IC

TRAY_SW

TRCLOSE_SW

EX_N_CS

UNCLAMP_SW

TROPEN_SW

EX_N_IC

REM

LED_PWR

KEY0

KEY1

KEY2

TRAY_MTR1

TRAY_MTR2

CLAMP_MTR2

CLAMP_MTR1

I2SSEL_DSDPCM

I2SSEL_DSDPCM

SEL_DIR_BYPASS

SSP2_YOSI

RY_AUDIO

EX_N_IC

SEL_DIR_BYPASS

SYS_TXD

SYS_RXD

DAC_N_RST

DAC_SCL

DAC_SDA

EX_N_CS

CD_YIVO

PULSE_DET

MTR_CTL_DA

CD_PWR_DET

CD_PWR_DET

SYS_RXD

SYS_TXD

REM_REAR

SSP2_N_YOSI_IRQ

SSP2_YISO

SSP2_N_YISO_IRQ

REM_REAR

SSP2_YISO

SSP2_N_YOSI_IRQ

SSP2_N_YISO_IRQ

SSP2_YOSI

SSP2_PON

SSP2_N_IC

SSP2_YISO_MUTE

SSP2_N_DSPSTOP

SSP2_DSD_PCM

SSP2_USB_RDY

SSP2_YOSI_MUTE

SSP2_YOSI_MUTE

FPGA_DSDMUTE

FPGA_DOP_DSDPCM

FPGA_DOP_DSDRATE

FPGA_SELA

FPGA_SELB

FPGA_SELC

FPGA_PROG

FPGA_DONE

FPGA_INITN

FPGA_INITN

FPGA_DONE

FPGA_RRESET

FPGA_SELC

FPGA_SELB

FPGA_SELA

FPGA_DSDMUTE

FPGA_DOP_DSDRATE

FPGA_DOP_DSDPCM

FPGA_PROG

FPGA_IO2

FPGA_IO1

FPGA_IO0

FPGA_RRESET

FPGA_IO2

FPGA_IO1

FPGA_IO0

FPGA_JTAGEN

FPGA_JTAGEN

A_MUTE

WR_CK

N_RST

CNVSS

WR_MOSI

WR_BUSY

WR_MISO

UNCLAMP_SW

SW_CD_OTHER

DPWR_ON

PRVR

PRVL

A_MUTE

DAC_A_MUTE

DAC_A_MUTE

CD_SPDIF_RQ

CD_MUTE

CD_RST

CD_PWR

TROPEN_SW

CLAMP_SW

R507

470

100R475

R486

100

R501

100

R483

100

C439 0.1/16

R434

100

R428

no_use

R471

0

100R477

R508

470

R510

470

470R464

R520 10K

C433 0.1/16

C435 0.1/16

100R479

10KR476

R462

100

R509

470

150K

R439

R473

no_use

R499

100

R454

100

R432

100

R518 10K

R470

100

R465

100

R517 10K

C434

0.1/16

R453 100

R481

100

R504

100

R500

100

R482

100

100R451

C460

10/50

s402

100R437

R506

100

R433

100

R484

100

100R424

C436 10P(CH)

R519

10K

R456

100

100

R455

R449 100

R516 47K

R505

100

R418

100

R452

100

R442

100K

R495

100

C438 0.1/16

R457

100

R459

100

R461

100

R466

100

R468

100

R472

100

R419100

R431

10K

R430

10K

R429

10K

R427

no_use

R426

no_use

C444

4.7/6.3

C448

1/25

R576

47K

C495

0.1/16

C493

100/16

D415

UDZV5.1B

R570

47K

R571 47K

C494

100/16

R569 47K

C496

0.1/16

CB401

no_use

1

2

3

4

5

R537

33

C481 0.01(B)

R538

33

C471 0.01(B)

R539

33

C490

0.01(B)

C437 0.1/16

C473 no_use

C475 no_use

C455 10P(CH)

47KR511

R492

100

R494

100

R440

4.7K

R441

no_use

R420

100

R423100

R422

100

R421

100

SSP2_N_YISO_IRQ

SSP2_N_YOSI_IRQ

SSP2_YISO_MUTE

DIR_N_INT

DIR_MISO

DIR_MOSI

DIR_SCK

DIR_N_RST

DIR_N_CS

R480

100

R445

47K

R438

100K

R444

100K

C484

1/50

R447

100K

R528

1M

C452

10/50

R591

1.0

C449

0.1/16

R458

100

R502

100

R503

100

R583

1.0

C476

3.3/50

C477

3.3/50

R557

470

R558

470

+12RY

-12RY

CB402

29FMN-BTK-A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

RY_GND

V+

8

V-

4

IC407

3

2

1

IC407

NE5532DR

X5482A0

5

6

7

V+

8

V-

4

IC405

NE5532DR

X5482A0

5

6

7

IC405

3

2

1

RY_GND

RY_GND

R534

1K

R536

10K

R535

10K

+12RY

C446

10/50

C441

0.1/16

C445

0.1/16

RY_GND

C440

0.1/16

C442

0.1/16

RY_GND

RY_GND

+12RY

-12RY

+3.3S

R525

10K

R540

33

D414

1SS355VM

R588

1P10

RY_GND

DAC_N_RST

DAC_SDA

DAC_SCL

RY_AUDIO2

L401

BLM18PG471SN1D

L402

BLM18PG471SN1D

C402

100/16

C408

100/16

C404

0.01(B)

C411

0.01(B)

R406

47

Q402

C2412K(Q/R/S)

D401

1SS355VM

D402

1SS355VM

R402

1K

R413

no_use

R412

no_use

+3.3S

PI_SPDIF

R401

10

R514 47K

R513 47K

R443 47K

PRVR

PRVL

R460

100

R469

100

Q401

C2412K(Q/R/S)

R409

47K

R410

47K

R411

4.7K

SW_CD_OTHER

G401

D412

1SS355VM

D413

1SS355VM

RY_GND

R522

10K

R523

10K

R533

10K

R527

10K

R521

10K

R524

10K

R403

470

+3.3S

R425

no_use

C426

no_use

D404

no_use

D403

no_use

FG3

IC418 BA6956AN

123456789

IC419 BA6956AN

123456789

C483

1/50

R556

470K

R541

470K

R526

10K

C447

0.1/16

D411

1SS355VM

DPWR_ON

+7MT

+7MT

PHI

1

2

I2SSEL_DSDPCM

SSP2_YISO

SSP2_PON

+7MT

MO_GND

MT_GND

+5MO1

R485

100

R487

100

R760

100

R761

100

R762

100

R763

100

RP130Q331D-TR-F

YC288A0

IC408

4

VDD

2

GND

3

VOUT

1

CE/CE

SEL_DIR_BYPASS

R783

3.3K

R784

3.3K

SN74LVC1G125DCK

IC406

123

45

MT_GND

MT_GND

V+

8

V-

4

IC438

3

2

1

IC438

NE5532DR

X5482A0

5

6

7

R785

10K

R786

10K

RY_GND

R789

1K

RY_GND

C636

0.1/16

C637

0.1/16

RY_GND

+12RY

RY_GND

-12RY

R790

100

R791

no_use

CB405

CB404

52045

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

XL401

20MHZ

R594

2.2

R595

2.2

IC409

BD00GA3WEFJ-E2

1234

5678

C462

1/16

C474

1/16

C457

47/16

47/16

C443

C479

no_use

C491

47/16

R478

100

CB403

52045

1

2

3

4

5

6

7

8

9

PHI

CB406

1

2

3

4

5

6

7

8

9

DGND

+5MO1

MT_GND

RY_GND

+5D

+7MT

-12RY

+12RY

MO_GND

+5MO2

C421

0.01(B)

C419

0.01(B)

C423

0.01(B)

C418

0.1/16

C420

0.1/16

C422

0.1/16

C451

0.1/16

C450

100/16

s401

C463

0.1/16

C464

0.01(B)

C465

0.1/16

C466

0.01(B)

PRVD

FL_PON

SSP2_YOSI

SSP2_N_IC

SSP2_DSD_PCM

SSP2_N_DSPSTOP

FL_PON

PRVD

SSP2_USB_RDY

R792

100

SSP2_YOSI_MUTE

R836

100

R837

100

R838

100

R839

100

R840

100

R841

100

R842

100

R843

100

R844

100

FPGA_RRESET

FPGA_SELC

FPGA_SELB

FPGA_SELA

FPGA_DSDMUTE

FPGA_IO2

FPGA_IO1

FPGA_IO0

FPGA_DOP_DSDPCM

FPGA_DOP_DSDRATE

FPGA_DONE

R845

100

R846

100

R847

100

R848

100

+5MO2

L431

BLM18PG471SN1D

C706

100/16

C707

0.01(B)

FG1

ST401

0J456

0J457

0J458

R872

no_use

C708

no_use

D435 no_use

D436 no_use

FPGA_INITN

FPGA_PROG

R873

100

FPGA_JTAGEN

150601123K3

CB410

12345678910111213141516171819202122

23

A_MUTE

R883

100

+3.3S

R788

18K

R787

18K

+7MT

R885

390

R436

56K

R435

12K

R886

1.8K

CB414

no_use

1

2

12

11

3

4

5

6

7

8

9

10

R887

no_use

C456 10P(CH)

C478 10P(CH)

R404

4.7K

C412 10P(CH)

C413 10P(CH)

C638

10P(CH)

C454 10P(CH)

C472 0.1/16

C453 0.1/16

C487 0.1/16

C482 0.1/16

C461 0.1/16

C486 0.1/16

C469 0.1/16

C459 0.1/16

C485 0.1/16

C458 0.1/16

C480 0.1/16

C4280.1/16

C432

0.1/16

C430

0.1/16

C4290.1/16

C4270.1/16

C431

0.1/16

C406 no_use

C405 0.1/16

C401 0.1/16

C403 0.1/16

C407 0.1/16

C417 0.1/16

C416 0.1/16

R474

47

C470 10P(CH)

R890

100

DAC_A_MUTE

R892

100K

RY_GND

R512

4.7K

R515

4.7K

C714 1000P(B)

C715

1000P(B)

C716

1000P(B)

C718

1000P(B)

C719

1000P(B)

C720

1000P(B)

C721

1000P(B)

C722

1000P(B)

C723

1000P(B)

C724

1000P(B)

C725

1000P(B)

C726

0.01(B)

C727

0.01(B)

MO_GND MO_GND

C728

1000P(B)

C729

1000P(B)

G

2

D6

S

1

UM6K1NTN

Q412

no_use

G

5

D3

S4

R896

no_use

Q413

no_use

R897

no_use

+3.3S

D439

1SS355VM

D440

1SS355VM

0J461

D405

RB520SM-40

D408 RB520SM-40

D406 RB520SM-40

D409

RB520SM-40

D407

RB520SM-40

D410

RB520SM-40

100R414

100R415

FW_WCK

FW_SDO

DGND

D441

1SS355VM

D442

1SS355VM

IC404

R5F364AENFA

YG122A0

1 2 3 4 5 6 7 8 9 10111213141516171819202122232425

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

56575859606162636465666768697071727374757677787980

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

26 27 28 29 30

55 54 53 52 51

CD_PWR_DET

VSS

SYS_RXD

PRVD

CLAMP_SW

TRXD

SSP2_YISO_MUTE

SSP2_N_YISO_IRQ

DAC_SCL

LED_PWR

GND

SSP2_USB_RDY

CD_YOVI

REM

WR_MOSI

CLAMP_MTR1

SSP2_YOSI_MUTE

DPWR_ON

FPGA_PROG

TRCLOSE_SW

DAC_N_RST

NC

LOAD-

DAC_SDA

LOAD+

CD_MUTE

PULSE_DET

N_NMI

CNVSS

AVCC

A_MUTE

SSP2_YOSI

FPGA_INITN

TRAY_SW

PRVR

TCK

FPGA_SELB

DIR_N_INT

PWR_RY

FPGA_SELA

FPGA_RRESET

FPGA_SELC

TRAY_MTR1

N_RST

FPGA_IO1

KEY1

PRVL

SEL_DIR_BYPASS

KEY2

DRI_SCK

BYTE

KEY0

WR_BUSY

SSP2_N_YOSI_IRQ

FL_EX_MOSI

PI_DVDRST

VREF

FL_EX_CLK

SW_CD_OTHER

FPGA_DOP_DSDRATE

FPGA_DSDMUTE

SSP2_YISO

VCC2

FPGA_IO0

VCC1

TRAY_MTR2

DIR_N_CS

WR_CK

-

ACPWR_DET

VSS

:YC806A0

RY_AUDIO

UNCLAMP_SW/N_CE

XIN

FPGA_DONE

DIR_MOSI

FL_N_CS

TMODE

CLAMP_MTR2

FPGA_JTAGEN

XOUT

DIR_MISO

SSP2_N_DSPSTOP

:YC731A0

SSP2_N_IC

AVSS

FPGA_DOP_DSDPCM

to Writer

FLASH U-COM

FLASH U-COM(Writen by YEM)

WR_MISO

N_EMP

SSP2_DSD_PCM

N_RST

DIR_N_RST

TVccd

TTXD

FPGA_IO2

CD_PWR

TROPEN_SW

DAC_A_MUTE

CD_YIVO

REM_REAR

SYS_TXD

MTR_CTL_DA

I2SSEL_DSDPCM

YDC BOOT

STBY_CNT/N_EMP

TROUT_SW

CLAMP_SW

GND

NC

EX_N_CS

EX_N_IC

FL_PON

FL_N_RST

SSP2_PON

NC

CD_SPDIF_RQ

L_MOTOR-

L_MOTOR+

+9SUB

PWR_DET

RY_PWR

MGND

+3.3M

N_RES

TRAY_SW

MGND

LED_POWER

MGND

FL_RESET

+3.3S

EX_N_CS

S2 TRAY OPEN

S4 CLAMP

KEY2

FL_CS

FL_EX_CLK

CLAMP MOTOR+

CLAMP MOTOR-

MGND

S1 TRAY CLOSE

S3 UNCLAMP

KEY0

EX_N_IC

KEY1

IR

FL_EX_DATA

+3.3M

to FRONT(4)

401 900

DIGITAL

CD_PWER_DET

SPDIF_OUT

MO_GND

+5MO2

TROPEN_SW

SPDIF_RQ

CD_YOVI

+7MT

MT_GND

CD_YIVO

CD_MUTE

MO_GND

+5MO2

+7MT

+5MO1

MO_GND

MO_GND

MT_GND

+5MO1

CD_PWR

CLAMP_SW

CD_RST

REM_REAR

SYS_TXD

SYS_RXD

003.sht CB909

(FL)

to Loader Mecha

(SUBTR)

002.sht W903

to FRONT(2)

to FRONT(1)

001.sht CB902

(DIGITAL POWER)

+7MT

+7MT

MT_GND

MT_GND

+5MO1

+5MO1

MO_GND

MO_GND

+5MO2

+5MO2

NC

NC

PRVD

FL_PON

+5D

+5D

+5D

DGND

DGND

DGND

+12RY

-12RY

RY_GND

to Zoran Module

to IC401

003.sht

(SSP2)

002.sht

(DIR)

to IC424

002.sht

(FPGA)

to IC443

002.sht

(PCM/DSD Sel)

002.sht

(DAC)

to CB408

to CB410

001.sht

(DIGITAL POWER)

002.sht

(+5D Control)

001.sht

MO_GND

MO_GND

MO_GND

MO_GND

MO_GND

MO_GND

MO_GND

to IC424

002.sht

(DIR)

Destination Part List

+--------+---------------+---------------+---------------+---------------+---------------+

| sXX | LOC | J | UTKALVS | B | G |

+--------+---------------+---------------+---------------+---------------+---------------+

| s401 | C581 | UR23810 | UR23810 | UU23810 | UU23810 |

| | C450 | 100/16 | 100/16 | 100/16 | 100/16 |

+--------+---------------+---------------+---------------+---------------+---------------+

| s402 | C460 | UU26710 | UU26710 | UU23710 | UU23710 |

| | | 10/50 | 10/50 | 10/16 | 10/16 |

+--------+---------------+---------------+---------------+---------------+---------------+

IC418, 419: BA6956AN

Reversible motor driver

VREF

GND

RIN

FIN

CTRL

TSD

7

9

1

8

OUT1

4

OUT2

RNF

2

3

VCC

6

VM

5

1

2

3

4

8

7

6

5

1OUT

1IN–

1IN+

V

CC–

V

CC+

2OUT

2IN–

2IN+

OUT

V

CC–

V

CC+

36 pF

37 pF

14 pF

7 pF

15

460

15

IN+

IN

IC405, 407, 438: NE5532DR

Dual low-noise operational amplifiers

IC409: BD00GA3WEFJ-E2

300 mA variable output LDO regulator

–

+

+

GND

EN

FB

Vo

Vcc

SOFT

START

TSD

OCP

3

5

2

1

8

IC404: R5F364AENFA

Single chip 16-bit microprocessor

Timer (16-bit)

Internal peripheral functions

Inputs (timer B): 6

Three-phase motor control circuit

Outputs (timer A): 5

Watchdog timer

(15-bit)

Remote control signal

receiver

(2 circuits)

PWM function (8-bit x 2)

CEC function

Real-time clock

VCC1 ports

VCC2 ports

A/D converter

(10-bit resolution X 26 channels)

System clock generator

PLL frequency synthesizer

On-chip oscillator (125 kHz)

X

IN-XOUT

XCIN-XCOUT

Port P0

8

Port P1

8

Port P1

8

Port P3

8

Port P4

8

Port P5

8

Port P10

8

Port P9

8

Port P8

8

Port P7

8

Port P6

8

ISP

USP

INTB

SB

CRC arithmetic circuit

(CRC-CCITT or CRC-16)

DMAC (4 channels)

Voltage detecter

On-chip debugger

Power-on reset

Multiplier

Memory

ROM

RAM

FB

A1

FLG

PC

UART or

clock synchronous serial I/O

Clock synchronous serial I/O

Multi-master I

2

C-bus interface

(6 channels)

(8 bit x 2 channels)

(1 channel)

D/A converter

(8-bit resolution X 2 circuits)

M16C/60 series

Microprocessor core

R0LR0H

R1H R1L

R2

R3

FB

A1

A0

IC406: SN74LVC1G125DCKR

Single bus buffer gate

1

2

3

OE

A

GND 4

5 VCC

Y

VDD

CE

Vref

43

12

Current Limit

VOUT

GND

Pin No.

1

2

3

4

Symbol

V

OUT

GND

CE

V

DD

Description

Output Pin

Ground Pin

Chip Enable ("H" Active)

Input Pin

IC408: RP130Q331D-TR-F

Voltage regulator

to DIGITAL 2/3

to DIGITAL 2/3

to DIGITAL 2/3

to DIGITAL 2/3

to DIGITAL 3/3

MICROPROCESSOR

to Loader mechanism unit

to Module board_CN211

Writing port

to DIGITAL 1/3

to DIGITAL 2/3

Details of colored lines

Red / full line: Power supply (+)

Red /dashed line: Power supply (-)

Orange: Signal detect

Yellow: Clock

Green: Protection detect

Brown: Reset signal

Blue: Panel key input

to FRONT (1)_CB902

Page 66

K5

to FRONT (2)_W903

Page 67

K6

to FRONT (3)_CB910

Page 68

B4

Loading...

Loading...