— 22 —

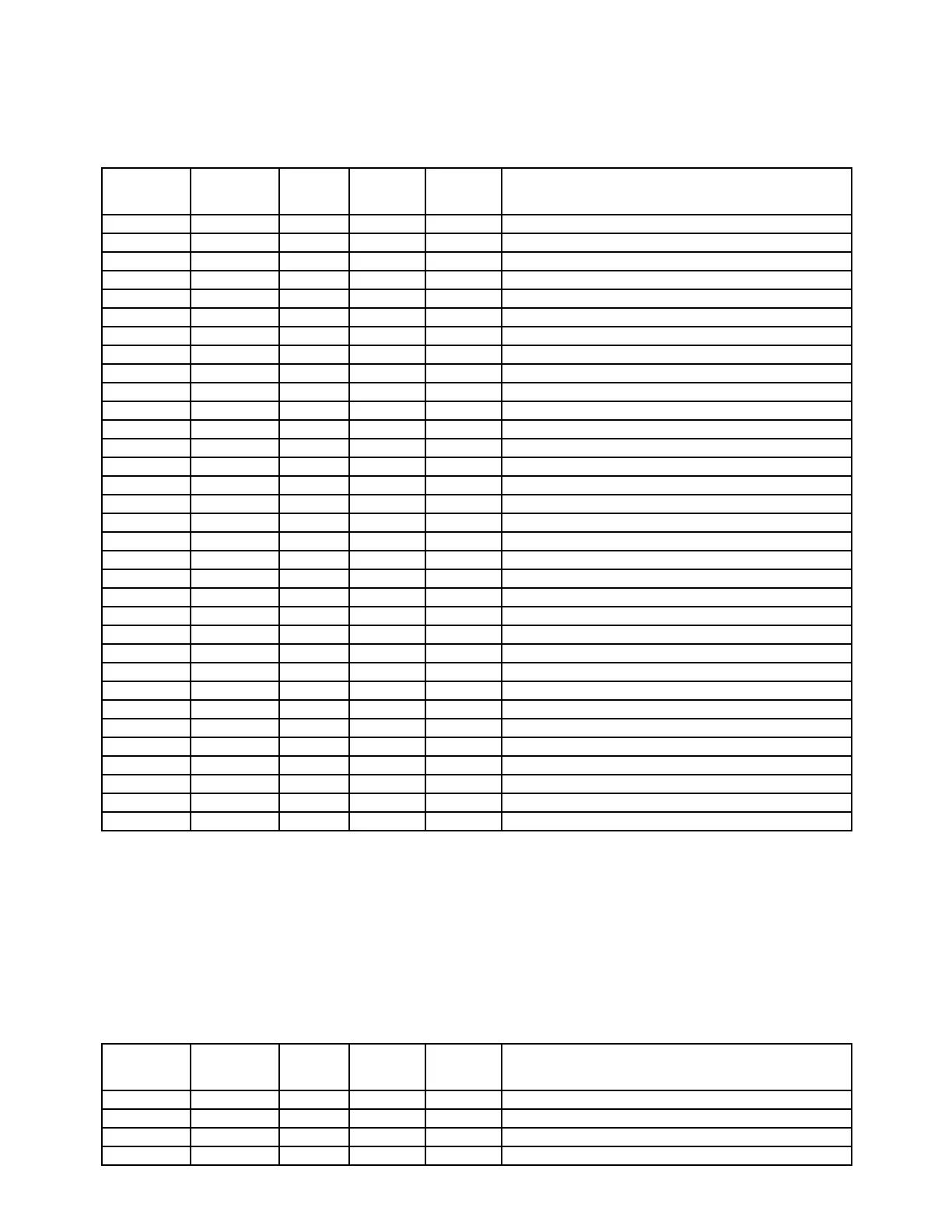

10-4. Gate array pin descriptions (µPD65005GC-566-3B6)

Pin No. Name In/Out Status Status Description

of OFF of ON

32, 22 GND1, 2 In L L GND terminal

1, 19 VDD1, 2 In H H Main battery positive terminal (+5V)

2 Vo1 Out H H VDD output terminal (4.5V)

31 PDB In L H Power on switch signal from gate array

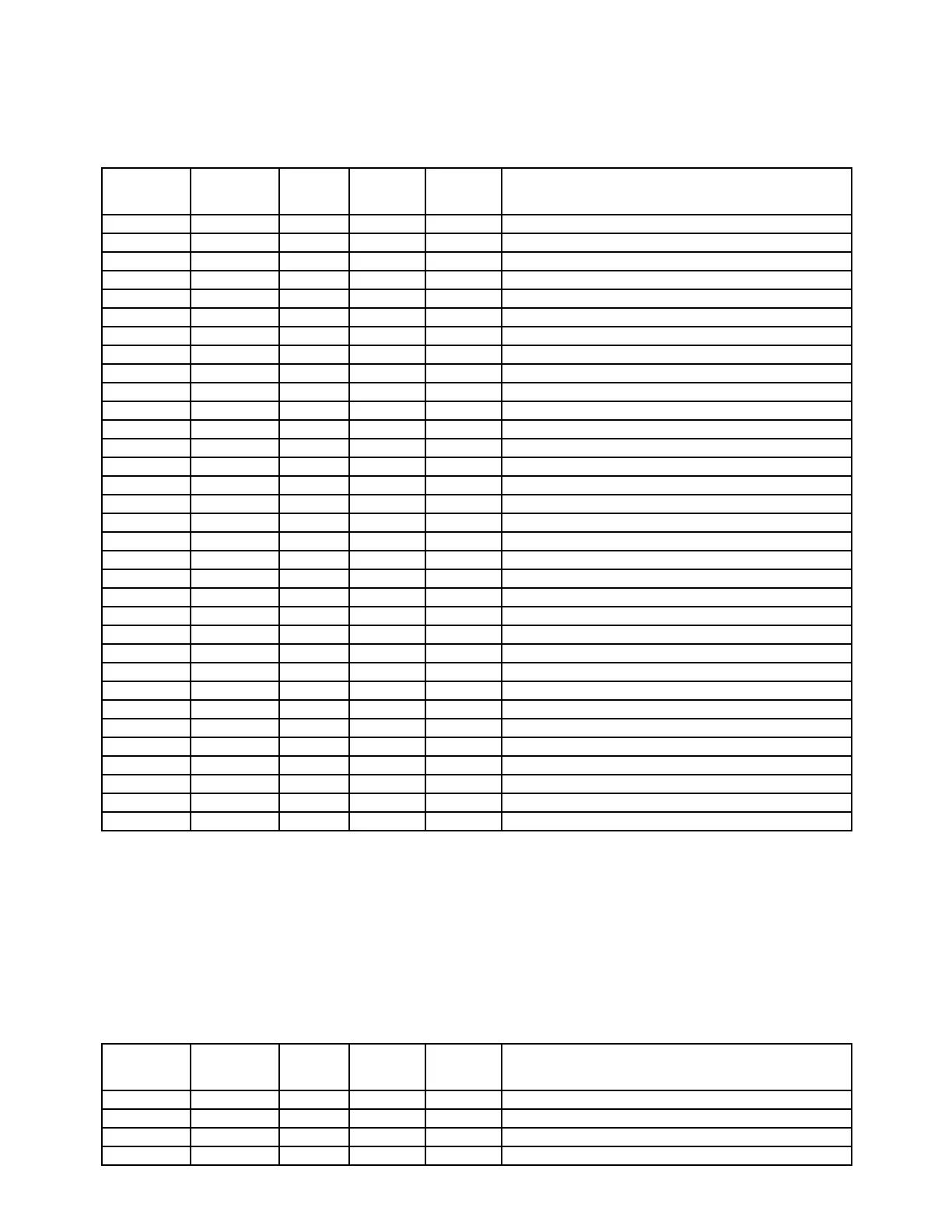

10-5. Power supply chip IC pin descriptions (SC371015FU)

Pin No. Name In/Out Status Status Description

of OFF of ON

1~6, 8, 9 OI7~OI0 In/Out L L Not used

7, 33 GND In L L GND terminal

10 B15 In L Pulse Address input

11~13 A15,A01,A00 In L Pulse Address input

14 N.C. - - - Not used

15 DT In H Pulse GC signal input

16~23 IO0~IO7 In/Out L Pulse Data bus line

24 CSB In H Pulse Chip select signal from CPU

25 MON Out L L Not used

26 LSI In L L Connected to GND

27 LSO Out H H Always "H"

28 PDN In H H Power down detection input

29 BLI In H H Battery detection V comp1 input

30 DEB Out H Pulse Chip selection signal for ROM (Charactor generator)

31 VIN In L H Power on signal input

32 VOT Out L H Power on signal output

34 VDD In H H VDD terminal

35 OEI In H Pulse Read signal input

36 WEI In H Pulse Write signal input

37 BBC Out L Pulse Memory back-up battery scanning signal

38 CDE In L H IC card detection signal input

39 VOB Out H L ROM power switching signal (Operation program)

40 SWO Out L L Main switch control signal

41 BCN In H H BCON signal from CPU

42 MDP In H L MDP2 signal from CPU

43 OEO Out L Pulse Read signal for ROM

44 WEO Out L Pulse Not used

45, 51 A19, A16 In L Pulse Address input

46, 47 R15, R16 Out L Pulse Address output

48 EOB In H Pulse Chip enable signal from CPU

49 RS0 Out H Pulse Chip enable signal for ROM (µPD27C4001EBGW-304)

50 CS3 In H Pulse Chip select signal from CPU

52 RS3 Out H Pulse Chip enable signal for ROM (Character generator)

Loading...

Loading...