— 21 —

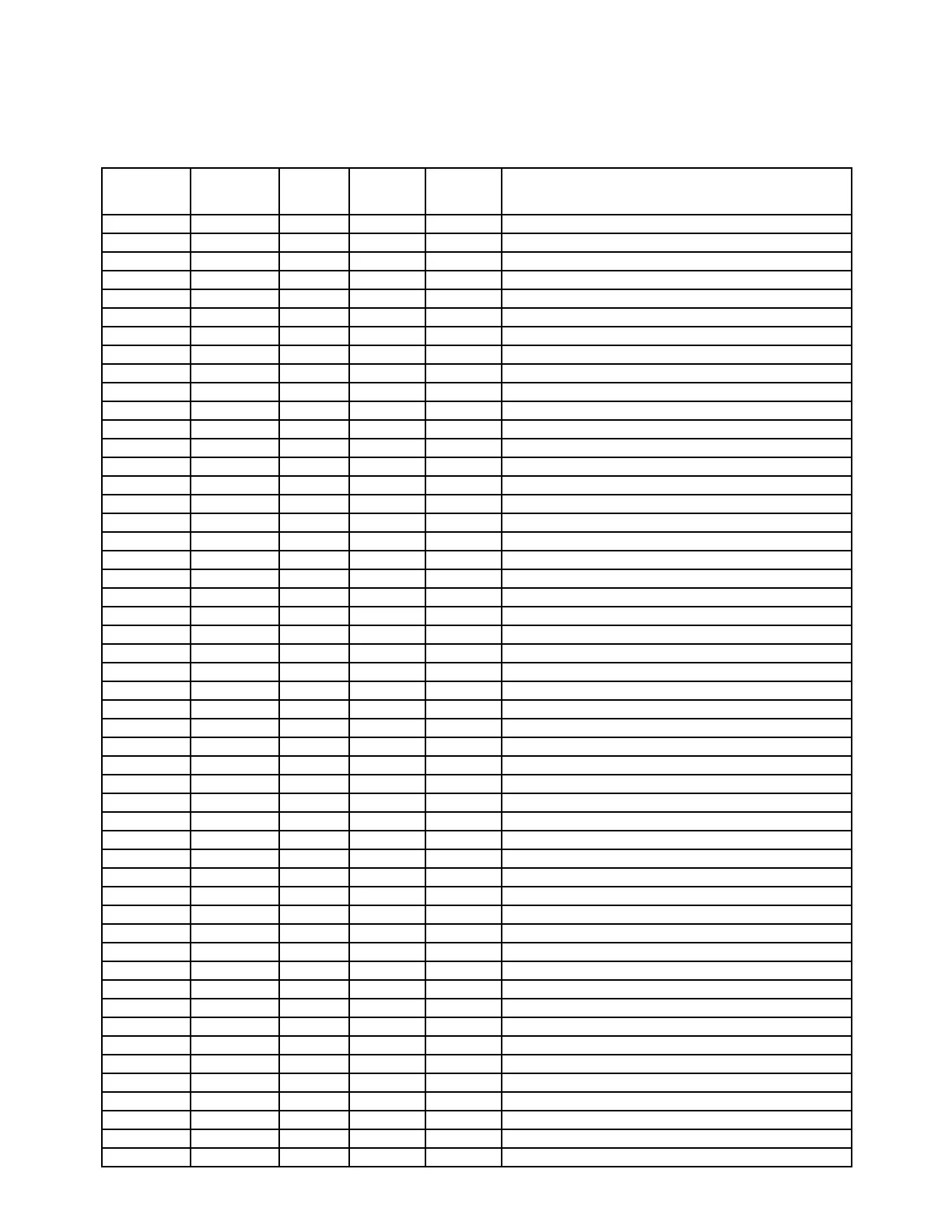

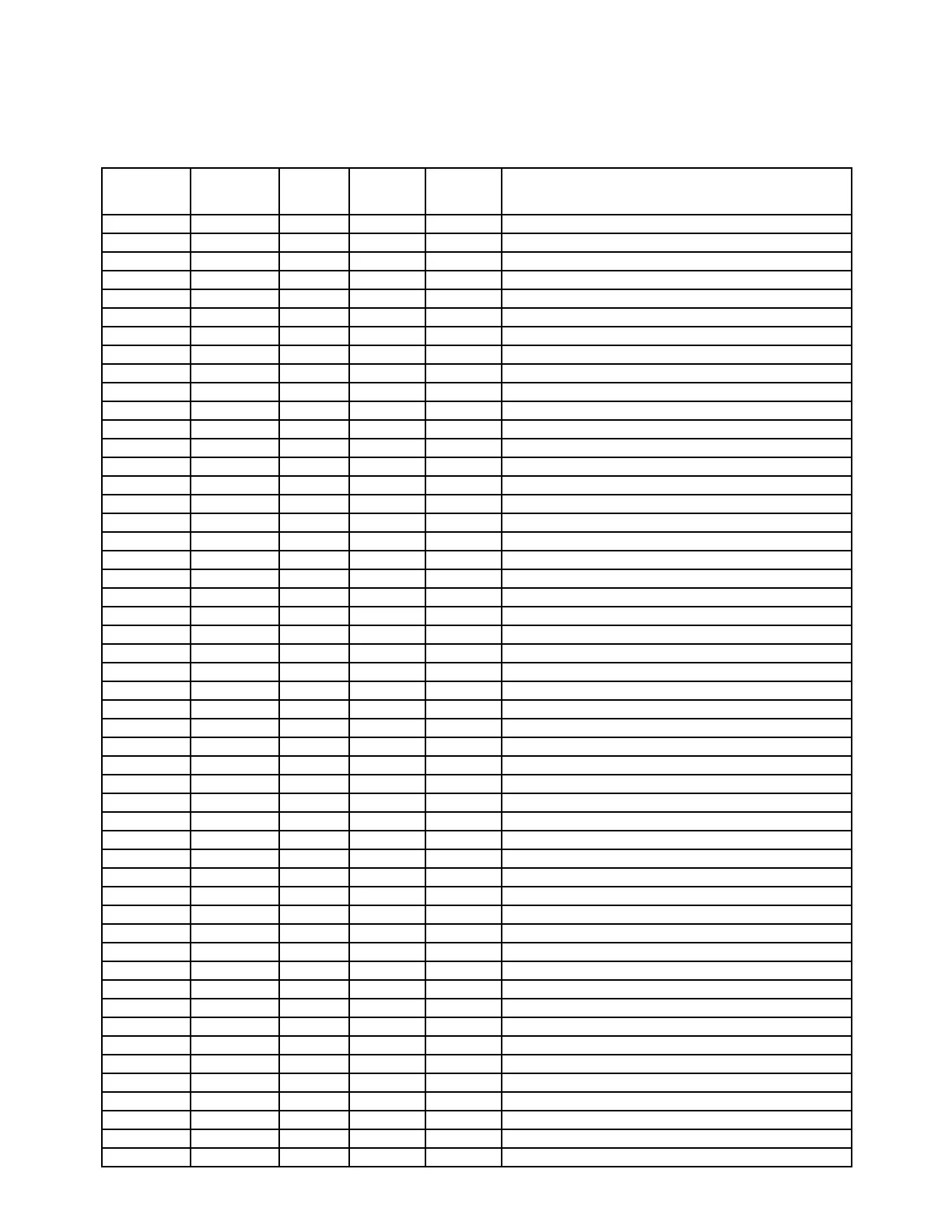

10-3. CPU pin description (HD62076C02)

Pin No. Name In/Out Status Status Description

of OFF of ON

1~14,16,17 A0~A15 Out L Pulse Address Bus line

15,39, 100 VSS In GND GND GND terminal

24 WE Out H Pulse Write signal

25 OE Out H Pulse Read signal

26 FE Out H Pulse Not used

27 CS1 Out H H Not used

28 CS2 Out H H Chip select signal for gate array

29 CS3 Out H Pulse Chip select signal for ROM (Charactor generator)

30 E0 Out L Pulse Chip enable signal for ROM (Operation program)

31 E1 Out L H Chip enable signal (Not used)

32 E2 Out L H Chip enable signal (Not used)

33 E3 Out L H Chip enable signal (Not used)

34 BCON Out H H BCN signal to gate array

35 MDP2 Out H L MDP signal to gate array

36 SW In L L Switch signal (When switches are at ON position)

37 ONMK In H H Battery detection V comp1 input

38 TEST In L L TEST terminal (connect to GND)

40,41 OSC O/I In L Pulse Clock input

42 VOSC In L H Power input for Clock

43, 91 VDD1 In H H VDD input terminal

44 VDD2 In H H VDD input terminal

45 V2ON Out L H Power on output signal

46~53 KI7~KI0 In H H Key input signal (K17…Not used)

54 KAC Out L Pulse Power on switch signal output

55~65,67 KC0~KC11 Out H Pulse Key common signal output

66 GND In L L GND terminal

68 INT2 In H H Interrupt signal from ROM (Charactor generator)

69 INT1 In L H Interrupt signal for transmission

70 INT0 In H H Interrupt signal for transmission

71 BRK In H H VDD input terminal

72 P0 Out H H Transmission data output

73 P1 In L H Reception data input

74 P2 In H H Card lock switch input

75 P3 In L H IC card detection signal input

76 P4 Out H Pulse KC 12 key common signal output

77 P5 Out H Pulse KC 13 key common signal output

78 P6 In H H Memory back-up battery detection input

79 P7 In H H Battery detection V comp2 input

80 H1 Out H H Display contrast control signal output (Up/Down)

81 WENL In L L GND terminal

82 H2 Out H H Not used

83 L1 Out L H Chip enable signal for gate array

84 L2 Out L L Dispray contrast control clock signal

85 DT Out H Pulse Not used

86 PRO Out L H LCD driver mode selection signal

87 FR Out L Pulse LCD driver synchronous signal

88 LP Out H Pulse LCD driver latch pulse signal

89 GC Out H Pulse GC signal output

90 DE Out H Pulse LCD driver data latch clock signal

92~99 IO7~IO0 In/Out L Pulse Data bus line

18~23 RA14~19 Out L Pulse Address line (Used exept RA 14)

Loading...

Loading...