H_D#[63:0]4

H_ S MI#

H_ D# 3 8

H_ P W RG D

H_ F E R R#

H _D#[63:0] 4

COMP0

H_ TM S

H_ D# 1 9

H_ D# 1 8

Z0214

H_ADS TB#04

COM P1

H_ T DO

R 1 22 56 _ 0 4

H _ DINV #3 4

COMP3

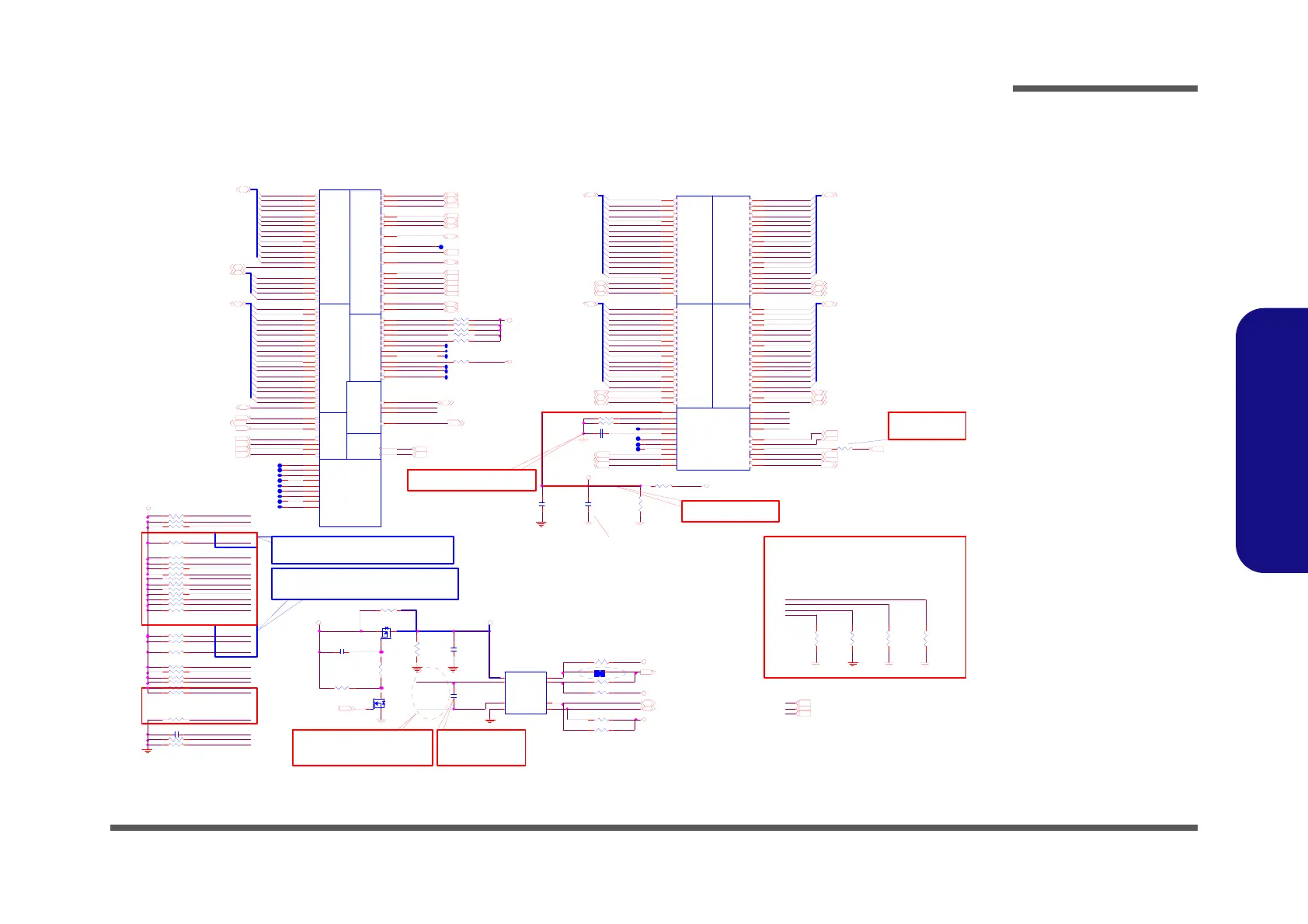

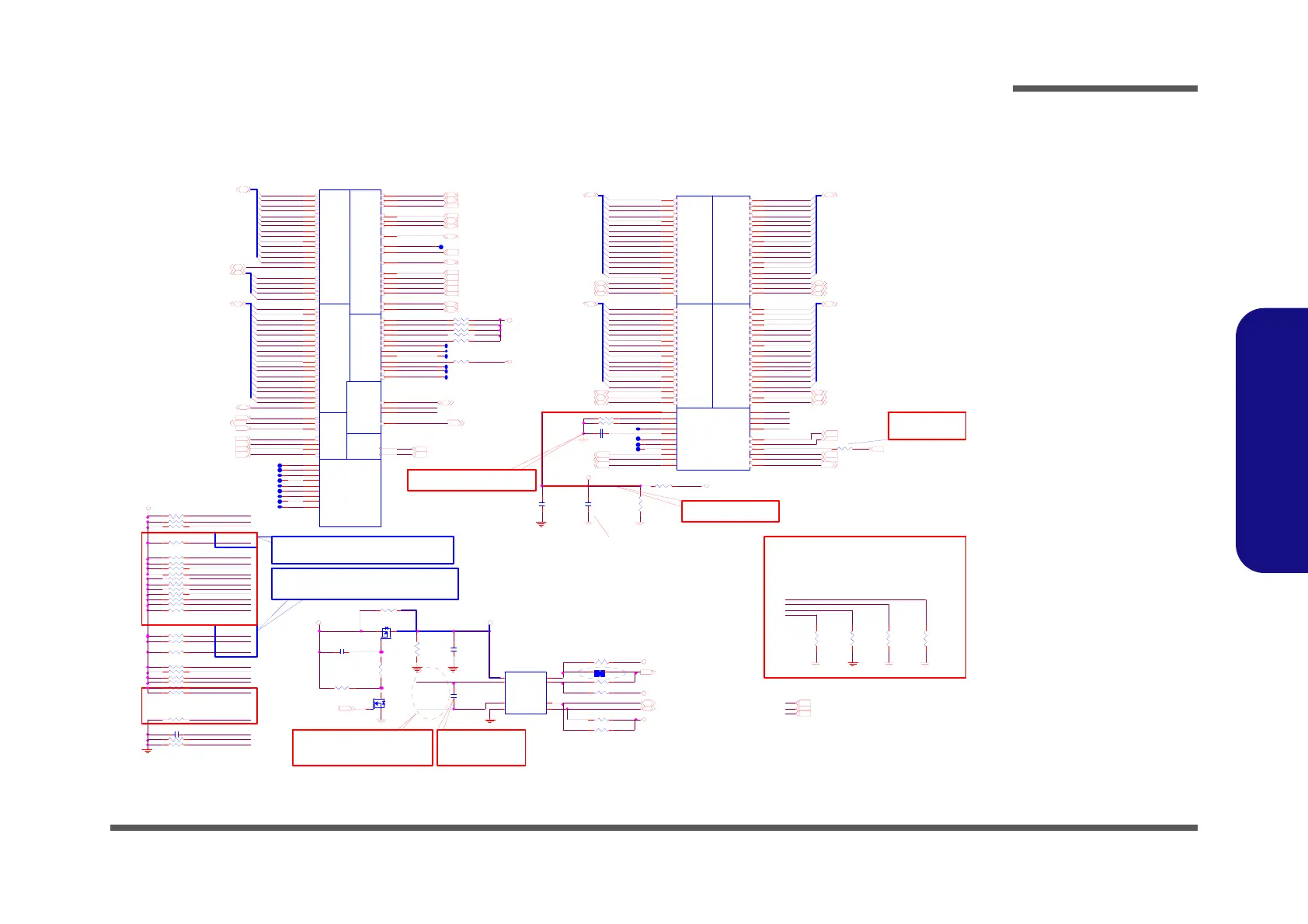

U7

ASC 75 2 5

1

2

3

4

5

6

7

8

VD D

D+

D-

TH ERM

GND

ALERT

SD ATA

SC LK

C 1 54 1 0 0P _5 0 V _ 04

Layout Note:

H _STPC LK #22

H_ D# 3 5

CPU_BSEL 1

R151

*330K_04

H_ D# 2 7

H_ D# 1 0

H_ D# 6

H_ TH RM TR IP #

H_A#33

R 101 51_1%_04

R449

27.4_1% _04

H_DSTBN#2 4

H_PREQ #

R1 55 *0_ 0 4

R 1 31 56 _ 0 4

H _ DINV #2 4

H_ A # 9

DATA GRP 0

DATA GRP 1

DATA GRP 2DATA GRP 3

MISC

JSKT1B

Pen ryn

R26

U26

AA1

Y1

E22

F24

J24

J23

H2 2

F26

K22

H2 3

N2 2

K25

P26

R2 3

E26

L23

M2 4

L22

M2 3

P25

P23

P22

T24

R2 4

L25

G2 2

T25

N2 5

Y22

AB24

V24

V26

V23

T22

U25

U23

F23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

AE24

AD 24

G2 5

AA21

AB22

AB21

AC 26

AD 20

AE22

AF2 3

AC 25

AE21

AD 21

E25

AC 22

AD 23

AF2 2

AC 23

E23

K24

G2 4

AF1

H2 5

N2 4

U22

AC 20

E5

B5

D24

J26

L26

Y26

AE25

H2 6

M2 6

AA26

AF2 4

AD26

AE6

D6

D7

C2 4

B22

B23

C2 1

D2 5

AF2 6

A26

C2 3

C3

CO MP[0 ]

CO MP[1 ]

CO MP[2 ]

CO MP[3 ]

D[0 ]#

D[1 ]#

D[1 0 ]#

D[1 1 ]#

D[1 2 ]#

D[1 3 ]#

D[1 4 ]#

D[1 5 ]#

D[1 6 ]#

D[1 7 ]#

D[1 8 ]#

D[1 9 ]#

D[2 ]#

D[2 0 ]#

D[2 1 ]#

D[2 2 ]#

D[2 3 ]#

D[2 4 ]#

D[2 5 ]#

D[2 6 ]#

D[2 7 ]#

D[2 8 ]#

D[2 9 ]#

D[3 ]#

D[3 0 ]#

D[3 1 ]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[4 ]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[5 ]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[6 ]#

D[60]#

D[61]#

D[62]#

D[63]#

D[7 ]#

D[8 ]#

D[9 ]#

TEST5

DIN V[0 ]#

DIN V[1 ]#

D INV[2 ]#

D INV[3 ]#

DPRSTP#

DPSLP#

DPWR#

DST B N [0]#

DST B N [1]#

DST B N[2 ]#

DST B N[3 ]#

DSTBP[0]#

DSTBP[1]#

DSTBP[2]#

DSTBP[3]#

GT L REF

PSI#

PW RG OOD

SLP#

TEST3

BSEL [0]

BSEL [1]

BSEL [2]

TEST2

TEST4

TEST6

TEST1

TEST7

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil spacing.

V_TH ERM

R142 0_06

Close to Thermal IC

3.3V 12,19,20,22,23,24,26,31,32,33,38,39,40

H_A#29

C5 52

.01U_16V_X7R_04

C686 Close to TEST4 (Pin AF26)

H_ DP W R #_ RH_ NM I

H_ DIN V # 04

H_ D# 5 6

H_ IE R R#

H_A#11

R156 *10K_04

H_A#31

Z0201

H_ T HE R MD A

R 88 56_1%_04

H_ D E F ER# 4

H_ D# 1 1

H_ D# 3 0

R1 2 6 * 1 K _0 4

R 1 57 4 . 7K _0 4

ADM1032 1000p

F75383M 2200p

H_DPRS TP# 6,37

H_ B N R# 4

H_ D# 5

Layout Note:

H_ H IT# 4

H_ IGN NE#22

H_ D# 5 4

H_ D# 4

H_ T DI

H_ B R 0#

Z0223

H_A#21

1.05VS 3,4,6,7,24,39

H_ NM I22

H_ D #1 4

IF US ED D esk to p CPU , H_ CPU RS T# ,H_ PW RG D, H_B RD ,n eed

ad d p ul l hig h re sis to r

H_ H ITM # 4

R 1 18 10 _ 0 4

H_ DS T BP# 14

H_PROCHOT# 22

H_ NM I

H_ D# 2 0

H_REQ#4

H_ IE RR #

H_ INT R

R 1 32 56 _ 0 4

H_CLK_CPU 25

THER M_ AL ERT# 27

H_ T MS

Z0212

H_ P W RG D

H_A#17

R 1 17 56 _ 0 4

H_ T RD Y# 4

H_INTR22

Z0204

Q1 0

*2N7002W

G

DS

H_ DP W R # 4

H_SMI#22

H_ D# 2 9

CPU_BSEL 0

H_ D# 2 6

H_A#22

H_A#32

Thermal IC

H_ D# 7

H_ D# 2 1

COM P0

H_D#[63:0]4

H_ DP W R # _R

H_A#25

C180

* .01U _ 16 V_ X7R _0 4

H_ D S TB N# 14

H_CLK_CPU# 25

H_ R S #0 4

C PU_BSEL1

H_THERMDA

H_ S M I#

R 1 15 56 _ 0 4

SMC _CPU_THER M 27

H_REQ#2

R 92 51_1%_04

H _ DSTBP# 2 4

H_ D# 1 5

H_A#10

CP U_BSEL225

H_ R S #1 4

H_ D# 4 7

H_DPSLP#

H_ D# 1 7

H_ T RST#

H_ D# 5 7

C PU_BSEL0

H_ P R DY #

H_ D S TB N# 04

H_CPUS LP# 22

H_REQ#1

H_ P R OC HOT#

( Si S Re co mma nd at ion 2 00 p)

H_ D# 1

H_A#28

Z0216

H_ INT R

R4 4 1

54.9_1%_04

VDD 3

H_ D# 1 2

H_ IN IT#

R 1 50 1K _0 4

1.05VS

H_DSTBN#3 4

H_AD S# 4

R 1 30 56 _ 0 4

CPU_GRFE=0.7V

H_ B R 0# 4

H_ D# 3

H_ B R0 #

H_ INIT #

H_ DP W R # _R

R 89 56_04

R152

*1 00 K_ 0 4

Layout Note:

H _AD STB#14

H_PWRGD 4

H_A#35

R 4 60 1K _0 4

H_ D# 4 4

COM P3

R 1 25 56 _ 0 4

R 1 14 56 _ 0 4

H_ D# 5 0

H_STPCLK#

H_ TC K

R1 3 5

*100K_04

R 4 59 1K _0 4

H_ D# 5 9

H_ P W RG D

R120 *0_04

PS I# 3 7

H_A#[35:3]4

H_A#15

R 106 *51_04

H_ D# 2 8

C163

.1U_10V_X7R_04

R 1 27 56 _ 0 4

Layout note:

R 1 13 56 _ 0 4

H_A20M#22

H_ D# 3 2

C554 * .1U_10V_X7R_04

R 116 *330_04

H_ D# 2

H_ A # 8

H_A#19

R406

2K_1%_04

H_ D# 4 8

H_A#18

COMP1

H_A#14

CP U_BSEL125

56_04

H_ D# 8

R74

54.9_1% _04

C164

1000P_50V _04

1. 05 V S

H_ D# 2 5

H_ D# 3 4

H_A#12

H_A#27

H_DPSLP#

1. 0 5 V S

H_ D# 0

H_ C P UR ST#

Z0208

H_ CP U SLP #

Q9

* NDS 35 2 AP_ NL

G

DS

H_THR MTRIP #

Z0226

H_A#30

H_REQ#0

Z0209

H_ CP U SLP #

Z0215

H_ P R EQ#

R 1 48 15 0 _ 1% _ 0 4

6-14-5603B-11B

CPU_GTLREF

H_A#[35:3]4

SMD _CPU_THER M 27

R 58 39.2_1% _04

C PU_BSEL2

H_ D# 4 9

H_ B PM 1 #

Z0203

H_ D RDY # 4

H_ D# 4 3

R 65 27.4_1% _04

R 1 47 56 _ 0 4

ADDR

GROUP_0

ADDR

GROUP_1

CONTROL

XDP/ITP SIGNALS

H C LK

THERMAL

RESERVED

ICH

JSKT1 A

Penry n

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

D2

D22

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD4

AD3

AD1

AC4

G5

F1

C2 0

E1

H5

F21

A5

G6

E4

D2 0

C4

B3

C6

B4

H4

AC2

AC1

D2 1

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC5

AA6

AB3

C7

A24

B25

AB5

G2

AB6

W3

AA4

AB2

AA3

F6

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[3]#

A[30]#

A[31]#

R SVD[01 ]

R SVD[02 ]

R SVD[03 ]

R SVD[04 ]

R SVD[05 ]

R SVD[06 ]

R SVD[07 ]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

AD S#

AD STB[0]#

AD STB[1]#

R SVD[08 ]

BC L K[0]

BC L K[1]

BNR #

BPM [0 ]#

BPM [1 ]#

BPM [2 ]#

BPM [3 ]#

BPR I#

BR0#

DBR #

DBSY #

DEF E R #

DR DY #

FER R#

HIT#

HI TM #

IERR #

IG NN E#

IN IT #

LINT0

LINT1

LOC K#

PR DY #

PREQ #

PRO CH OT#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

R ESET#

R S[0 ]#

R S[1 ]#

R S[2 ]#

SM I#

STPC LK#

TCK

TDI

TDO

THE RMTR IP#

THERM DA

TH ERM DC

TMS

TR D Y #

TR S T #

A[32]#

A[33]#

A[34]#

A[35]#

R SVD[09 ]

H_ TR S T #

H_ D# 3 7

R 66 51_1%_04

H_ P RO CH OT#

Z0210

H_ B PM 3 #

H_ F E RR #

R 1 49 68 _ 0 4

R 108 *51_04

H_ D# 6 3

H_ D# 4 1

H_ D# 5 1

Z0213

H_ DS T BP# 04

VD D3 20,23,27,34,35,36,38,40

H_ D# 4 5

R4 5 8 * 1 K _0 4

1.05VS

H_ D# 3 3

H_ A # 4

H_ D# 4 2

H _ DPSLP# 6

Z0211

H_ D# 6 0

H_A#13

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms(20mil)

COMP1, COMP3: 0.5" Max, Zo=55 Ohms(5mil)

Best estimate is 18 mils wide trace for outer

layers and 14 mils wide trace if on internal

layers.

H_ IGN NE#

R 1 58 4 . 7K _0 4

3.3V

H_THERMDC

H_A#16

H_A#23

R 80 54.9_1% _04

THER M_RST#27

H_ TD I

H _ DSTBP# 3 4

H_ A 2 0M #

VDD 3

H_BPR I# 4

H_ D# 6 2

H_ D# 1 3

H_STPCLK#

H_ T CK

H_REQ#3

R 1 34 56 _ 0 4

0.5" max, Zo= 55 Ohms

H_ DIN V # 14

H_D BSY# 4

H_ B PM 2 #

H_ B PM 0 #

H_A#20

R 119 *56_04

CPU to SB interface

H _D#[63:0] 4

H_ IGN NE#

COM P2

H_ CP U RST #

H_ A # 7

H_ DB R #

H_ D# 5 3

Z0205

CP U_BSEL025

H_ D# 6 1

H_A20M#

H_ R S #2 4

COMP2

CPU_BSEL 2

Z0225

Layout Note:

H_ D# 5 8

H_ D# 3 9

H_ D# 9

H_A#34

R1 38 1 0K _ 04

H _ TH R M TR I P # 22

If PR OC HO T# is r out ed b etw ee n CPU , IM VP an d MC H,

pu ll- up r esi st or ha s to be 6 8 ohm ? 5 %. If n ot

us e, pu ll -up r es ist or h as to b e 5 6 oh m ? 5 %

If u se d M6 72

th an d el R 3

H_ D# 3 1

H_ A # 6

H_ C P URS T# 4

H_ F E RR #22

H_ D# 4 6

H_ D# 5 2

H_ A # 5

H_ D# 4 0

H_ D# 5 5

R 407 1K_1% _04

H_ L OC K# 4

H_ D# 1 6

Z0202

Z0224

H_ A # 3

H_A#26

R8 5

27.4_1%_04

H _ RE Q# [4 :0]4

H_ D B R#

I f us ed M6 72 th an

d el R 40 an d add R 42

H_ D# 2 2

H_ D# 2 4

R 100 51_1%_04

H_ IN IT# 2 2

PSI#

H_ T HE R MD C

20MIL

H_ D# 3 6

Z0206

Z0207

H_A#24

C553

1U_6.3V_X5R_06

R 57 680_04

V_THERM

R 1 37 * 1 0m i l_ s h or t

H_ D# 2 3

R 73 150_1% _04

Loading...

Loading...